## **DATA SHEET**

OKI

# MSM7630

**Universal Speech Processor**

**SECOND EDITION**

**ISSUE DATE: JAN. 1999**

#### NOTICE

- 1. The information contained herein can change without notice owing to product and/or technical improvements. Before using the product, please make sure that the information being referred to is up-to-date.

- 2. The outline of action and examples for application circuits described herein have been chosen as an explanation for the standard action and performance of the product. When planning to use the product, please ensure that the external conditions are reflected in the actual circuit, assembly, and program designs.

- 3. When designing your product, please use our product below the specified maximum ratings and within the specified operating ranges including, but not limited to, operating voltage, power dissipation, and operating temperature.

- 4. Oki assumes no responsibility or liability whatsoever for any failure or unusual or unexpected operation resulting from misuse, neglect, improper installation, repair, alteration or accident, improper handling, or unusual physical or electrical stress including, but not limited to, exposure to parameters beyond the specified maximum ratings or operation outside the specified operating range.

- 5. Neither indemnity against nor license of a third party's industrial and intellectual property right, etc. is granted by us in connection with the use of the product and/or the information and drawings contained herein. No responsibility is assumed by us for any infringement of a third party's right which may result from the use thereof.

- 6. The products listed in this document are intended for use in general electronics equipment for commercial applications (e.g., office automation, communication equipment, measurement equipment, consumer electronics, etc.). These products are not authorized for use in any system or application that requires special or enhanced quality and reliability characteristics nor in any system or application where the failure of such system or application may result in the loss or damage of property, or death or injury to humans. Such applications include, but are not limited to, traffic and automotive equipment, safety devices, aerospace equipment, nuclear power control, medical equipment, and life-support systems.

- 7. Certain products in this document may need government approval before they can be exported to particular countries. The purchaser assumes the responsibility of determining the legality of export of these products and will take appropriate and necessary steps at their own expense for these.

- 8. No part of the contents cotained herein may be reprinted or reproduced without our prior permission.

- 9. MS-DOS is a registered trademark of Microsoft Corporation.

Copyright 1999 Oki Electric Industry Co., Ltd.

## **OKI** Semiconductor

This version: Jan. 1999 Previous version: Mar. 1998

## MSM7630

**Universal Speech Processor**

#### **GENERAL DESCRIPTION**

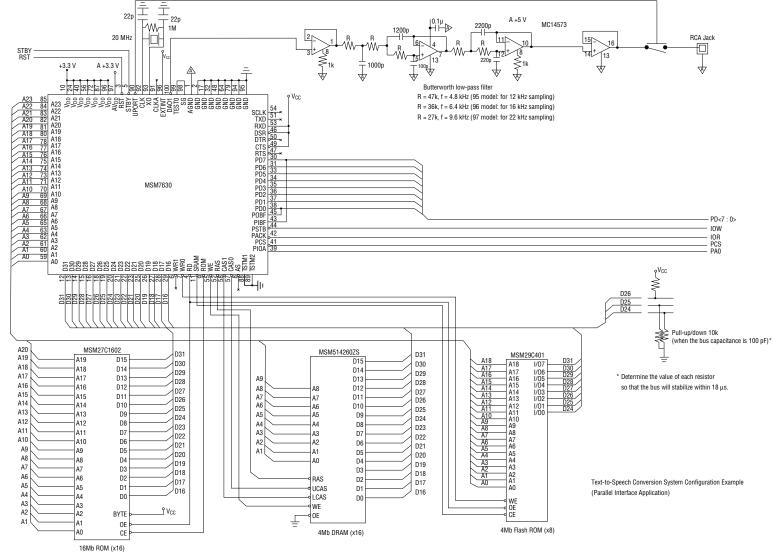

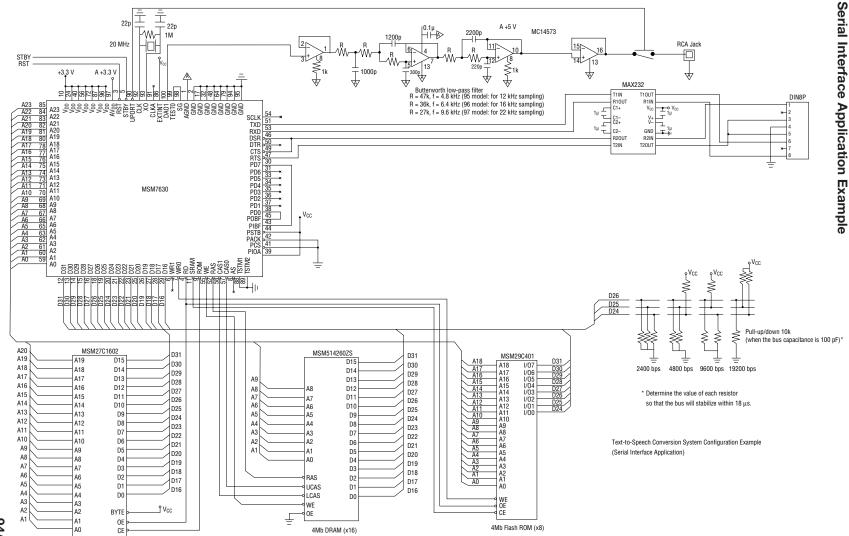

The MSM7630 is a speech processor LSI device with internal D/A converter. It is optimized for speech output applications such as text-to-speech conversion.

#### **FEATURES**

- Parallel and serial interfaces

- Single 3.3V power supply

- 5V interface available

- Internal 16-bit x 16-bit to 32-bit multiplier (2-clock data throughput)

- 26 VAX MIPS performance at 40 MHz operation (when using ordinary ROM/SRAM)

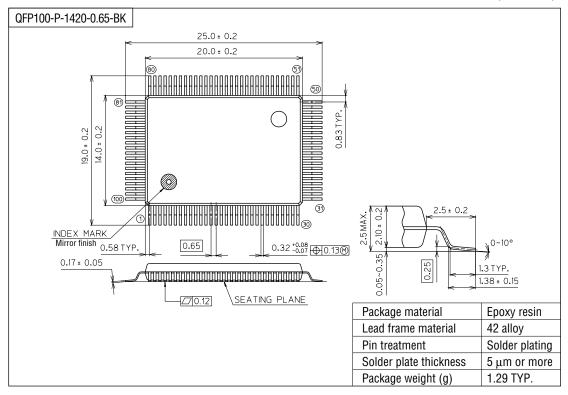

- Package: 100-pin plastic QFP (QFP100-P-1420-0.65-BK) (Product name: MSM7630GS-BK)

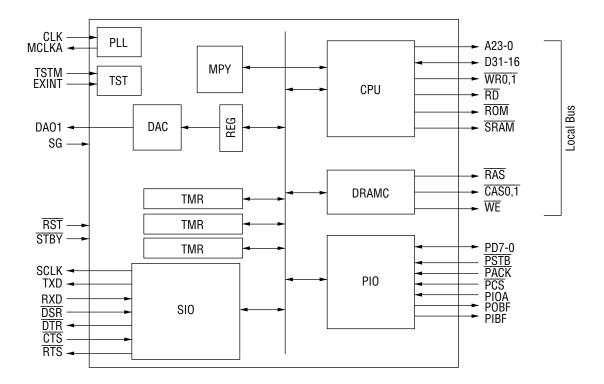

#### **BLOCK DIAGRAM**

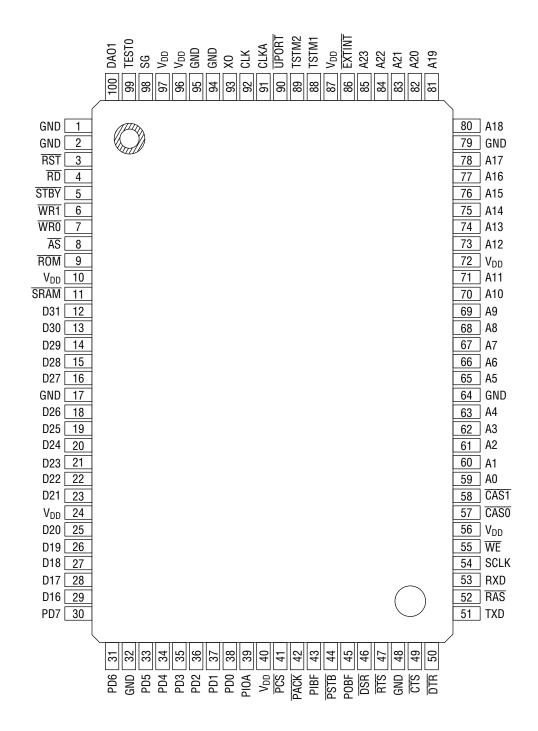

#### PIN CONFIGURATION (TOP VIEW)

100-Pin Plastic QFP

## **PIN DESCRIPTIONS**

| Symbol                                 | Туре                 | Description                                                                                                       |

|----------------------------------------|----------------------|-------------------------------------------------------------------------------------------------------------------|

| D31-16                                 | 1/0                  | 16-bit data bus. 8-bit devices are accessed through D31-24.                                                       |

| A23-0                                  | 0                    | 24-bit address bus. DRAM addresses are output from A13-0.                                                         |

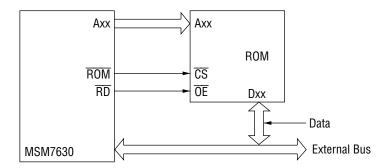

| DOM                                    | 0                    | ROM select signal. ROM indicates that ROM space is assigned to the specified address.                             |

| ROM                                    | 0                    | It is used as a chip select signal.                                                                               |

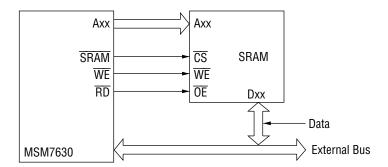

| SRAM                                   | 0                    | SRAM select signal. SRAM indicates that SRAM space is assigned to the specified address.                          |

| SKAIVI                                 | 0                    | It is used as a chip select signal.                                                                               |

| RD                                     | 0                    | Read signal. $\overline{\text{RD}}$ is active during both 8-bit and 16-bit reads.                                 |

| WR0,1                                  | 0                    | Write signals. $\overline{WR0}$ corresponds to writes from D31-24, and $\overline{WR1}$ corresponds to            |

| Whu, I                                 | U                    | writes from D23-16.                                                                                               |

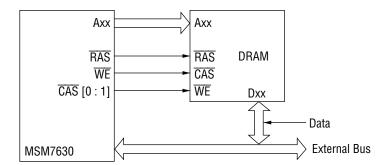

| RAS                                    | 0                    | Row address strobe. RAS is active during both 8-bit and 16-bit reads.                                             |

| CAS0,1                                 | 0                    | Column address strobe. $\overline{\text{CASO}}$ corresponds to accesses from D31-24, and $\overline{\text{CAS1}}$ |

| UA30, I                                | U                    | corresponds to accesses from D23-16.                                                                              |

| WE                                     | 0                    | Write enable. WE is active during writes to DRAM space as the DRAM write signal.                                  |

| AS                                     | 0                    | Address strobe.                                                                                                   |

| TXD                                    | 0                    | Serial data output.                                                                                               |

| RXD                                    | I                    | Serial data input.                                                                                                |

| DTR                                    | 0                    | Control signal indicating SIO can transmit and receive.                                                           |

| DSR                                    | I                    | Input signal indicating that modem is in operable state.                                                          |

| RTS                                    | 0                    | SIO transmit request signal.                                                                                      |

| CTS                                    | I                    | Input signal indicating that modem can transmit.                                                                  |

| SCLK                                   | 0                    | Synchronous transfer clock output.                                                                                |

| PD7-0                                  | 1/0                  | Parallel port data input/output.                                                                                  |

| PACK                                   | I                    | Parallel port read signal. Set high for Centronics interface.                                                     |

| PSTB                                   | I                    | Parallel port write signal. Strobe signal for Centronics interface.                                               |

| PCS                                    | I                    | Parallel port chip select signal.                                                                                 |

| PIOA                                   | ļ                    | Parallel port address signal. Selects data or status during an access.                                            |

| POBF                                   | 3-state              | Output port buffer full. Indicates that data has been set in the output buffer.                                   |

| PIBF                                   | 3-state              | Input port buffer full. Indicates that there is data in the input buffer.                                         |

| —————————————————————————————————————— | บ <sup>-</sup> รเลเษ | Busy output signal for Centronics interface.                                                                      |

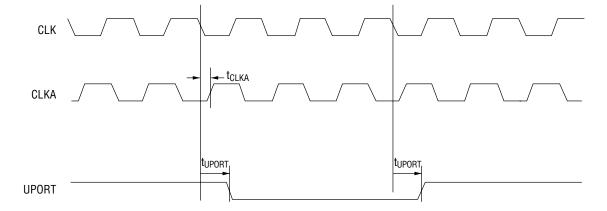

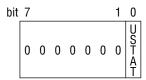

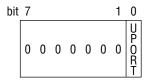

| UPORT                                  | 0                    | General flag output signal.                                                                                       |

| TEST0                                  | I                    | Connects with SG.                                                                                                 |

| DA01                                   | 0                    | D/A converter output.                                                                                             |

| SG                                     | I                    | Signal ground. Connects with TESTO.                                                                               |

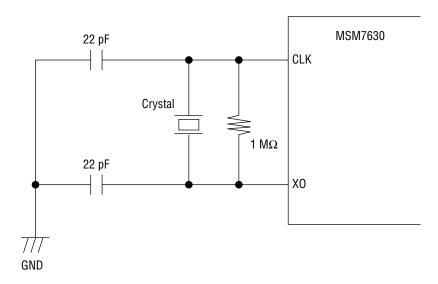

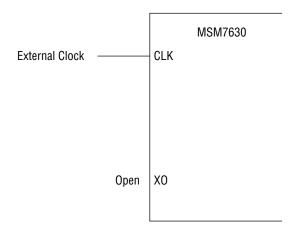

| CLK                                    | I                    | Clock input signal.                                                                                               |

| X0                                     | 0                    | Clock signal. Inverse of CLK.                                                                                     |

| CLKA                                   | 0                    | Internal clock signal.                                                                                            |

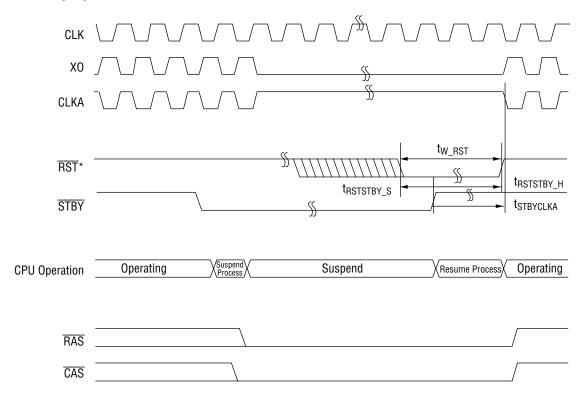

| RST                                    | I                    | Reset input.                                                                                                      |

| STBY                                   | I                    | Standby signal. STBY suspends operation and places the MSM7630 in a standby state.                                |

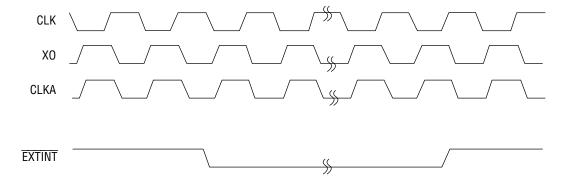

| EXTINT                                 | I                    | External interrupt signal.                                                                                        |

| TSTM2,1                                | 1                    | Test mode select input signal.                                                                                    |

## **ABSOLUTE MAXIMUM RATINGS**

| Parameter            | Symbol           | Condition                      | Rating       | Unit |

|----------------------|------------------|--------------------------------|--------------|------|

| Power Supply Voltage | V <sub>DD</sub>  | Ta = 25°C<br>(excluding TEST0) | -0.3 to +4.5 | V    |

| Input Voltage        | V <sub>IN</sub>  | Ta = 25°C                      | -0.3 to +5.5 | V    |

| Storage Temperature  | T <sub>STG</sub> | _                              | -55 to +125  | °C   |

## **RECOMMENDED OPERATING CONDITIONS**

| Parameter             | Symbol          | Conditon     | Range      | Unit |

|-----------------------|-----------------|--------------|------------|------|

| Power Supply Voltage  | $V_{DD}$        | _            | 3.0 to 3.6 | V    |

| Operating Temperature | T <sub>op</sub> | <del>_</del> | -40 to +85 | °C   |

## **ELECTRICAL CHARACTERISTICS**

#### **DC Characteristics**

| Parameter                    | Symbol           | Condition                  | Min.                | Тур. | Max.                | Unit |

|------------------------------|------------------|----------------------------|---------------------|------|---------------------|------|

| "H" Input Voltage            | V <sub>IH</sub>  | Excluding CLK              | 2.2                 | _    | _                   | V    |

| "L" Input Voltage            | V <sub>IL</sub>  | Excluding CLK              | _                   | _    | 0.8                 | V    |

| "H" Input Voltage            | V <sub>IH</sub>  | CLK                        | $0.8 \times V_{DD}$ | _    | _                   | V    |

| "L" Input Voltage            | V <sub>IL</sub>  | CLK                        | _                   | _    | $0.2 \times V_{DD}$ | V    |

| "H" Output Voltage           | V <sub>OH</sub>  | I <sub>OH</sub> = -4 mA    | 2.4                 | _    | _                   | V    |

| "L" Output Voltage           | V <sub>OL</sub>  | I <sub>OL</sub> = 4 mA     | _                   | _    | 0.4                 | V    |

| Input Leakage Current        | ILI              | $0 \le V_{IN} \le V_{DD}$  | -10                 | _    | +10                 | μΑ   |

| Output Leakage Current       | I <sub>LO</sub>  | $0 \le V_{OUT} \le V_{DD}$ | -10                 | _    | +10                 | μΑ   |

| Dynamic Supply Current       | Inc              | $V_{DD} = 3.6 \text{ V},$  | _                   |      | 120                 | mA   |

| Dynamic Supply Current       | I <sub>DO</sub>  | f <sub>OPE</sub> = 20 MHz  |                     | _    | 120                 | IIIA |

| Static Supply Current        | I <sub>DS</sub>  | _                          | _                   | _    | 1.5                 | mA   |

| D/A Output Relative Accuracy | V <sub>DAE</sub> | No load                    | _                   | _    | 10                  | mV   |

| D/A Output Impedance         | R <sub>DA</sub>  | _                          | 12                  | 20   | 28                  | kΩ   |

## **AC Characteristics**

|                           |                      | (188 ete te ete 1, 191E : e te 1e |      |      |                           |                  |  |

|---------------------------|----------------------|-----------------------------------|------|------|---------------------------|------------------|--|

| Parameter                 | Symbol               | Condition                         | Min. | Тур. | Max.                      | Unit             |  |

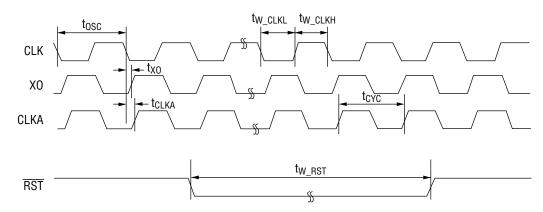

| Source Oscillation Period | tosc                 | _                                 | 25   | _    | 50                        | ns               |  |

| Input Clock Low-Level     | tw_clkl              | _                                 | 13   | _    | _                         | ns               |  |

| Minimum Width             |                      |                                   |      |      |                           |                  |  |

| Input Clock High-Level    | tw_clkH              | _                                 | 8    | _    | _                         | ns               |  |

| Minimum Width             |                      |                                   |      |      |                           |                  |  |

| Operating Period          | t <sub>CYC</sub>     | _                                 | 25   | _    | 50                        | ns               |  |

| CLKA Delay Time           | t <sub>CLK</sub>     | _                                 | _    | _    | 12                        | ns               |  |

| XO Delay Time             | t <sub>XO</sub>      | <del></del>                       | _    | _    | 7                         | ns               |  |

| Required RST Time         | t <sub>W_RST</sub>   | _                                 | 1024 | _    | _                         | t <sub>CYC</sub> |  |

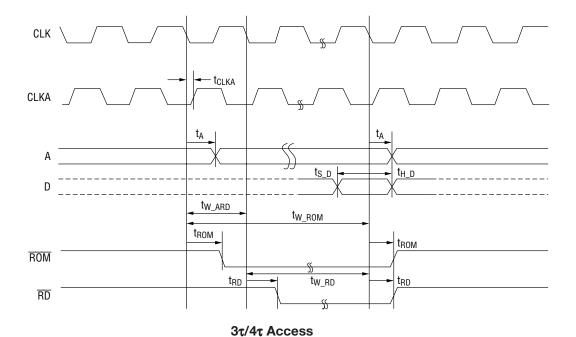

| A Delay Time              | t <sub>A</sub>       | _                                 | _    | _    | 22                        | ns               |  |

| D Setup Time              | t <sub>S_D</sub>     | _                                 | 2    | _    | _                         | ns               |  |

| D Hold Time               | t <sub>H_D</sub>     | _                                 | 6    | _    | _                         | ns               |  |

| D Delay Time              | t <sub>D</sub>       | <del></del>                       | _    | _    | 25                        | ns               |  |

| RD Delay Time             | t <sub>RD</sub>      | _                                 | _    | _    | 20                        | ns               |  |

| WR Delay Time             | t <sub>WR</sub>      | Falling                           | _    | _    | 22                        | ns               |  |

|                           |                      | Rising                            | _    | _    | 22 + 0.5 t <sub>CYC</sub> | ns               |  |

| UPORT Delay Time          | t <sub>UPORT</sub>   | <del></del>                       | _    | _    | 20                        | ns               |  |

| EXINT Setup Time          | t <sub>S_EXINT</sub> | _                                 | 2    | _    | _                         | ns               |  |

## ROM, SRAM Access

| Parameter        | Symbol              | Condition        | Min. | Тур. | Max.                      | Unit             |

|------------------|---------------------|------------------|------|------|---------------------------|------------------|

| RD Pulse Width   | t <sub>W_RD</sub>   | ROM, SRAM        | 2    | _    | 11                        | t <sub>CYC</sub> |

|                  |                     | 3τ to 12τ Access |      |      |                           |                  |

| WR Pulse Width   | t <sub>W_WR</sub>   | SRAM             | 1.5  | _    | 10.5                      | t <sub>CYC</sub> |

|                  |                     | 3τ to 12τ Access |      |      |                           |                  |

| A to RD Time     | t <sub>W_ARD</sub>  | ROM, SRAM        | _    | 1    | _                         | t <sub>CYC</sub> |

|                  |                     | 3τ, 4τ Access    |      |      |                           |                  |

|                  |                     | ROM, SRAM        | _    | 2    | _                         | t <sub>CYC</sub> |

|                  |                     | 5τ to 12τ Access |      |      |                           |                  |

| A to WR Time     | t <sub>W_AWR</sub>  | SRAM             | _    | 1    | _                         | t <sub>CYC</sub> |

|                  |                     | 3τ to 12τ Access |      |      |                           |                  |

| WR to SRAM Time  | tw_wrsram           | SRAM             | _    | 1    | _                         | t <sub>CYC</sub> |

|                  |                     | 3τ to 12τ Access |      |      |                           |                  |

| ROM Delay Time   | t <sub>ROM</sub>    | _                | _    | _    | 20 + 0.5 t <sub>CYC</sub> | ns               |

| SRAM Delay Time  | t <sub>SRAM</sub>   | _                | _    | _    | 20 + 0.5 t <sub>CYC</sub> | ns               |

| ROM Pulse Width  | t <sub>W_ROM</sub>  | ROM              | 3    | _    | 12                        | t <sub>CYC</sub> |

|                  |                     | 3τ to 12τ Access |      |      |                           |                  |

| SRAM Pulse Width | t <sub>W_SRAM</sub> | SRAM             | 3    | _    | 12                        | t <sub>CYC</sub> |

|                  |                     | 3τ to 12τ Access |      |      |                           |                  |

| WR to D Time     | t <sub>W_WRD</sub>  | SRAM             | _    | 0    | _                         | t <sub>CYC</sub> |

|                  |                     | 3τ Access        |      |      |                           |                  |

|                  |                     | SRAM             | _    | 1    | _                         | tcyc             |

|                  |                     | 4τ to 12τ Access |      |      |                           |                  |

#### DRAM Access

$(V_{DD} = 3.0 \text{ to } 3.6 \text{ V}, T_{OPE} = -40 \text{ to } +85^{\circ}\text{C})$

|                         |                     |                    | 1 55 |      | 7 0.2                     |                  |

|-------------------------|---------------------|--------------------|------|------|---------------------------|------------------|

| Parameter               | Symbol              | Condition          | Min. | Тур. | Max.                      | Unit             |

| RAS Delay Time          | t <sub>RAS</sub>    | _                  | _    | _    | 18                        | ns               |

| RAS Pulse Width         | t <sub>W_RAS</sub>  | _                  | 3    | _    | Note 1                    | t <sub>CYC</sub> |

| A to RAS Time           | tw_aras             | _                  | 1    | _    | _                         | t <sub>CYC</sub> |

| CAS Delay Time          | t <sub>CAS</sub>    | 2nτ access falling | _    | _    | 18 + 0.5 t <sub>CYC</sub> | ns               |

|                         |                     | edge               |      |      |                           |                  |

|                         |                     | Normal             | _    | _    | 18                        | ns               |

| CAS Pulse Width         | t <sub>W_CAS</sub>  | Normal             | 1.5  | _    | 2                         | t <sub>CYC</sub> |

|                         |                     | Refresh            | 4    | _    | 5                         | tcyc             |

| A to CAS Time           | tw_acas             | _                  | 0.5  | _    | 1                         | ns               |

| RAS to CAS Time         | tw_rascas           | _                  | 1.5  | _    | 2                         | t <sub>CYC</sub> |

| WE to CAS Time          | tw_wecas            | _                  | 1.5  | _    | 2                         | t <sub>CYC</sub> |

| WE Delay Time           | t <sub>WE</sub>     | _                  | _    | _    | 20                        | ns               |

| WE Pulse Width          | tw_we               | _                  | 3    | _    | Note 1                    | tcyc             |

| A to WE Time            | t <sub>W_AWE</sub>  | _                  | _    | 1    | _                         | t <sub>CYC</sub> |

| Required Precharge Time | t <sub>W_PREC</sub> | _                  | 1    | _    | Note 2                    | t <sub>CYC</sub> |

| CAS to RAS Time         | tw_casras           | _                  | _    | 1    | _                         | t <sub>CYC</sub> |

| CAS to D Time           | t <sub>W_EDO</sub>  | Hyper Mode         | _    | _    | 1                         | t <sub>CYC</sub> |

## General Device Access

| Parameter     | Symbol | Condition | Min. | Тур. | Max. | Unit |

|---------------|--------|-----------|------|------|------|------|

| AS Delay Time | tas    | _         | _    | _    | 18   | ns   |

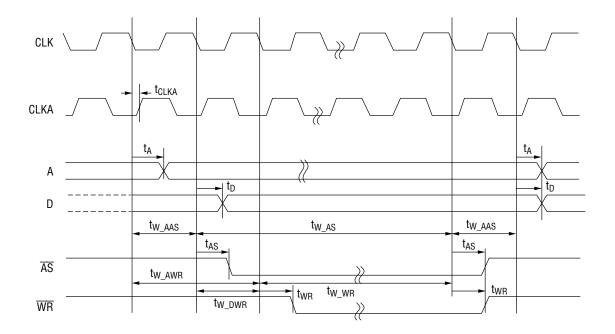

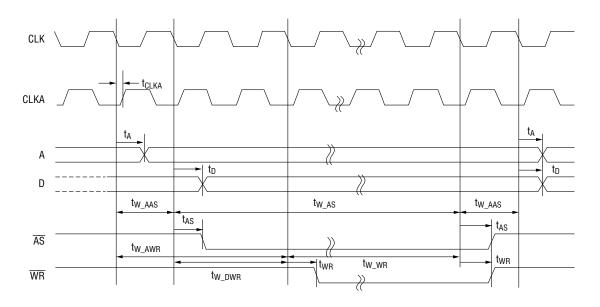

When DS bit = 0

| Parameter      | Symbol             | Condition        | Min. | Тур. | Max. | Unit             |

|----------------|--------------------|------------------|------|------|------|------------------|

| AS Pulse Width | t <sub>W_AS</sub>  | 4τ to 7τ Access  | 2    | _    | 5    | t <sub>CYC</sub> |

|                |                    | (X bit = 0)      |      |      |      |                  |

|                |                    | 8τ to 14τ Access | 6    | _    | 12   | t <sub>CYC</sub> |

|                |                    | (X bit = 1)      |      |      |      |                  |

| A to AS Time   | t <sub>W_AAS</sub> | 4τ to 7τ Access  | _    | 1    | _    | t <sub>CYC</sub> |

|                |                    | (X bit = 0)      |      |      |      |                  |

|                |                    | 8τ to 14τ Access | _    | 1    | _    | t <sub>CYC</sub> |

|                |                    | (X bit = 1)      |      |      |      |                  |

| RD Pulse Width | t <sub>W_RD</sub>  | 4τ to 7τ Access  | 2    | _    | 5    | t <sub>CYC</sub> |

|                |                    | (X bit = 0)      |      |      |      |                  |

|                |                    | 8τ to 14τ Access | 6    | _    | 12   | tcyc             |

|                |                    | (X bit = 1)      |      |      |      |                  |

| A to RD Time   | t <sub>W_ARD</sub> | 4τ to 7τ Access  | _    | 1    | _    | t <sub>CYC</sub> |

|                |                    | (X bit = 0)      |      |      |      |                  |

|                |                    | 8τ to 14τ Access | _    | 1    | _    | t <sub>CYC</sub> |

|                |                    | (X bit = 1)      |      |      |      |                  |

| WR Pulse Width | t <sub>W_WR</sub>  | 4τ to 7τ Access  | 2    | _    | 5    | t <sub>CYC</sub> |

|                |                    | (X bit = 0)      |      |      |      |                  |

|                |                    | 8τ to 14τ Access | 6    | _    | 12   | t <sub>CYC</sub> |

|                |                    | (X bit = 1)      |      |      |      |                  |

| A to WR Time   | t <sub>W_AWR</sub> | 4τ to 7τ Access  | _    | 1    | _    | tcyc             |

|                |                    | (X bit = 0)      |      |      |      |                  |

|                |                    | 8τ to 14τ Access | _    | 1    | _    | t <sub>CYC</sub> |

|                |                    | (X bit = 1)      |      |      |      |                  |

| D to WR Time   | t <sub>W_DWR</sub> | 4τ to 7τ Access  | _    | 0    | _    | t <sub>CYC</sub> |

|                |                    | (X bit = 0)      |      |      |      |                  |

|                |                    | 8τ to 14τ Access | _    | 0    | _    | t <sub>CYC</sub> |

|                |                    | (X bit = 1)      |      |      |      |                  |

When DS bit = 1

| Parameter      | Symbol             | Condition        | Min. | Тур. | Max. | Unit             |

|----------------|--------------------|------------------|------|------|------|------------------|

| AS Pulse Width | t <sub>W_AS</sub>  | 4τ to 7τ Access  | 2    | _    | 5    | t <sub>CYC</sub> |

| Note 3         |                    | (X bit = 0)      |      |      |      |                  |

|                |                    | 8τ to 14τ Access | 6    | _    | 12   | tcyc             |

|                |                    | (X bit = 1)      |      |      |      |                  |

| A to AS Time   | t <sub>W_AAS</sub> | 4τ to 7τ Access  | _    | 1    | _    | t <sub>CYC</sub> |

|                |                    | (X bit = 0)      |      |      |      |                  |

|                |                    | 8τ to 14τ Access | _    | 1    | _    | t <sub>CYC</sub> |

|                |                    | (X bit = 1)      |      |      |      |                  |

| RD Pulse Width | t <sub>W_RD</sub>  | 4τ to 7τ Access  | 2    | _    | 5    | tcyc             |

|                |                    | (X bit = 0)      |      |      |      |                  |

|                |                    | 8τ to 14τ Access | 6    | _    | 12   | t <sub>CYC</sub> |

|                |                    | (X bit = 1)      |      |      |      |                  |

| A to RD Time   | t <sub>W_ARD</sub> | 4τ to 7τ Access  | _    | 1    | _    | tcyc             |

|                |                    | (X bit = 0)      |      |      |      |                  |

|                |                    | 8τ to 14τ Access | _    | 1    | _    | t <sub>CYC</sub> |

|                |                    | (X bit = 1)      |      |      |      |                  |

| WR Pulse Width | t <sub>W_WR</sub>  | 4τ to 7τ Access  | 2    | _    | 5    | t <sub>CYC</sub> |

|                |                    | (X bit = 0)      |      |      |      |                  |

|                |                    | 8τ to 14τ Access | 6    | _    | 12   | t <sub>CYC</sub> |

|                |                    | (X bit = 1)      |      |      |      |                  |

| A to WR Time   | t <sub>W_AWR</sub> | 4τ to 7τ Access  | _    | 2    | _    | t <sub>CYC</sub> |

|                |                    | (X bit = 0)      |      |      |      |                  |

|                |                    | 8τ to 14τ Access | _    | 3    | _    | t <sub>CYC</sub> |

|                |                    | (X bit = 1)      |      |      |      |                  |

| D to WR Time   | t <sub>W_DWR</sub> | 4τ to 7τ Access  | _    | 1    | _    | t <sub>CYC</sub> |

|                |                    | (X bit = 0)      |      |      |      |                  |

|                |                    | 8τ to 14τ Access | _    | 2    | _    | t <sub>CYC</sub> |

|                |                    | (X bit = 1)      |      |      |      |                  |

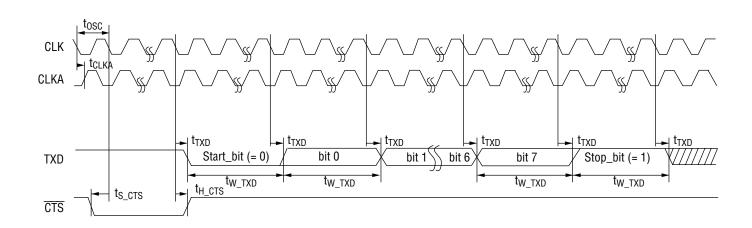

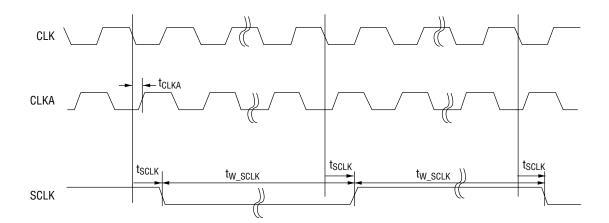

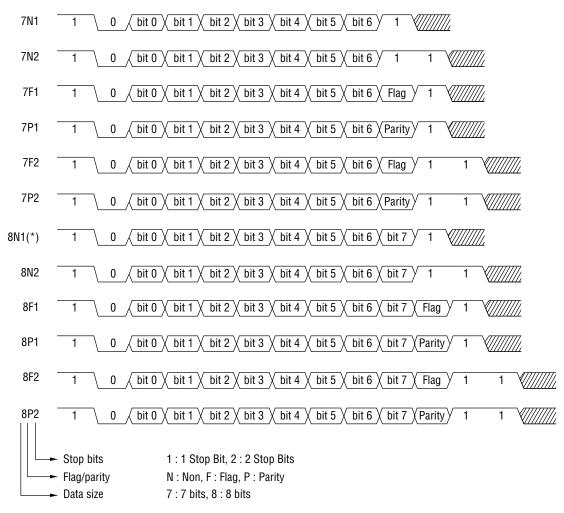

#### Serial Interface

$(V_{DD} = 3.0 \text{ to } 3.6 \text{ V}, T_{OPE} = -40 \text{ to } +85^{\circ}\text{C})$

| Parameter         | Symbol              | Condition | Min.    | Тур. | Max. | Unit |

|-------------------|---------------------|-----------|---------|------|------|------|

| RTS Delay Time    | t <sub>RTS</sub>    | _         | _       | _    | 20   | ns   |

| Required RXD Time | t <sub>W_RXD</sub>  | _         | 1/bps   | _    | _    | S    |

| RXD Setup Time    | t <sub>S_RXD</sub>  | _         | 0.5/bps | _    | _    | S    |

| RXD Hold Time     | t <sub>H_RXD</sub>  | _         | 0.5/bps | _    | _    | S    |

| CTS Setup Time    | t <sub>S_CTS</sub>  | _         | 0       | _    | _    | ns   |

| CTS Hold Time     | t <sub>H_CTS</sub>  | _         | 0       | _    |      | ns   |

| TXD Delay Time    | t <sub>TXD</sub>    | _         | _       | _    | 20   | ns   |

| TXD Pulse Width   | t <sub>W_TXD</sub>  | _         | 1/bps   | _    | _    | S    |

| DTR Delay Time    | t <sub>DTR</sub>    | _         | _       | _    | 20   | ns   |

| SCLK Delay Time   | t <sub>SCLK</sub>   | _         | _       | _    | 20   | ns   |

| SCLK Pulse Width  | t <sub>W_SCLK</sub> | <u> </u>  | 1/bps   | _    |      | S    |

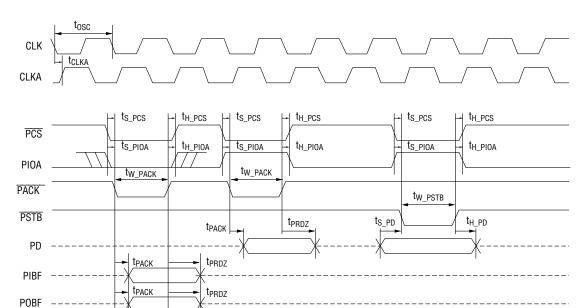

#### Parallel Interface

$(V_{DD} = 3.0 \text{ to } 3.6 \text{ V}, T_{OPE} = -40 \text{ to } +85^{\circ}\text{C})$

| Parameter                     | Symbol              | Condition | Min.                    | Тур. | Max. | Unit |

|-------------------------------|---------------------|-----------|-------------------------|------|------|------|

| PACK to PD Delay Time         | t <sub>PACK</sub>   | _         | _                       | _    | 22   | ns   |

| PACK to PD Hi Z Delay Time    | t <sub>PRDZ</sub>   | _         | _                       | _    | 22   | ns   |

| PCS Setup Time for PSTB/PACK  | t <sub>S_PCS</sub>  | _         | 0                       | _    | _    | ns   |

| PCS Hold Time for PSTB/PACK   | t <sub>H_PCS</sub>  | _         | 0                       | _    | _    | ns   |

| PIOA Setup Time for PSTB/PACK | ts_pioa             | _         | 0                       | _    | _    | ns   |

| PIOA Hold Time for PSTB/PACK  | t <sub>H_PIOA</sub> | _         | 3                       | _    | _    | ns   |

| Required PACK Time            | tw_pack             | _         | 30 + t <sub>CYC</sub>   | _    | _    | ns   |

| Required PSTB Time            | t <sub>W_PSTB</sub> | _         | 30 + 2 t <sub>CYC</sub> | _    | _    | ns   |

| PD Setup Time for PSTB        | t <sub>S_PD</sub>   | _         | -t <sub>CYC</sub>       | _    | _    | ns   |

| PD Hold Time for PSTB         | t <sub>H_PD</sub>   | _         | 8                       | _    | _    | ns   |

Note 1 According to DRAM configuration

Note 2 By the DRAM access timing

Note 3 In the case of writing, increased by 1 clock when X bit = 0 and by 2 clocks when X bit = 1.

Note 4 Flash memory access timing is the same with the SRAM timing.

## **TIMING DIAGRAM**

## **Clock And Reset**

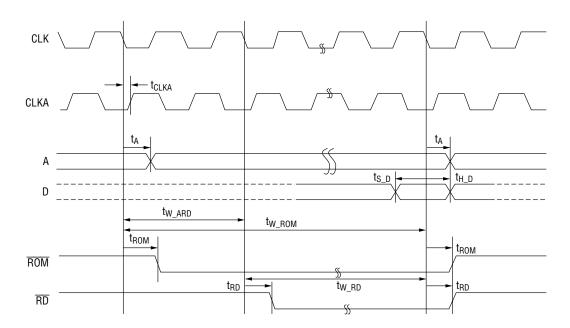

## **ROM Read**

5τ/6τ/8τ/10τ/12τ Access

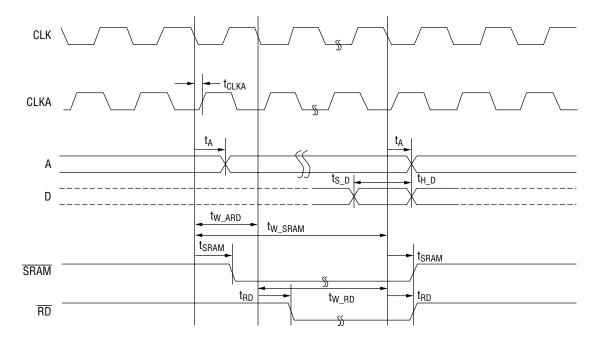

## **SRAM Read**

3τ/4τ Access

5τ/6τ/8τ/10τ/12τ Access

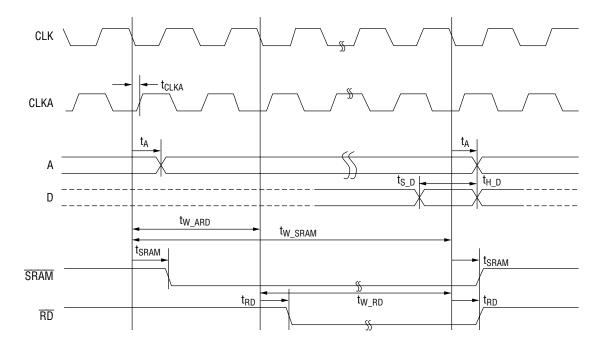

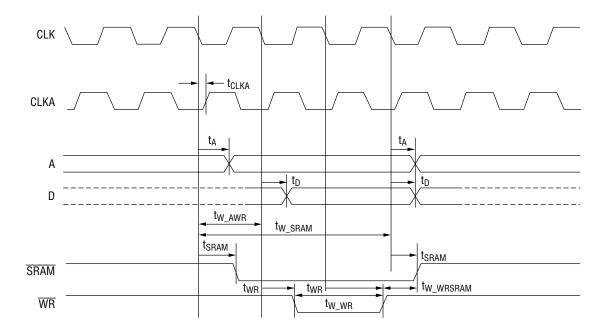

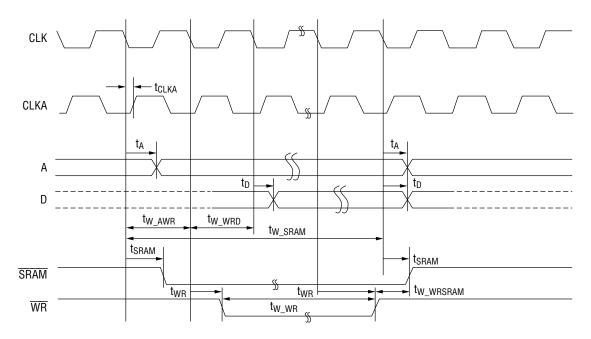

## **SRAM Write**

**3τ Access**

4τ/5τ/6τ/8τ/10τ/12τ Access

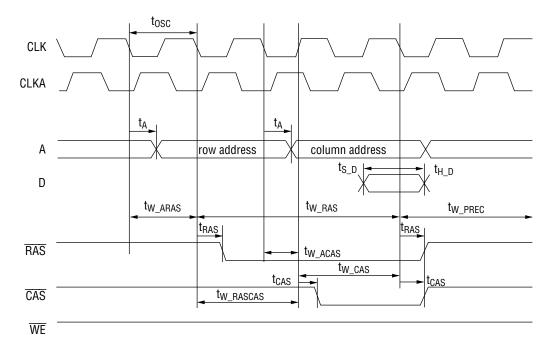

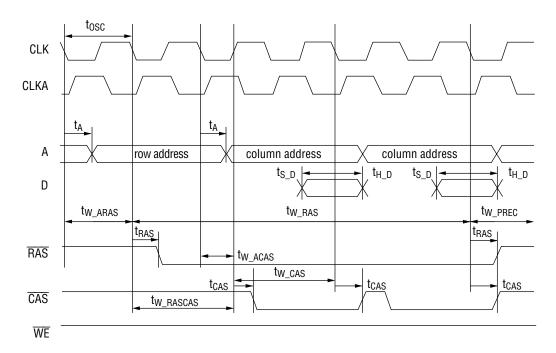

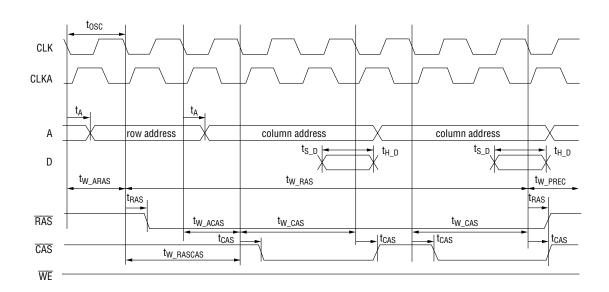

#### **DRAM Read**

2nt Access (Fast Page Mode)

2nτ Access (Fast Page Mode)

3ητ Access (Fast Page Mode)

3nτ Access (Fast Page Mode)

3nτ Access (Hyperpage Mode)

3nτ Access (Hyperpage Mode)

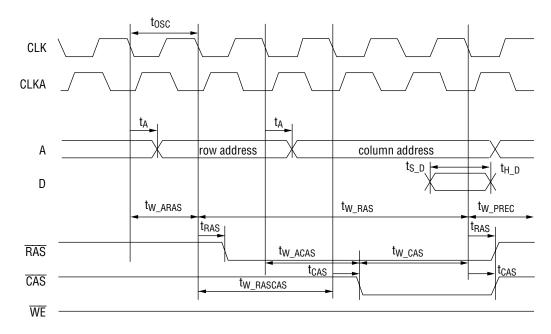

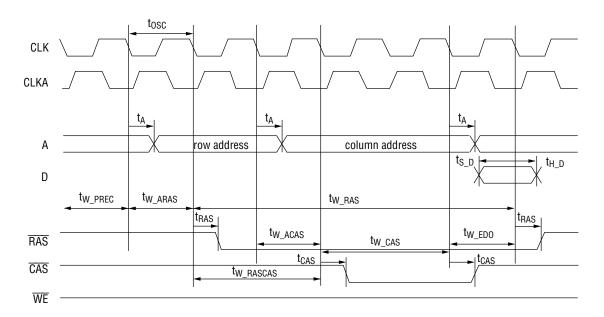

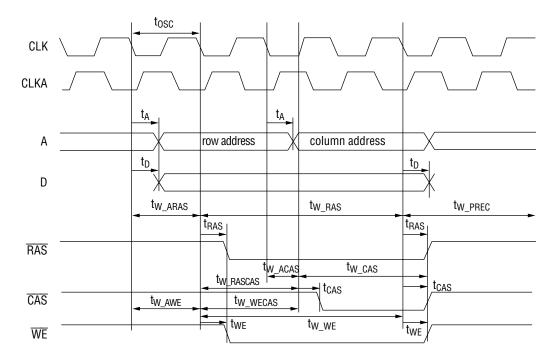

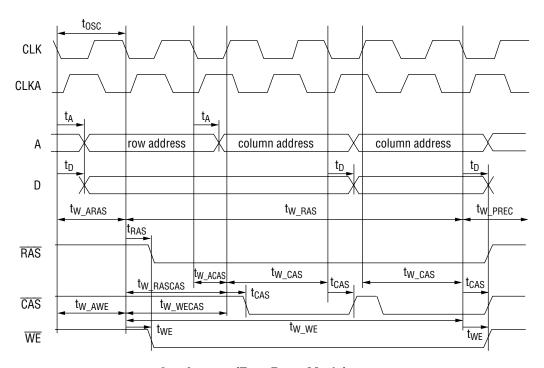

#### **DRAM Write**

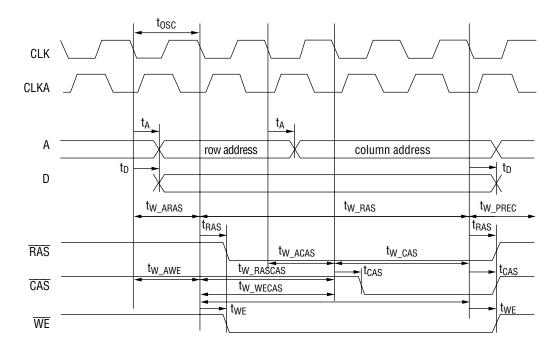

2nτ Access (Fast Page Mode)

2nτ Access (Fast Page Mode)

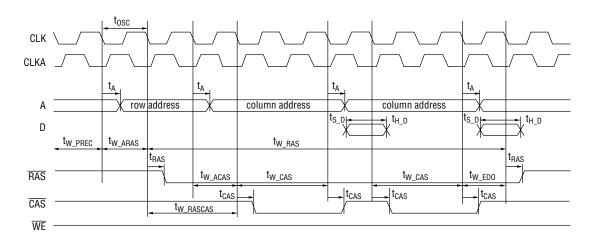

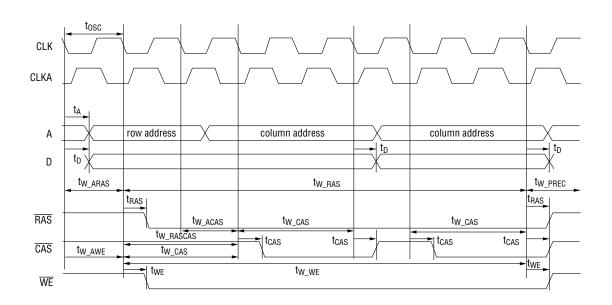

3nτ Access (Fast Page Mode/Hyperpage Mode)

3nτ Access (Fast Page Mode/Hyperpage Mode)

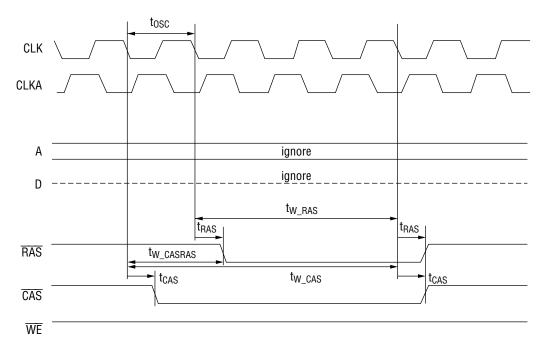

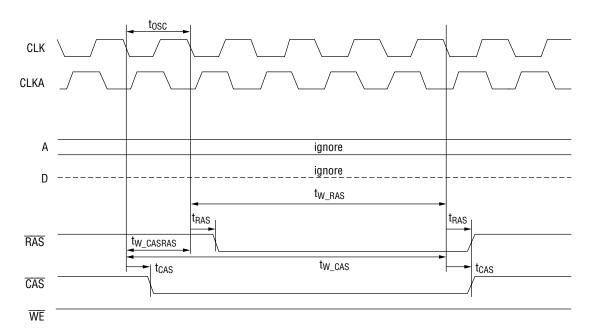

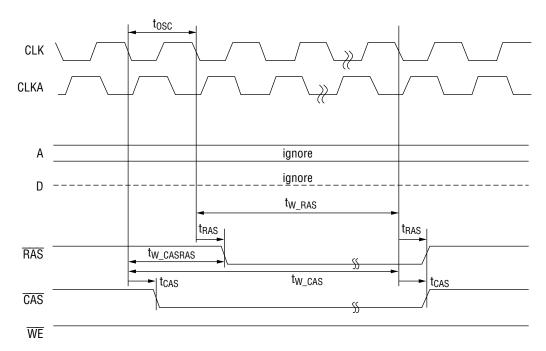

#### **DRAM Refresh**

2nτ CAS-Before-RAS Refresh

3ητ CAS-Before-RAS Refresh

**CAS-Before-RAS Self-Refresh**

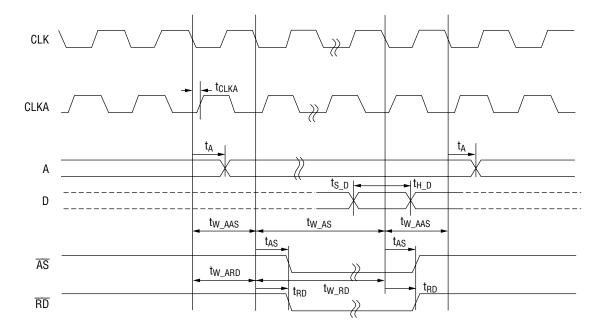

## **General Device Access**

**Bus Read**

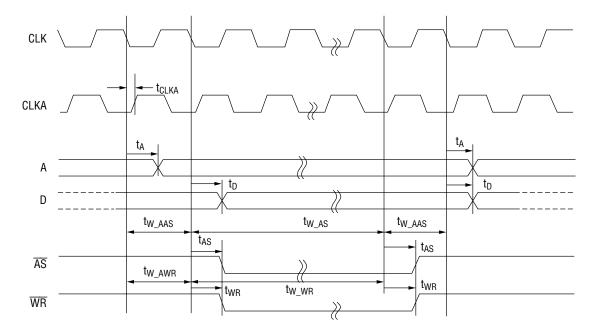

Bus Write (When DS bit in the SCR register is "0")

Bus Write (When DS bit is "1" and X bit is "0" in the SCR register)

Bus Write (When DS bit is "1" and X bit is "1" in the SCR register)

## **Parallel Interface**

Serial Interface

#### CLK CLKA $t_{H\_RXD}$ t<sub>S\_RXD</sub> t<sub>H\_RXD</sub> $t_{S\_RXD}$ t<sub>H\_RXD</sub> $t_{H\_RXD}$ t<sub>S\_RXD</sub> t<sub>S\_RXD</sub> RXD Start\_bit (= 0) bit 0 bit 7 Stop\_bit (= 1) bit 6 t<sub>W\_RXD</sub> t<sub>W\_RXD</sub> t<sub>W\_RXD</sub> t<sub>W\_RXD</sub> ± t<sub>RTS</sub> ► t<sub>RTS</sub> RTS

**Synchronous Transfer Output**

## **General Port Output**

**General Port Output**

#### **Standby Operation**

$\label{eq:maintain} \mbox{Maintain the pin level on the $\overline{STBY}$ signal until the CPU has completed its suspend process and clock signal CLKA has stopped.}$

After the  $\overline{\text{STBY}}$  signal is released, the CPU will not resume until oscillation has stabilized (1024  $t_{CYC}$ ).

<sup>\*</sup> The  $\overline{\text{RST}}$  signal is not necessary for self-refresh DRAM.

## **Interrupt Process**

The external interrupt signal  $\overline{EXTINT}$  requests an interrupt to the CPU. The pin level on  $\overline{EXTINT}$  must be maintained until the CPU accepts the interrupt. Also, be sure to clear the interrupt source within the interrupt routine.

#### **FUNCTIONAL DESCRIPTION**

#### **CPU Core**

#### 1. Features

The SCP (Speech Control Processor) uses a CPU core with an Oki-original 32-bit RISC architecture.

## 2. Register Configuration

The CPU core registers are configured as 32 words for general registers, 7 words for privileged registers, and 1 word for a special register.

| General Registers |

|-------------------|

| %r0 (link)        |

| %r1 (pre-PC)      |

| %r2 (pre-nPC)     |

| %r3 (long-immed.) |

| %r4               |

| %r5               |

|                   |

|                   |

|                   |

|                   |

|                   |

| %r30              |

| %r31              |

| Privileged Registers |  |  |  |  |  |  |  |

|----------------------|--|--|--|--|--|--|--|

| %PSR                 |  |  |  |  |  |  |  |

| %VBA                 |  |  |  |  |  |  |  |

| %prPSR               |  |  |  |  |  |  |  |

| %IRR                 |  |  |  |  |  |  |  |

| %BPA                 |  |  |  |  |  |  |  |

| %PC                  |  |  |  |  |  |  |  |

| %nPC                 |  |  |  |  |  |  |  |

|                      |  |  |  |  |  |  |  |

|                      |  |  |  |  |  |  |  |

|                      |  |  |  |  |  |  |  |

| Special Register     |  |  |  |  |  |  |  |

%NOP

#### 2.1 General Registers

The general registers are a set of 32 registers with 32-bit width. Of these registers %r0 to %r3 can be used as general registers, but they do have special functions pre-assigned by the system. Registers %r4 to %r31 can be used freely. Contents are undefined after reset.

| bit 31 |    | 0 |

|--------|----|---|

|        |    |   |

|        | GR |   |

|        | un |   |

|        |    |   |

%r0: Link register (stores subroutine return address). Also stores %PC+4 during bl instruction execution.

- %r1: Stores value of %PC when an exception, interrupt, or trap is accepted.

- %r2: Stores value of %nPC when an exception, interrupt, or trap is accepted.

- %r3: Stores the immediate value of SETLI (Set Long Immediate) instructions.

#### 2.2 Privileged Registers

Reads are allowed at any processor level (Processor Level: 0 = user mode, 1 or above = supervisor mode), but write accesses are allowed only when the processor level is supervisor mode. The privileged registers are configured as 7 words, and are used primarily for processor control. If the processor attempts a write access to a privileged register while in user mode, then the instruction will not be executed and a privileged instruction exception will be issued.

### 2.2.1 PSR (Processor Status Register)

This register sets and displays the state of the processor.

| bit : | 31  | 28 | 27 | 26 | 25 | 24 | 23 | 22     | 21     | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4      | 3 |    | 0 |

|-------|-----|----|----|----|----|----|----|--------|--------|----|----|----|----|----|----|----|----|----|----|----|---|---|---|---|---|--------|---|----|---|

|       |     |    |    |    |    |    |    | M      | M      |    |    |    |    |    |    |    |    |    |    |    |   | N |   |   | F |        |   |    |   |

|       | VER |    | 0  | 0  | 0  | 0  | 0  | F<br>U | F<br>U | 0  | 0  | 0  | 0  | 0  | ٧  | С  | N  | Z  | 0  | Ċ  | Ċ | Ö | 0 | 0 | B | E<br>M |   | PL |   |

|       |     |    |    |    |    | l  |    | 32     | 16     | ı  |    |    |    |    |    |    |    |    |    | -  | _ | - |   |   | F |        |   |    |   |

• bit[31:28] VER: Version (read-only)

Indicates the CPU core version. Currently fixed to "3".

• bit[22] MFU32 (read-only)

Indicates whether the 32-bit multiplier unit is present ("1") or not ("0"). This is "0" for the MSM7630.

• bit[21] MFU16 (read-only)

Indicates whether the 16-bit multiplier unit is present ("1") or not ("0"). This is "1" for the MSM7630.

• bit[15] V: Overflow (read-only)

Indicates that execution of an addition or subtraction instruction resulted in an arithmetic overflow.

• bit[14] C: Carry (read-only)

Indicates that execution of an addition or subtraction instruction resulted in an arithmetic carry or borrow.

• bit[13] N: Negative (read-only)

Indicates that execution of an addition or subtraction instruction resulted in a negative value (bit[31] is "1").

• bit[12] Z: Zero (read-only)

Indicates that execution of an addition or subtraction instruction resulted in a zero value (bit[31:0] are all "0").

• bit[10] ICP: Instruction Cache Purge (read/write)

Invalidates all instruction cache entries. Writing "1" to this bit purges the contents of the instruction cache. After this process (after one cycle) this bit is automatically cleared to "0" by hardware. The instruction cache is purged during reset.

• bit[9] ICL: Instruction Cache Lock (read/write)

Freezes all instruction cache entries. After "1" is written to this bit, instruction cache contents are frozen and then instruction execution continues. This bit will be "1" after reset.

• bit[8] NOP: Non-Operation (read-only)

When set to "1", forces the next instruction to a NOP regardless of the instruction. There is no way to directly set this bit to "1". This bit will be "0" after reset.

• bit [5] EBP: Breakpoint Trap Enable (read/write)

Enables breaks. If this bit is set to "1", then a trap will occur when the value of the instruction execution address (%PC) equals the value of the breakpoint address (%BPA). The instruction that generated the break will not be executed. This bit will be "0" after reset.

• bit[4] EM: Master Enable (read/write)

Disables all exceptions, interrupts, and traps. This bit automatically becomes "0" at the point when the processor accepts an exception, interrupt, or trap. While this bit is "0", further exceptions, interrupts or traps will not be accepted, with instruction execution continuing in the normal instruction sequence. An instruction must be used to return this bit to "1". It will be "0" after reset.

• bit[3:0] PL: Processor Level (read/write)

Sets and provides the processor's instruction execution level. Processor levels are 0-15. An external interrupt will be accepted if its level has a higher priority than the processor level at that time. External interrupt levels are 1-16, so when PL is 0 all external interrupts will be accepted, and when PL is 1 external interrupts of level 2 and above will be accepted. When an external interrupt is accepted, the processor level will become the same as the external interrupt level. For example, if PL is 5 and a level 7 external interrupt is accepted, then PL will transition to 7 at that point. When PL is restored to its previous state, its saved value in %prPSR will be restored to %PSR. Alternatively PL can be set to its previous value explicitly by an instruction in the interrupt process routine. However, %PSR is a privileged register, so writes are only permitted in supervisor mode. PL will be set to 15 after reset.

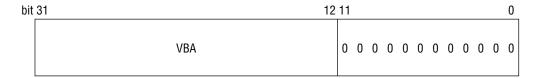

#### 2.2.2 VBA: Vector Base Address (read/write)

This read/write register sets the leading address of the dispatch table (vector table) to exception, interrupt, and trap process routines.

The dispatch table is 256 entries of 4K bytes size, with 16 bytes (4 instructions) save for each entry's dispatch routine. Entry points are generated by an OR operation with this register, so they are set at 4K-byte boundaries. As a result, only the upper 20 bits of an argument will be written to the VBA register (the lower 12 bits will be ignored).

This register is undefined after reset.

#### 2.2.3 prPSR: Pre-Processor Status Register (read/write)

This read/write register saves the value of %PSR at the time an exception, interrupt, or trap is accepted. In order to accept overlapping exceptions, interrupts, and traps, the value of %prPSR must be pushed on a stack and then EM of %PSR must be set to "1".

| bit 31 | 28 | 27 | 26    | 25 | 24 | 23 | 22                | 21                | 20 | 19 | 18 | 17 | 16 | 15     | 14     | 13     | 12     | 11 | 10          | 9           | 8           | 7 | 6 | 5                | 4           | 3 |     | 0 |

|--------|----|----|-------|----|----|----|-------------------|-------------------|----|----|----|----|----|--------|--------|--------|--------|----|-------------|-------------|-------------|---|---|------------------|-------------|---|-----|---|

| VER    |    | 0  | 0<br> | 0  | 0  | 0  | M<br>F<br>U<br>32 | M<br>F<br>U<br>16 | 0  | 0  | 0  | 0  | 0  | p<br>V | p<br>C | p<br>N | p<br>Z | 0  | P<br>C<br>P | p<br>C<br>L | P<br>O<br>P | 0 | 0 | p<br>E<br>B<br>P | p<br>E<br>M |   | pPL |   |

The upper 16 bits of %prPSR are always identical to %PSR. Refer to the descriptions of the same bit positions in %PSR for an explanation of %prPSR bits.

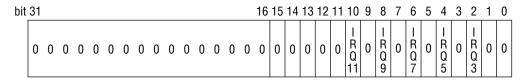

#### 2.2.4 IRR: Interrupt Request Register (read-only)

This register indicates whether there is an interrupt request at each of the 16 levels of external interrupts. It is read-only, and shows interrupt requests regardless of PL (processor level). The IRR value will continue until an interrupt source is released.

| bit 31                      | 16 15 14 13 12 11 10 9 8 | 7 6 5 4 3 2 1 0 |

|-----------------------------|--------------------------|-----------------|

| 0 0 0 0 0 0 0 0 0 0 0 0 0 0 |                          |                 |

The MSM7630 uses only 6 interrupts of the 16 interrupt levels.

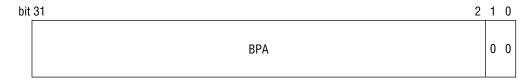

#### 2.2.5 BPA: Breakpoint Address (read/write)

This read/write register sets and shows the instruction address (byte address) where a breakpoint trap occurred. The lowest 2 bits will always be "0". When EBP of %PSR is "1", a trap will be generated immediately before execution of the instruction at the breakpoint set by this register. This register will be undefined after reset.

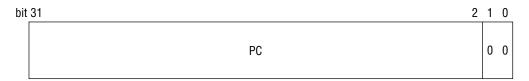

## 2.2.6 PC: Program Counter (read-only)

This read-only register provides the instruction address (byte address) in the execution phase. Its lowest 2 bits will always be "0".

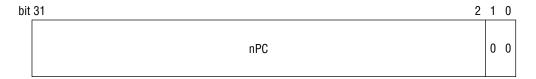

#### 2.2.7 nPC: Next Program Counter (read-only)

This read-only register provides the instruction address (byte address) in the instruction decode phase. Its lowest 2 bits will always be "0".

### 2.3 Special Registers

These are not privileged registers, but they are special registers used for specific functions.

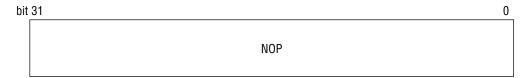

## 2.3.1 NOP: Non-Operation (read/write)

When this register is specified as a destination register, execution results will not be stored anywhere. When specified as a source register, it will read as an undefined value.

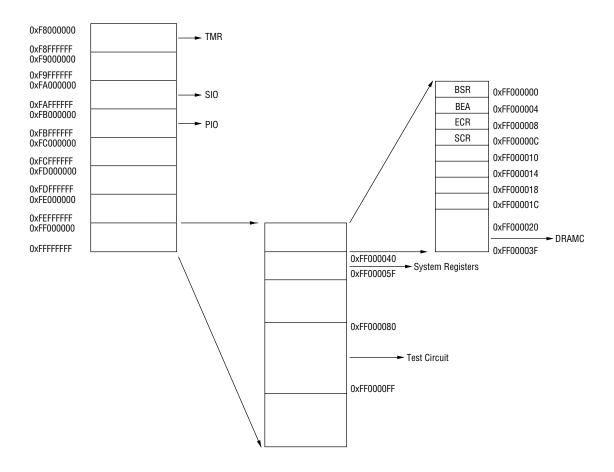

#### 3. Data Formats

There are two data format types: one for internal processor core calculations and one for memory accesses.

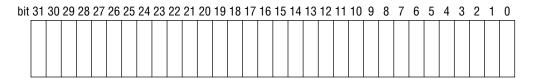

#### 3.1 Internal Data Format

The CPU core handles all data as 32 bits (word format). Therefore, when the format of data stored in memory is byte (8 bits) or half-word (16 bits) it must be used internally as 32-bit data through a signed load instruction or unsigned load instruction. Similarly when internal core processing results are stored to memory, a store instruction corresponding to the data format in memory must be executed. Also, bit addresses specified for bit test instructions and bit manipulation instructions are shown in the diagram below.

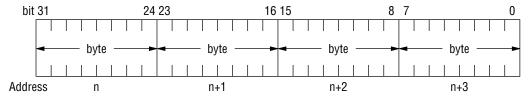

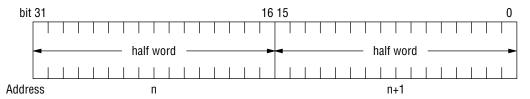

### 3.2 Memory Data Format

The following memory data formats are supported: byte (8 bits), half-word (16 bits), and word (32 bits). Memory addresses are always byte addresses regardless of data format. However, half-word accesses must be on 16-bit boundaries (least significant bit is "0"), and word accesses must be on 32-bit boundaries (least significant 2 bits are "00"). If a load or store instruction execution attempts a memory access that violates these boundaries, then a data address invalid exception will occur. Memory addressing is big-endian. The diagrams below show memory data formats for byte data access, half-word data access, and word data access.

#### Byte Data Access

#### Half-Word Data Access

#### Word Data Access

## 3.3 Memory Addressing Modes

Memory addresses are byte addresses, so memory addressing is performed with three types of load instructions and two types of store instructions. Swap instructions have the same memory addressing as store instructions.

### 3.3.1 Load Instruction Addressing

#### 1. Base + Index

The effective address (EA) is obtained by adding the values of any two general registers %r0-31 specified.

$$EA = [reg_S1 + reg_S2]$$

### 2. Base + Displacement

The effective address (EA) is obtained by adding the value of any general register %r0-31 specified and a displacement given by the instruction's immediate value field.

$$EA = [reg_S1] + offS$$

## 3.3.2 Store Instruction Addressing

### 1. Base + Displacement

The effective address (EA) is obtained by adding the value of any general register %r0-31 specified and a displacement given by the instruction's immediate value field.

$$EA = [reg_S1] + offS$$

# 4. Instruction Set

All instructions are fixed 32-bit length.

| Category                     | Instruction          | Function                           |

|------------------------------|----------------------|------------------------------------|

| Unconditional branch         | b{,x}?               | Unconditional branch               |

|                              | bl{,x}?              | Unconditional branch to subroutine |

| Conditional branch           | bt{,x/t} S1,?        | Conditional Branch                 |

|                              | bf{,x/t} S1,?        | Conditional Branch                 |

|                              | jlr {,x} S2,D*       | Conditional branch to subroutine   |

|                              | jlrt {,x/t} S1,S2,D* | Conditional branch to subroutine   |

|                              | jlrf {,x/t} S1,S2,D* | Conditional branch to subroutine   |

|                              | rt S2                | Return from subroutine             |

| Bit test                     | btst1 S1,S2/immU,D   | Bit test                           |

|                              | btst0 S1,S2/immU,D   | Bit test                           |

| Comparison                   | cmpeq S1,S2/immS,D   | Comparison [=]                     |

|                              | cmple S1,S2/immS,D   | Comparison [signed: ≤]             |

|                              | cmplt S1,S2/immS,D   | Comparison [signed: <]             |

|                              | cmpls S1,S2/immS,D   | Comparison [unsigned: ≤]           |

|                              | cmpc S1,S2/immS,D    | Comparison [unsigned: <]           |

|                              | cmpne S1,S2/immS,D   | Comparison [≠]                     |

|                              | cmpgt S1,S2/immS,D   | Comparison [signed: >]             |

|                              | cmpge S1,S2/immS,D   | Comparison [signed: ≥]             |

|                              | cmphi S1,S2/immS,D   | Comparison [unsigned: >]           |

|                              | cmpnc S1,S2/immS,D   | Comparison [unsigned: ≥]           |

| Trap                         | trap vct             | Transfer to trap toutine           |

| Arithmetic/logical operation | add S1,S2/immS9,D    | Add                                |

|                              | sub S1,S2/immS9,D    | Subtract                           |

|                              | adc S1,S2/immS9,D    | Add with carry                     |

|                              | sbc S1,S2/immS9,D    | Subtract with carry                |

|                              | and S1,S2/immS9,D    | Logical AND                        |

|                              | or S1,S2/immS9,D     | Logical OR                         |

|                              | xor S1,S2/immS9,D    | Exclusive OR                       |

|                              | sbr S1,S2/immS12,D   | Subtract                           |

| Extend                       | extu S1,S2/immU,D    | MSB extend                         |

|                              | ext S1,S2/immU,D     | MSB extend                         |

| Shift                        | sl S1,S2/immS,D      | Logical shift                      |

|                              | rot S1,S2/immS,D     | Logical rotate                     |

|                              | slr S1,S2/immS,D     | Logical shift                      |

|                              | sar S1,S2/immS,D     | Arithmetic shift                   |

| Bit manipulation             | brst S1,S2/immU,D    | Set bit to "0"                     |

| er promote                   | bset S1,S2/immU,D    | Set bit to "1"                     |

|                              | bnot S1,S2/immU,D    | Invert bit                         |

|                              | brst %psr,4/5,%psr   | Set bit to "0"                     |

|                              | brst %psr,4/5,%psr   | Set bit to "1"                     |

| Category               | Instruction           | Function                                         |

|------------------------|-----------------------|--------------------------------------------------|

| Register-register move | mov S,D               | Move                                             |

|                        | movh S1,D'            | Move upper bits                                  |

| Store immediate value  | seti imm17S,D         | Store immediate value                            |

|                        | setih const16,D'      | Store immediate value to upper 16 bits           |

|                        | setli const25         | Store immediate value left-shifted 7 bits to %r3 |

| Store                  | sb S2/immS,[S1+offS]  | Byte store                                       |

|                        | shw S2/immS,[S1+offS] | Half-word store                                  |

|                        | sw S2/immS,[S1+offS]  | Word store                                       |

| Swap                   | swap S2,[S1+offS]     | Swap                                             |

| Load                   | lb [S1+offS],D'       | Byte load                                        |

|                        | Ihw [S1+offS],D'      | Half-word load                                   |

|                        | lw [S1+offS],D'       | Word load                                        |

| Multiplication         | mul0 S1,S2/immS,D'    | Signed multiply                                  |

|                        | mul16 S1,S2/immS,D'   | Signed multiply                                  |

|                        | mul32 S1,S2/immS,D'   | Signed multiply                                  |

|                        | mulu0 S1,S2/immS,D'   | Unsigned multiply                                |

|                        | mulu16 S1,S2/immS,D'  | Unsigned multiply                                |

|                        | mulu32 S1,S2/immS,D'  | Unsigned multiply                                |

Multiply instructions need two clocks for execution time.

The MSM7630 can only use the mul0 and mulu0 instructions of the multiplication instructions.

## 5. Exceptions, Traps, and Interrupts

The CPU core of SCP provides error exceptions, traps, external interrupts, and software traps (by trap instructions). Each type has a corresponding interrupt priority level and instruction dispatch address.

| Source                                | Vector | Branch Address | Priority | Synchronous/Asynchronous |

|---------------------------------------|--------|----------------|----------|--------------------------|

|                                       | Number |                |          | (Sense)                  |

| System reset                          |        | 0x00000000     | 0        | Asynchronous (level)     |

| CPU reset (INIT)                      | 0      | VBA+0x000      | 1        | Asynchronous (edge)      |

| Instruction access exception          | 1      | VBA+0x010      | 2        | Synchronous              |

| Instruction address invalid exception | 2      | VBA+0x020      | 3        | Synchronous              |

| Reserved instruction exception        | 3      | VBA+0x030      | 4        | Synchronous              |

| Privileged instruction exception      | 4      | VBA+0x040      | 5        | Synchronous              |

| Data address invalid exception        | 5      | VBA+0x050      | 8        | Asynchronous (edge)      |

| Data access exception                 | 6      | VBA+0x060      | 9        | Asynchronous (edge)      |

| Reserved                              | 7      | VBA+0x070      |          |                          |

| Breakpoint trap                       | 8      | VBA+0x080      | 6        | Synchronous              |

| Reserved                              | 9      | VBA+0x090      |          |                          |

|                                       | to 32  | to VBA+0x200   |          |                          |

| External interrupt 1                  | 33     | VBA+0x210      | 25       | Asynchronous (level)     |

| External interrupt 2                  | 34     | VBA+0x220      | 24       | Asynchronous (level)     |

| External interrupt 3                  | 35     | VBA+0x230      | 23       | Asynchronous (level)     |

| External interrupt 4                  | 36     | VBA+0x240      | 22       | Asynchronous (level)     |

| External interrupt 5                  | 37     | VBA+0x250      | 21       | Asynchronous (level)     |

| External interrupt 6                  | 38     | VBA+0x260      | 20       | Asynchronous (level)     |

| External interrupt 7                  | 39     | VBA+0x270      | 19       | Asynchronous (level)     |

| External interrupt 8                  | 40     | VBA+0x280      | 18       | Asynchronous (level)     |

| External interrupt 9                  | 41     | VBA+0x290      | 17       | Asynchronous (level)     |

| External interrupt 10                 | 42     | VBA+0x2a0      | 16       | Asynchronous (level)     |

| External interrupt 11                 | 43     | VBA+0x2b0      | 15       | Asynchronous (level)     |

| External interrupt 12                 | 44     | VBA+0x2c0      | 14       | Asynchronous (level)     |

| External interrupt 13                 | 45     | VBA+0x2d0      | 13       | Asynchronous (level)     |

| External interrupt 14                 | 46     | VBA+0x2e0      | 12       | Asynchronous (level)     |

| External interrupt 15                 | 47     | VBA+0x2f0      | 11       | Asynchronous (level)     |

| External interrupt 16 (NMI)           | 48     | VBA+0x300      | 10       | Asynchronous (edge)      |

| TRAP instruction                      | 0      | VBA+0x000      | 7        | Synchronous              |

|                                       | to 255 | to VBA+0xff0   |          |                          |

The system reset vector is at absolute address 0. All others are ORed with VBA as the base address. Synchronous detection is acceptance of a request within an instruction cycle.

Asynchronous detection is acceptance of a request between instruction cycles or at any point in time after.

### 5.1 RST: System Reset

A system reset resets all states under all circumstances.

Type: Asynchronous hardware reset after RST pin level detection.

Vector address: Absolute address 0 (0x00000000).

Conditions: Non-maskable (unconditional)

PL after interrupt transition: 15

5.2 IAE: Instruction Access Exception

An instruction access exception is generated when an instruction is fetched from an undefined memory space. If the instruction is converted to a NOP by delayed instruction control (x-bit manipulation), then no exception will be generated.

Type: Instruction-synchronous exception caused by memory access error during instruction fetch.

Vector number/address: Vector number = 1 / VBA + 0x010

Conditions: Non-maskable (unconditional). Invalidated by delayed instruction control (x-bit).

Saved address: Address of the instruction that caused the exception.

PL after interrupt transition: 15

5.3 IAIE: Instruction Address Invalid Exception

An instruction address invalid exception is generated when a register indirect branch instruction attempts an instruction fetch at an address that is not on a word boundary. If the instruction is converted to a NOP by delayed instruction control (x-bit manipulation), then no exception will be generated.

Type: Instruction-synchronous exception caused by an illegal JLR or RT instruction.

Vector number/address: Vector number = 2 / VBA + 0x020

Conditions: Non-maskable (unconditional). Invalidated by delayed instruction control (x-bit).

Saved address: Address of the instruction that caused the exception.

PL after interrupt transition: 15

### 5.4 PIE: Privileged Instruction Exception

A privileged instruction exception is generated when an action that can only be performed in supervisor mode attempted in user mode: (a) in user mode a privileged register is specified as a destination, or (b) in user mode a number 64 or below is specified for a TRAP instruction vector. If the instruction is converted to a NOP by delayed instruction control (x-bit manipulation), then no exception will be generated.

Type: Instruction-synchronous exception caused by an illegal privileged instruction.

Vector number/address: Vector number = 4 / VBA + 0x040

Conditions: Non-maskable (unconditional). Invalidated by delayed instruction control (x-bit).

Saved address: Address of the instruction that caused the exception.

PL after interrupt transition: 15

5.5 DAIE: Data Address Invalid Exception

A data address invalid exception is generated when a memory access instruction attempts to access a memory address not on a word boundary.

Type: Asynchronous exception caused by an illegal memory access instruction.

Vector number/address: Vector number = 5 / VBA + 0x050

Conditions: EM == 1. However, exception must be maintained until accepted.

Saved address: Address being executed when the exception was accepted.

PL after interrupt transition: 15

5.6 DAE: Data Access Exception

A data access exception is generated when data is accessed in an undefined memory space.

Type: Asynchronous exception caused by a memory access instruction error.

Vector number/address: Vector number = 6 / VBA + 0x060

Conditions: EM == 1. However, exception must be maintained until accepted.

Saved address: Address being executed when the exception was accepted.

PL after interrupt transition: 15

## 5.7 BPT: Breakpoint Trap

A breakpoint trap is generated when the instruction execution address matches the address pointed to by the %BPA register. However, the EBP bit in the %PSR register must be enabled. The instruction at the address that causes the trap will not be executed. The trap will be generated even if the instruction is converted to a NOP by delayed instruction control (x-bit manipulation).

Type: Instruction-synchronous trap caused by hardware.

Vector number / address: Vector number = 8 / VBA + 0x080

Conditions: EM == 1 && EBP == 1. Not invalidated by delayed instruction control (x-bit).

Saved address: Address pointed to by the %BPA register.

PL after interrupt transition: 15

5.8 EINT: External Interrupt 1-15

External interrupts are generated by inputs. However, an external interrupt will be accepted only when its level has higher priority than the current processor level. When an external interrupt is accepted, the processor level becomes the same as its level.

Type: Asynchronous interrupt when level on INT1-INT15 pins is detected.

Vector number/address: Vector number = 33-47 / VBA+0x210-0x2f0

Conditions: EM == 1 && PL < external\_interrupt\_number

Saved address: Address being executed when the interrupt was accepted.

PL after interrupt transition: External interrupt number

The MSM7630 assigns interrupt levels as follows. It does not use other interrupts (including NMI).

| Interrupt Source      | Priority | Interrupt Number |

|-----------------------|----------|------------------|

| User Block/TMR2       | 1        | INT11            |

| External pin (EXTINT) | 2        | INT9             |

| Serial I/O            | 3        | INT7             |

| Parallel I/O          | 4        | INT5             |

| TMR1                  | 5        | INT3             |

### 5.9 Return From Interrupt

In order to return from an interrupt process caused by an exception, external interrupt, or software trap, the pipeline at the time of the interrupt must be regenerated before execution.

There are two types of returns: (1) re-execution of an instruction that was in its execution phase at the time an exception, external interrupt, or asynchronous trap caused an interrupt, and (2) re-execution of the instruction after the instruction that was in its execution phase at the time a software trap caused an interrupt. However, if breakpoints are supported by software traps then case (1) applies.

The return sequence from an interface process is described below.

Also, an rt instruction must not be executed while the EM bit of %PSR is 1 (the state permitting overlapping interrupts). If an interrupt occurred during the rt instruction in such a case, then the contents of %PSR would be corrupted.

## 1. Resume from interrupted instruction

#### 2. Return from instruction after interrupt

```

: add %r2, 4, %r1 ; %r2+4 (old %nPC+4)\rightarrow%r1 brst %psr, 4, %psr ; EM-bit reset jlr %r2, %nop ; delay slot, branch %r2 (old %nPC), return address not saved rt %r1 ; return to %r1 (old %nPC+4), %prPSR move to %PSR

```

In this case the pNOP bit of %prPSR must be cleared in advance of rt instruction execution. If the pNOP bit of %prPSR is set and then the rt instruction is executed, then the instruction at the return point would not be executed.

#### **Bus Interface Unit**

#### 1. Features

The SCP's bus interface unit (BIU) manages address space and outputs control signals that enable optimal memory access. This allows ROM, SRAM, DRAM and other general devices to be accessed.

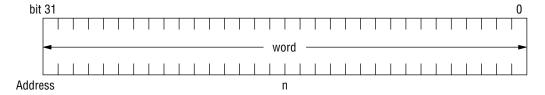

## 2. Address Space

The address space that can be directly accessed by load/store instructions is 4 gigabytes. The BIU manages this address space by dividing it into several.

## 2.1 ROM Space

ROM space is assigned to 0x000000000-0x0FFFFFFF. When this space is accessed the  $\overline{ROM}$  signal goes "L".

### 2.2 SRAM Space

SRAM space is assigned to 0x10000000-0x1FFFFFFF. When this space is accessed the SRAM signal goes "L".

### 2.3 DRAM Space

DRAM space is assigned to 0x20000000-0x2FFFFFF. When this space is accessed the DRAM controller outputs a signal required for DRAM access.

## 2.4 General Device Space

General device space is assigned to 0x40000000-0x7FFFFFFF. When this space is accessed the  $\overline{AS}$  signal goes "L". This space is used to access general devices external to the MSM7630.

### 2.5 Internal ROM Space

Internal ROM space is assigned to 0xC0000000-0xCFFFFFFF. It is used to access internal ROM.

This space is not used by the MSM7630. Accesses to this space will cause instruction access exceptions or data access exceptions.

#### 2.6 Internal RAM Space

Internal RAM space is assigned to 0xD0000000-0xDFFFFFFF. It is used to access internal RAM.

This space is not used by the MSM7630. Access to this will cause instruction access exceptions or data access exceptions.

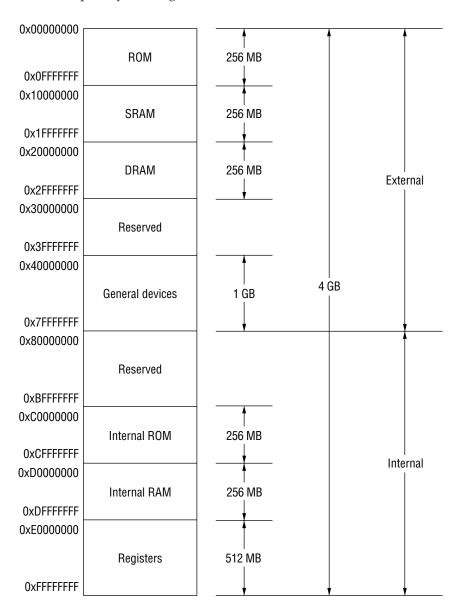

### 2.7 Register Space

Register space is assigned to 0xE0000000-0xFFFFFFF. Within this space, 0xF8000000-0xFFFFFFF is assigned for standard I/O and system registers.

#### 3. Registers

This is a register group used for bus control.

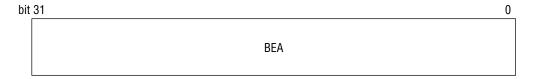

#### 3.1 BEA: Bus Error Address

This register provides the address at the time a bus error occurred.

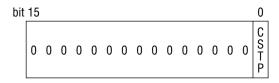

## 3.2 BSR: Bus Status Register

This register provides bus status information.

| bit 31 | 19 18 17 | 16 15       | 14 12 | 2 1 1 8 | 3 7 | 6 4 | 3 2 | 1 | 0 |

|--------|----------|-------------|-------|---------|-----|-----|-----|---|---|

|        | XSP      | C<br>S<br>P | ST    | PEB     | 0   | BES | 0 0 | Н | R |

• bit[18:17] XSP: Sleep (read/write)

When the  $\overline{STBY}$  signal is "L", these bits either stop the clock without CPU intervention (XSP = 00) or stop the clock after waiting for the CPU suspend process (XSP = 11).

• bit[16] CSP: CPU Sleep (read/write)

This bit indicates whether the CPU core is operating or suspended. Writing "1" will stop the CPU core's clock.

• bit[14:12] ST: Status (read-only)

These bits save the status signals when an access by the CPU core causes a bus error.

• bit[11:8] PEB: Parity Error Byte (read-only)

These bits provide the byte position when a parity error occurs.

• bit[6:4] BES: Bus Error Status (read-only)

These bits provide the source of a bus error.

| BES = 000 | No error                         |

|-----------|----------------------------------|

| BES = 001 | BIU register privilege violation |

| BES = 010 | Parity error                     |

| BES = 100 | Invalid space access             |

These bits will be "000" after reset.

• bit[1] H: Hold (read/write)

This bit sets whether or not bus rights will be passed upon a CPU core bus rights request. This bit will be "0" after reset.

3.3 ECR: Extra Configuration Register

This register sets bus operation.

| bit 31 | 11 | 10     | 9      | 8 | 7      | 6 | 4  | 3 | 2      | 1      | 0      |

|--------|----|--------|--------|---|--------|---|----|---|--------|--------|--------|

|        |    | 0<br>X | A<br>X | 0 | P<br>M |   | BM | А | 0<br>V | A<br>V | D<br>V |

• bit[10] OX: Internal ROM (read-only)

This bit indicates whether or not internal ROM will be accessed in 2 clocks. MSM7630 does not use this bit.

• bit[9] AX: Internal RAM (read-only)

This bit indicates whether or not internal RAM will be accessed in 2 clocks. MSM7630 does not use this bit.

• bit[7] PM: Parity Mode (read/write)

This bit sets parity.

$$PM = 0$$

Even parity  $PM = 1$  Odd parity

This bit will be "0" after reset.

MSM7630 does not use parity checking, so it ignores this field.

• bit[3] A: All Internal ROM (read/write)

This bit sets whether or not internal ROM will be accessed instead of external ROM. MSM7630 has no internal ROM, so this bit is always "0".

• bit[2] OV: Internal ROM Valid (read-only)

This bit shows whether internal ROM is enabled or disabled. This bit is "0" for MSM7630.

• bit[1] AV: Internal RAM Valid (read-only)

This bit shows whether internal RAM is enabled or disabled. This bit is "0" for MSM7630.

### 3.4 SCR: Space Configuration Register

This register sets ROM space, SRAM space, and general device space.

| bit 31 | 26 25 24 | 23 21 | 20 18 | 17 16 | 15 | 14 13 | 12 10 | 9 8 | 7      | 6 | 5  | 4 | 3 2 | 1 0 |  |

|--------|----------|-------|-------|-------|----|-------|-------|-----|--------|---|----|---|-----|-----|--|

|        |          |       |       |       |    |       |       |     |        |   |    |   |     |     |  |

| <br>   | A A      | ARW   | AWW   | AS    | 0  | 0 0   | ORW   | OS  | D<br>S | P | SD | х | WT  | SZ  |  |

| I<br>I |          |       |       |       |    |       |       |     |        |   |    |   |     |     |  |

• bit[25] AC: SRAM Parity Check (read/write)

This bit sets parity checking of SRAM space. It will be "0" after reset.

AC = 0 Ignore parity checks.

AC = 1 Generate a bus error if a parity error is detected.

• bit[24] AD: SRAM Dummy Cycle (read/write)

This bit sets whether or not SRAM space may be accessed continuously after ROM space or DRAM space has been read.

AD = 0 Continuous access allowed.

AD = 1 Open an interval of at least one clock.

This bit will be "1" after reset.

• bit[23:21] ARW: SRAM Read Wait (read/write)

These bits set the wait count when SRAM space is accessed by a read.

| ARW = 000 | 2τ access (1 wait)    |

|-----------|-----------------------|

| ARW = 001 | 3τ access (2 waits)   |

| ARW = 010 | 4τ access (3 waits)   |

| ARW = 011 | 5τ access (4 waits)   |

| ARW = 100 | 6τ access (5 waits)   |

| ARW = 101 | 8τ access (7 waits)   |

| ARW = 110 | 10τ access (9 waits)  |

| ARW = 111 | 12τ access (11 waits) |

|           |                       |

These bits will be "111" after reset.

• bit[20:18] AWW: SRAM Write Wait (read/write)

These bits set the wait count when SRAM space is accessed by a write.

```

AWW = 000 \qquad 2\tau \ access \ (1 \ wait)

AWW = 001 \qquad 3\tau \ access \ (2 \ waits)

AWW = 010 \qquad 4\tau \ access \ (3 \ waits)

AWW = 011 \qquad 5\tau \ access \ (4 \ waits)

AWW = 100 \qquad 6\tau \ access \ (5 \ waits)

AWW = 101 \qquad 8\tau \ access \ (7 \ waits)

AWW = 110 \qquad 10\tau \ access \ (9 \ waits)

AWW = 111 \qquad 12\tau \ access \ (11 \ waits)

```

These bits will be "111" after reset.

• bit[17:16] AS: SRAM Device Size (read/write)

These bits set the device size of SRAM space.

| AS = 00 | No SRAM (space is invalid) |

|---------|----------------------------|

| AS = 01 | 8-bit wide device          |

| AS = 10 | 16-bit wide device         |

| AS = 11 | 32-bit wide device         |

These bits will be "00" after reset. When this field is "00", attempting to access SRAM space will cause an instruction access exception or data access exception.

• bit[14] OC: ROM Parity Check (read/write)

This bit sets parity checking for ROM space. It will be "0" after reset.

```

OC = 0 Ignore parity errors.

OC = 1 Generate a bus error if a parity error is detected.

```

This bit will be "0" for the MSM7630.

• bit[13] OD: ROM Dummy Cycle (read/write)

This bit sets whether or not a ROM space access will immediately follow an SRAM space or DRAM space read.

```

OD = 0 Consecutive access enabled.

OD = 1 Force an interval of at least one clock.

```

This bit will be "1" after reset.

• bit[12:10] ORW: ROM Read Wait (read/write)

These bits set the wait count when ROM space is accessed by a read.

```

\begin{array}{lll} \text{ORW} = 000 & 2\tau \, \text{access} \, (1 \, \text{wait}) \\ \text{ORW} = 001 & 3\tau \, \text{access} \, (2 \, \text{waits}) \\ \text{ORW} = 010 & 4\tau \, \text{access} \, (3 \, \text{waits}) \\ \text{ORW} = 011 & 5\tau \, \text{access} \, (4 \, \text{waits}) \\ \text{ORW} = 100 & 6\tau \, \text{access} \, (5 \, \text{waits}) \\ \text{ORW} = 101 & 8\tau \, \text{access} \, (7 \, \text{waits}) \\ \text{ORW} = 110 & 10\tau \, \text{access} \, (9 \, \text{waits}) \\ \text{ORW} = 111 & 12\tau \, \text{access} \, (11 \, \text{waits}) \end{array}

```

These bits will be "111" after reset.

• bit[9:8] OS: ROM Device Size (read/write)

These bits set the device size of ROM space.

| OS = 00 | No ROM (space is invalid) |

|---------|---------------------------|

| OS = 01 | 8-bit wide device         |

| OS = 10 | 16-bit wide device        |

| OS = 11 | 32-bit wide device        |

When this field is "00", attempting to access ROM space will cause an instruction access exception or data access exception.

• bit[7] DS: Other Data Setup (read/write)

This bit sets whether or not the data setup time to the write strobe signal  $\overline{WR}$  is guaranteed during writes to general device space.

```

DS = 0 Not guaranteed.

DS = 1 Guaranteed.

```

This bit will be "1" after reset.

• bit[6] PC: Other Parity Check (read/write)

This bit sets parity checking for general device space. It will be "0" after reset.

```

PC = 0 Ignore parity errors.

PC = 1 Generate a bus error if a parity error is detected.

```

This bit will be "0" for the MSM7630.

• bit[5] SD: Other Dummy Cycle (read/write)

This bit sets whether or not a general device space access will immediately follow an SRAM space or DRAM space read.

SD = 0 Consecutive access enabled.

SD = 1 Force an interval of at least one clock.

This bit will be "1" after reset.

• bit[4] X: External Bus Clock Unit (read/write)

This bit sets the operating clock unit for general device space.

X = 0 Use 1 clock as the unit. X = 1 Use 2 clocks as the unit.

This bit will be "0" after reset.

• bit[3:2] WT: Other Wait (read/write)

These bits set the wait count when general device space is accessed.

| WT = 00 | 4τ access |

|---------|-----------|

| WT = 01 | 5τ access |

| WT = 10 | 6τ access |

| WT = 11 | 7τ access |

These bits will be "11" after reset.

• bit[1:0] SZ: Other Device Size (read/write)

These bits set the device size of general device space.

| SZ = 00 | No general device (space is invalid) |

|---------|--------------------------------------|

| SZ = 01 | 8-bit wide device                    |

| SZ = 10 | 16-bit wide device                   |

| SZ = 11 | 32-bit wide device                   |

These bits will be "11" after reset. When this field is "00", attempting to access general device space will cause an instruction access exception or data access exception.

### 3.5 DRAM: DRAM Configuration Register

This register sets DRAM space.

| bit 31 | 29 | 28 27 | 26     | 25 24 | 23     | 22 21 | 20 18 | 17 16 | 15 13 | 12 11 | 10     | 9   | 0 |

|--------|----|-------|--------|-------|--------|-------|-------|-------|-------|-------|--------|-----|---|

|        |    |       |        |       |        |       |       |       |       |       | Ь      |     |   |

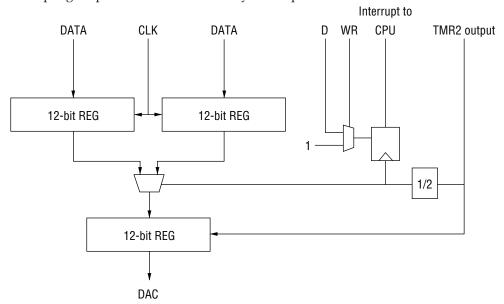

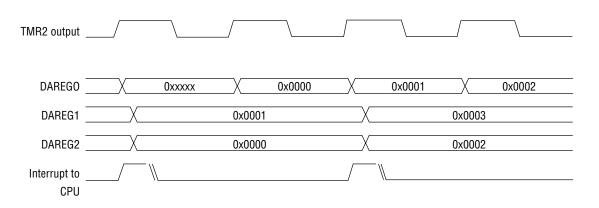

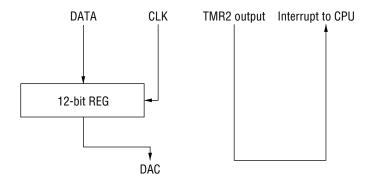

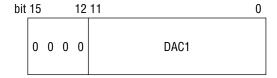

| 0 0    | 0  | DT    | E<br>M | TP    | D<br>P | MD    | RA    | cs    | CA    | SZ    | F<br>M | RFC |   |