**PEDL2308DIGEST-03** Issue Date: Dec. 27, 2004

# Preliminary

Stereo Recording/Playback LSI with Built-in Buffer Memory

**OKI Semiconductor**

Both a serial interface and a parallel interface are available with the ML2308 through the use of a pin switch. Refer to pages 3 to 16 for information on the serial interface, and pages 17 to 24 for information on the parallel interface.

Also, common information such as command functions, operation flow and examples of applied circuits are described on page 25 and subsequent pages.

# **GENERAL DESCRIPTION**

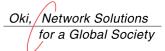

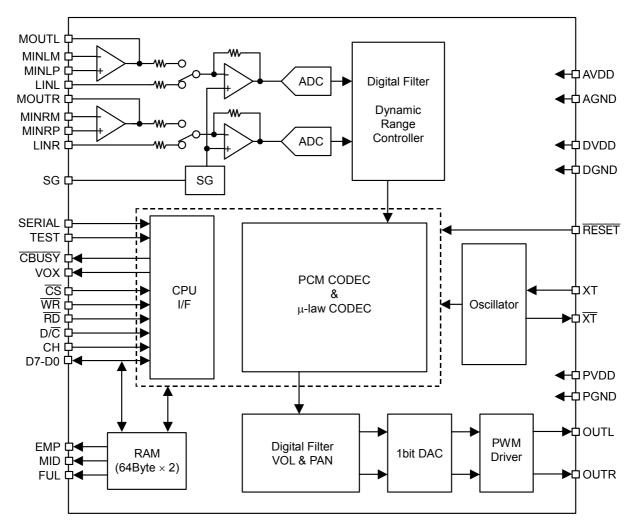

The ML2308 is a stereo recording/playback LSI that has integrated in a single chip all the functions required for recording and playing back audio data.

Analog signals fed into the microphone or line inputs are converted into digital signals by the analog to digital converter, and output to external equipment via the buffer memory. Further, digital signals from external equipment are converted into PWM signals by the 1-bit digital to analog converter, and output by the PWM driver that can directly drive the headphones. The influence of noise is lower with the ML2308 when compared with the mixed analog LSI, since most of the signals are digitally processed inside the LSI.

# FEATURES

User Interfaces

- Supports Serial Peripheral Interface (SPI) or 8-bit bus interface

- Buffer memory for audio data buffer: 128 bytes (64 bytes each for left and right channels)

- Buffer memory status output pins FUL, MID, EMP

Codec section/audio input and output sections

• Audio synthesis method:

μ-law G.711compliant 8-bit PCM, 8-bit/16-bit linear PCM, 8-bit Oki non-linear PCM, 2-bit/3-bit/5-bit/5-bit/6-bit/7-bit/8-bit ADPCM2

- Sampling frequency: 4.0 kHz to 32 kHz (selectable with commands)

- Built-in stereo  $\Delta$ - $\Sigma$  type 1-bit A/D converter S/(N+D): 80 dB DR, S/N: 85 dB

- Built-in stereo  $\Delta$ - $\Sigma$  type 1-bit D/A converter S/(N+D): 75 dB DR, S/N: 85 dB

- Built-in PWM driver for driving a speaker (150mW max,  $RL = 16\Omega$ , at BTL)

- Microphone amplifier  $\times 2$ , Line amplifier  $\times 2$  (Stereo)

- Dynamic Range Control (DRC) automatic recording level adjustment function

- Recording input level detect function

#### Control commands

- Volume control : 256 steps, 0 dB to -48.16 dB, OFF

- PAN control : 16 steps, 0 dB to -24.08 dB, OFF

- Power supply voltage : +2.7 V to +3.6 V

- Operating temperature  $:-20^{\circ}C$  to  $+70^{\circ}C$

- Source oscillation frequency : 24.576MHz

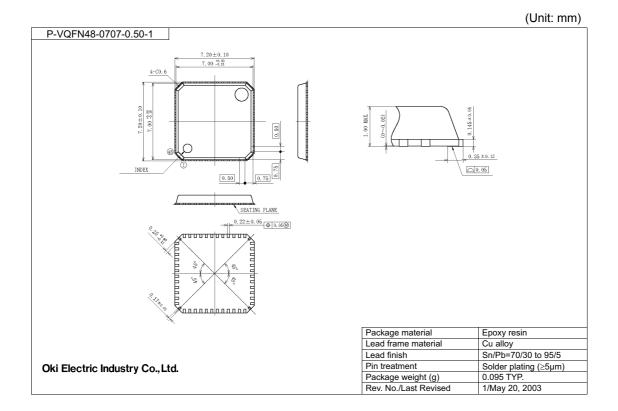

- Package : 48-pin plastic QFN (P-VQFN48-0707-0.50) (ML2308GD)

#### TABLE OF CONTENTS

| General Description                                                                   |    |

|---------------------------------------------------------------------------------------|----|

| Features                                                                              | 1  |

| (1) SERIAL INTERFACE                                                                  | 3  |

| BLOCK DIAGRAM                                                                         |    |

| PIN CONFIGURATION (TOP VIEW)                                                          |    |

| description of Pins                                                                   |    |

| When Placing an Order                                                                 |    |

| ABSOLUTE MAXIMUM RATINGS                                                              |    |

| RECOMMENDED OPERATING CONDITIONS                                                      | 9  |

| ELECTRICAL CHARACTERISTICS                                                            | 9  |

| DC Characteristics                                                                    | 9  |

| Analog Section Characteristics                                                        |    |

| Description of Functions                                                              | 11 |

| Command Interface                                                                     | 11 |

| 1. SPI mode                                                                           |    |

| 2. Command Data Write Timing                                                          | 13 |

| 3. Status Read Timing                                                                 |    |

| Audio Interface                                                                       | 14 |

| 1. At I <sup>2</sup> S Formatting                                                     | 14 |

| 2. At Front-Aligned MSB First Formatting                                              |    |

| 3. Data Configurations for Respective Audio Synthesis Methods                         | 16 |

|                                                                                       |    |

| (2) Parallel Interface                                                                |    |

| Block diagram                                                                         |    |

| PIN CONFIGURATION (TOP VIEW)                                                          |    |

| Description of pins                                                                   |    |

| When Placing an Order                                                                 |    |

| ABSOLUTE MAXIMUM RATINGS                                                              |    |

| RECOMMENDED OPERATING CONDITIONS                                                      |    |

| ELECTRICAL CHARACTERISTICS                                                            |    |

| DC Characteristics                                                                    |    |

| Analog Section Characteristics                                                        | 24 |

|                                                                                       | 05 |

| (3) Common to Serial and parallel interfaces                                          | 25 |

| description of functions                                                              |    |

| Relationship between Source oscillation frequency and Sampling Frequency              | 25 |

| Audio Synthesis Methods                                                               |    |

| Restriction of Sampling Frequency                                                     |    |

| Buffer Memory Configuration                                                           |    |

| Command Functions                                                                     |    |

| Command List                                                                          |    |

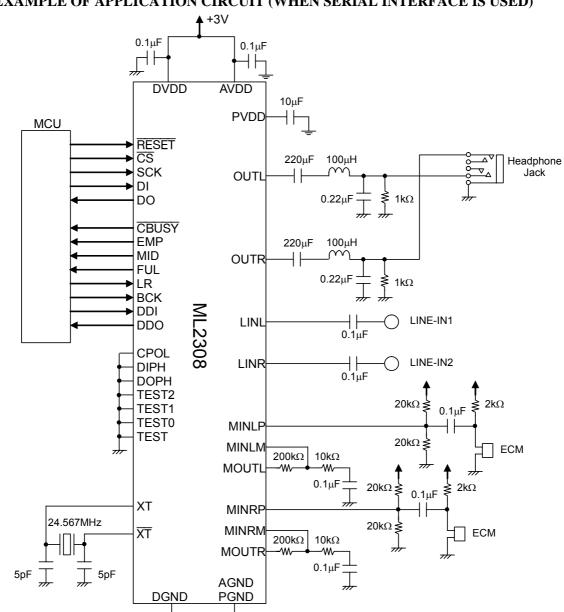

| Power Supply Wiring<br>EXAMPLE Of APPLICATION CIRCUIT (when serial interface is used) |    |

| PACKAGE DIMENSIONS                                                                    |    |

|                                                                                       |    |

| Revision History                                                                      | 31 |

#### (1) SERIAL INTERFACE

#### **BLOCK DIAGRAM**

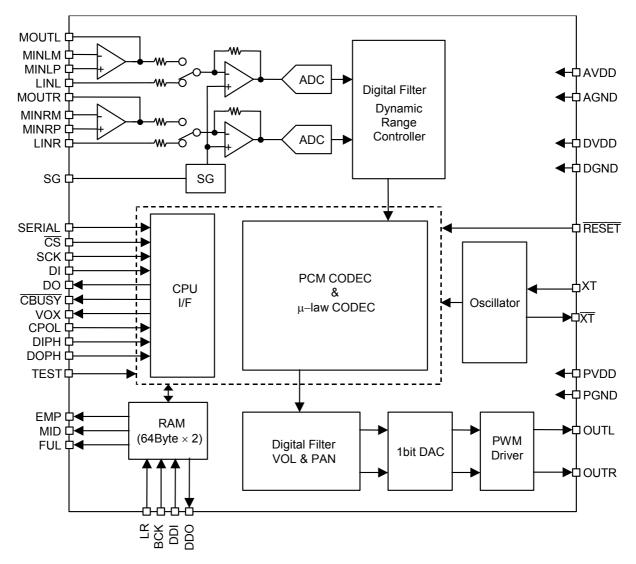

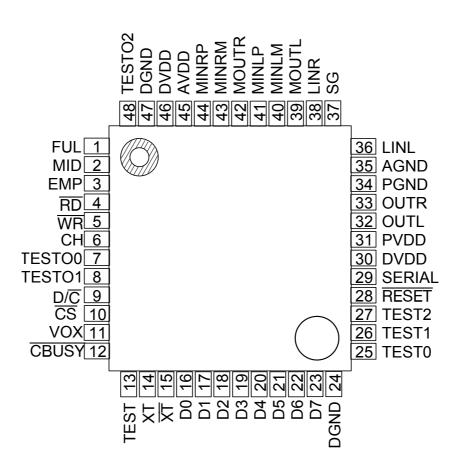

# PIN CONFIGURATION (TOP VIEW)

#### 48-pin plastic VQFN (Serial interface)

# **DESCRIPTION OF PINS**

| Command Inter | face Related P | ins |                                                                                                                                                                                                                                                                                                                                                                                        |

|---------------|----------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin number    | Pin name       | I/O | Description                                                                                                                                                                                                                                                                                                                                                                            |

| 28            | RESET          | I   | The reset input pin. At "L" level input, the LSI is initialized. At that time, oscillation is stopped and the power is shut off. When turning the power on, input at the "L" level, and change to the "H" level once the supplied power voltage has been stabilized.                                                                                                                   |

| 29            | SERIAL         | I   | The parallel/serial interface select pin.<br>Fixed to "H" level when the serial interface is selected.                                                                                                                                                                                                                                                                                 |

| 10            | CS             | I   | The chip select input pin. At "L" level input, the command interface for the SCK, DI, and DO pins is enabled. It's unable to use $\overline{CS}$ pin fixed "L" level. CS pin should be "H" level after transferring 8bits command data.                                                                                                                                                |

| 9             | SCK            | I   | The command data input and status output serial clock input pin.                                                                                                                                                                                                                                                                                                                       |

| 8             | DI             | I   | The command data serial data input pin.                                                                                                                                                                                                                                                                                                                                                |

| 7             | DO             | 0   | The serial data output pin. The status signal in the LSI is output as a serial data, when a command is input subsequently following the input of the RDSTAT command.                                                                                                                                                                                                                   |

| 4             | CPOL           | Ι   | The pin to select the input pulse polarity of the SCK pin.<br>When the CPOL pin is at the "L" level, the SCK will become "H" active.<br>When the CPOL pin is at the "H" level, the SCK will become "L" active.                                                                                                                                                                         |

| 5             | DIPH           | I   | The edge of the SCK pulse, at which data input at the DI pin is taken in<br>the LSI, is selected with this pin.<br>When the DIPH pin is at the "L" level, the data input at the DI pin is taken<br>in the LSI at the rising edge of the SCK pulse.<br>When the DIPH pin is at the "H" level, the data input at the DI pin is taken<br>in the LSI at the falling edge of the SCK pulse. |

| 6             | DOPH           | I   | The edge of the SCK pulse, at which data is output to the DO pin, is selected with this pin.<br>When the DOPH pin is at the "L" level, data is output to the DO pin at the falling edge of the SCK pulse.<br>When the DOPH pin is at the "H" level, data is output to the DO pin at the rising edge of the SCK pulse.                                                                  |

| 12            | CBUSY          | 0   | This pin outputs data at "L" level during command processing.<br>Commands should be input with the CBUSY pin at the "H" level.                                                                                                                                                                                                                                                         |

| 11            | VOX            | 0   | The audio level detect signal output pin for recording. After recording has started, this pin outputs "H" once the recording input signal amplitude reaches the prescribed level.                                                                                                                                                                                                      |

#### PEDL2308DIGEST-03

#### **OKI** Semiconductor

# ML2308

| Pin number | Pin name | I/O | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|------------|----------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 17         | LR       | Ι   | This pin inputs the left or right side channel select signal for writing the audio data in the buffer memory or reading the audio data from the buffer memory.<br>The outputs of the respective status signals in the buffer memory (EMP, MID and FUL) are switched by the input level of the LR pin input. Note that the status signal of the buffer memory is an output of a channel status signal that is opposite to that of the selected channel.<br>[I <sup>2</sup> S format selected]<br>When the LR pin is at the "L" level, access to the buffer memory of the left side will be permitted. The status signal of the buffer memory of the right side will be output.<br>When the LR pin is at the "H" level, access to the buffer memory of the right side will be permitted. The status signal of the buffer memory of the right side will be permitted. The status signal of the buffer memory of the left side will be output.<br>[Front-aligned MSB first format selected]<br>When the LR pin is at the "L" level, access to the buffer memory of the right side will be output.<br>[Front-aligned MSB first format selected]<br>When the LR pin is at the "L" level, access to the buffer memory of the left side will be output.<br>[Front-aligned MSB first format selected]<br>When the LR pin is at the "L" level, access to the buffer memory of the left side will be permitted. The status signal of the buffer memory of the left side will be permitted. The status signal of the buffer memory of the left side will be output. |

| 18         | BCK      | I   | The serial clock input pin for buffer memory input and output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 19         | DDI      | Ι   | This is the pin for the input of serial data to the buffer memory. Data is taken into the LSI at the rising edge of the BCK clock.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 20         | DDO      | 0   | This is the pin for the output of serial data from the buffer memory. Data is output serially at the falling edge of the BCK clock.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 1          | FUL      | 0   | The status signal, indicating that the entire buffer memory is full of data,<br>will be output. A "H" active or "L" active selection can be made with the<br>OPT command.<br>Recorded data after the buffer memory becomes full is not stored in the<br>buffer memory and is discarded.<br>Therefore, any data written after the buffer memory becomes full will not<br>be played back.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 2          | MID      | 0   | The status signal, indicating that at least half of the buffer memory is filled with data, will be output. A "H" active or "L" active selection can be made with the OPT command.<br>Ordinarily, access to the buffer memory is controlled by the output of the MID pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 3          | EMP      | 0   | The status signal, indicating that there is no data in the entire buffer memory, will be output. A "H" active or "L" active selection can be made with the OPT command.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Analog, Clock o<br>Pin number | Pin name | I/O | Description                                                                                                                                                |

|-------------------------------|----------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 39                            | MOUTL    | 0   | The output pin of the microphone amplifier on the left side.                                                                                               |

| 40                            | MINLM    | Ι   | The inverted input pin of the microphone amplifier on the left side.                                                                                       |

| 41                            | MINLP    | Ι   | The non-inverted input pin of the microphone amplifier on the left side.                                                                                   |

| 42                            | MOUTR    | 0   | The output pin of the microphone amplifier on the right side.                                                                                              |

| 43                            | MINRM    | Ι   | The inverted input pin of the microphone amplifier on the right side.                                                                                      |

| 44                            | MINRP    | Ι   | The non-inverted input pin of the microphone amplifier on the right side.                                                                                  |

| 36                            | LINL     | I   | The input pin of the line amplifier on the left side.                                                                                                      |

| 38                            | LINR     | Ι   | The input pin of the line amplifier on the right side.                                                                                                     |

| 37                            | SG       | 0   | The output pin for the reference voltage (signal ground) of the analog circuit.                                                                            |

| 33                            | OUTR     | 0   | The playback output pin for the right side. An external LC filter has been configured to eliminate a high-frequency component, as the PWM pulse is output. |

| 32                            | OUTL     | 0   | The playback output pin for the left side. An external LC filter has been configured to eliminate a high-frequency component, as the PWM pulse is output.  |

| 14                            | ХТ       | I   | An oscillator connection pin. When using an external clock, input it from this pin.                                                                        |

| 15                            | XT       | 0   | An oscillator connection pin. When using an external clock, leave this open.                                                                               |

| 25,26,27                      | TEST2-0  | I   | Test pins. Keep these pins "L" level, as these pins don't have pull-up resistors.                                                                          |

| 13                            | TEST     | I   | A test pin. Fix it at "L". It has a built-in pull-down resistor                                                                                            |

| 16,21,22,<br>23,48            | TESTO4-0 | 0   | Test pins. Leave them open when the circuit board is connected.                                                                                            |

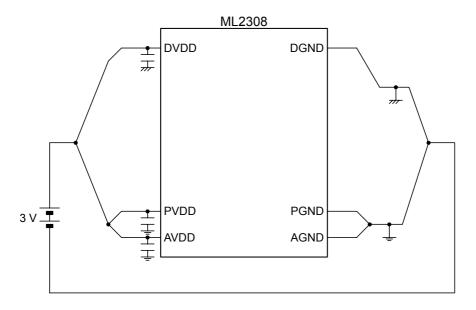

| 30,46                         | DVDD     | _   | The digital power supply pins. Connect a bypass capacitor of $0.1\mu$ F or more between these pins and the DGND pin.                                       |

| 24,47                         | DGND     | _   | The digital ground pins.                                                                                                                                   |

| 45                            | AVDD     |     | The analog power supply pin. Connect a bypass capacitor of $0.1\mu$ F or more between this pin and the AGND pin.                                           |

| 35                            | AGND     |     | The analog ground pin.                                                                                                                                     |

| 31                            | PVDD     | _   | The power supply pin for the PWM driver. Connect a bypass capacitor of $10\mu$ F or more between this pin and the PGND pin.                                |

|                               | PGND     |     | The ground pin for the PWM driver.                                                                                                                         |

#### Analog, Clock or Power Supply Related Pins

# WHEN PLACING AN ORDER

Specify ML2308GD (Package: 48-pin plastic VQFN).

#### ABSOLUTE MAXIMUM RATINGS

| Parameter            | Symbol           | Condition         | Rating                        | Unit |

|----------------------|------------------|-------------------|-------------------------------|------|

| Power supply voltage | V <sub>DD</sub>  | Ta = 25°C         | –0.3 to +5.0                  | V    |

| Input voltage        | V <sub>IN</sub>  |                   | -0.3 to V <sub>DD</sub> + 0.3 | V    |

| Power Dissipation    | PD               | Ta = 25°C         | 890                           | mW   |

| Output abort ourrapt |                  | Ta = 25°C(Note 1) | 10                            | mA   |

| Output short current | I <sub>SC</sub>  | Ta = 25°C(Note 2) | 100                           | mA   |

| Storage temperature  | T <sub>STG</sub> | _                 | -55 to +150                   | °C   |

Notes: 1. Applies to output pins excluding OUTL and OUTR pins.

2. Applies to OUTL and OUTR pins.

# **RECOMMENDED OPERATING CONDITIONS**

| Parameter              | Symbol           | Condition         | Range      | Unit |

|------------------------|------------------|-------------------|------------|------|

| Power supply voltage   | V <sub>DD</sub>  | DGND = AGND = 0 V | 2.7 to 3.6 | V    |

| Operating temperature  | T <sub>op</sub>  | —                 | –20 to +70 | °C   |

| Source clock frequency | f <sub>OSC</sub> | —                 | 20 to 25   | MHz  |

# **ELECTRICAL CHARACTERISTICS**

#### **DC Characteristics**

DV<sub>DD</sub> = AV<sub>DD</sub> = 2.7 to 3.6 V DGND = AGND = 0 V. Ta = -20 to +70°C

|                               |                  |                                             | DGN                        | ID = AGND = 0 | 0 V, Ta = -20        | 10 + 10 C |

|-------------------------------|------------------|---------------------------------------------|----------------------------|---------------|----------------------|-----------|

| Parameter                     | Symbol           | Condition                                   | Min.                       | Тур.          | Max.                 | Unit      |

| "H" input voltage             | VIH              | —                                           | $V_{\text{DD}} \times 0.8$ |               | V <sub>DD</sub> +0.3 | V         |

| "L" input voltage             | VIL              | —                                           | -0.3                       |               | 0.6                  | V         |

| "H" output voltage            | V <sub>OH</sub>  | I <sub>ОН</sub> = –1 mA                     | $V_{DD} - 0.4$             |               |                      | V         |

| "L" output voltage            | V <sub>OL</sub>  | I <sub>OL</sub> = 2 mA                      |                            |               | 0.4                  | V         |

| "H" input current (Note 1)    | I <sub>IH1</sub> | $V_{IH} = V_{DD}$                           |                            |               | 10                   | μA        |

| "H" input current (Note 2)    | I <sub>IH2</sub> | $V_{IH} = V_{DD}$                           | 0.3                        |               | 20                   | μA        |

| "H" input current (Note 3)    | I <sub>IH3</sub> | $V_{IH} = V_{DD}$                           | 30                         |               | 180                  | μA        |

| "H" input current (Note 4)    | $I_{IL1}$        | V <sub>IL</sub> = GND                       | -10                        | _             | —                    | μA        |

| "L" input current (Note 2)    | I <sub>IL2</sub> | V <sub>IL</sub> = GND                       | -20                        |               | -0.3                 | μA        |

| Operating current consumption | I <sub>DD</sub>  | f <sub>OSC</sub> = 24.576 MHz at<br>no load |                            | 30            | 40                   | mA        |

| Current consumption           |                  | Ta = –20 to +50°C                           |                            |               | 20                   | μA        |

| during power down             | I <sub>DDS</sub> | Ta = +50 to +70°C                           |                            |               | 100                  | μA        |

Notes: 1. Applies to input pins excluding XT and TEST pins.

2. Applies to XT pin.

3. Applies to TEST pin.

4. Applies to input pins excluding XT pin.

#### **OKI** Semiconductor

# ML2308

# **Analog Section Characteristics**

#### DVDD = AVDD = 2.7 to 3.6 V DGND = AGND = 0 V. Ta = -20 to $+70^{\circ}$ C

|                                           |                   |                                                          | DGND              | = AGND = 0 \  | /, Ta = –20 to   | +70°C |

|-------------------------------------------|-------------------|----------------------------------------------------------|-------------------|---------------|------------------|-------|

| Parameter                                 | Symbol            | Condition                                                | Min.              | Тур.          | Max.             | Unit  |

| MIN input impedance                       | R <sub>INM</sub>  | —                                                        | 1                 |               |                  | MΩ    |

| LINL, LINR input impedance                | R <sub>INL</sub>  | When line input<br>is used                               | 22                | 32            | 42               | kΩ    |

| LIN1, LIN2 input amplitude                | V <sub>LIN</sub>  | —                                                        | —                 | _             | $0.6 \times VDD$ | Vpp   |

| MOUT, LOUTL, LOUTR output load resistance | R <sub>OUTA</sub> | _                                                        | 100               | _             | _                | kΩ    |

| Microphone amplifier gain setting range   | G <sub>MIC</sub>  | —                                                        | —                 | _             | 30               | dB    |

| SG output voltage                         | $V_{SG}$          | _                                                        | $0.48 \times VDD$ | 0.5 	imes VDD | 0.52 ×<br>VDD    | V     |

| SG output resistance                      | R <sub>SG</sub>   | —                                                        | 12                | 15            | 18               | kΩ    |

| OUTL, OUTR output power                   | P <sub>OUT</sub>  | At BTL output<br>RL = $16\Omega$<br>S/(N+D) $\geq$ -20dB | _                 | _             | 150              | mW    |

#### **DESCRIPTION OF FUNCTIONS**

#### **Command Interface**

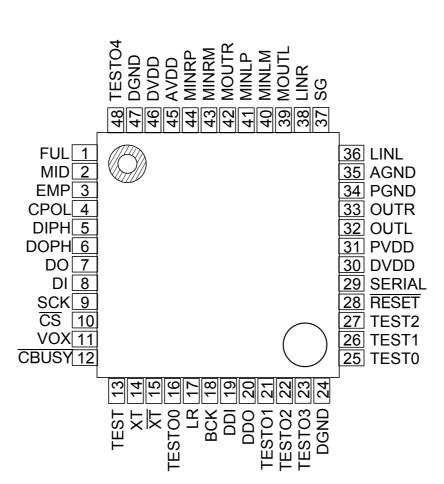

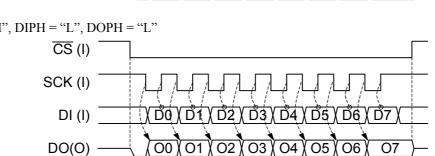

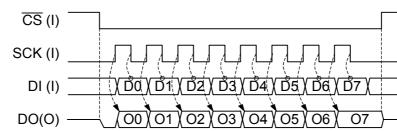

#### 1. SPI mode

The ML2308 supports eight types of SPI modes as available command interface modes. These SPI modes can be selected with the CPOL pin, DIPH pin and DOPH pin. Fix the output level to "L" or "H" as the SPI mode setting cannot be changed once the power has been turned on.

Setting descriptions for the CPOL pin, DIPH pin and DOPH pin are shown below:

| Pin       | Input Level | Setting descriptions                                                           |  |  |  |  |

|-----------|-------------|--------------------------------------------------------------------------------|--|--|--|--|

| CPOL      | "L" level   | "H" pulse is input as the SCK pulse.                                           |  |  |  |  |

| "H" level |             | "L" pulse is input as the SCK pulse.                                           |  |  |  |  |

| DIPH      | "L" level   | The input data of the DI pin is taken in at the rising edge of the SCK pulse.  |  |  |  |  |

| "H" level |             | The input data of the DI pin is taken in at the falling edge of the SCK pulse. |  |  |  |  |

| DOPH      | "L" level   | Data is output to the DO pin at the falling edge of the SCK pulse.             |  |  |  |  |

| DOPH      | "H" level   | Data is output to the DO pin at the rising edge of the SCK pulse.              |  |  |  |  |

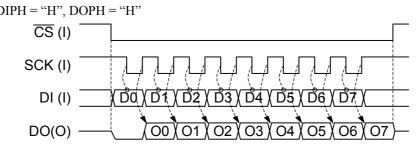

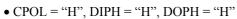

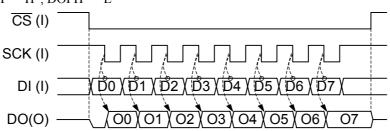

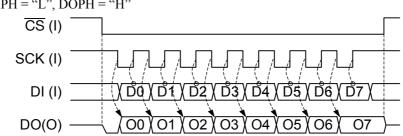

Timing diagrams of respective SPI modes are shown below:

• CPOL = "H", DIPH = "H", DOPH = "L"

• CPOL = "L", DIPH = "H", DOPH = "H"

PEDL2308DIGEST-03

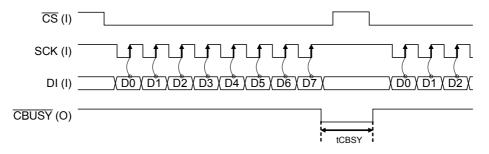

# 2. Command Data Write Timing

The timing for writing command data is shown below.

After "L" is input to the CS pin, 8-bit command data is input to the DI pin serially from the LSB, synchronized with the input clock signal of the SCK pin. After 8 SCK clock signals have been input, "L" is output to the CBUSY pin. While the CBUSY pin is "L", the serial interface cannot be used. It waits for the CBUSY pin output to become "H" before inputting the next command data. Please change CS pin to "H" level after one command inputted.

A timing diagram for the case where the CPOL pin is set at the "H" level and the DIPH pin is set at "L" level is shown below.

The "L" level output time of the CBUSY pin, tCBSY, varies depending on the operating state of the LSI.

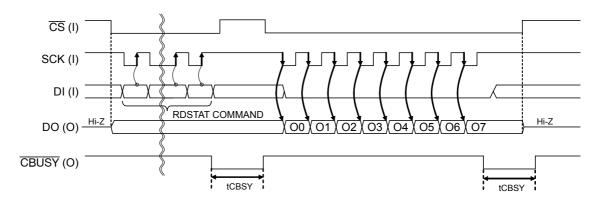

#### 3. Status Read Timing

The timing for reading status signals is shown below.

After "L" is input to the CS pin and the status read command (RDSTAT command) is input, 8-bit status data is output to the DO pin serially from the LSB synchronized with the falling edge of the input clock signal of the SCK pin.

A timing diagram for the case where the CPOL pin is set at the "H" level, the DIPH pin at "L" level, and the "DOPH" at the "L" level is shown below.

#### **Audio Interface**

The audio interface is used to write the audio data into and read the audio data out of the buffer memory during recording and playback.

As an audio interface, the ML2308 supports two types of interface formats (I<sup>2</sup>S format and front-aligned MSB first format).

Access to the buffer memory is made from the LR pin, BCK pin, DDI pin and DDO pin regardless of the selected format.

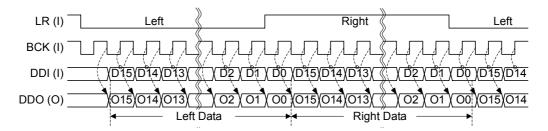

#### 1. At I<sup>2</sup>S Formatting

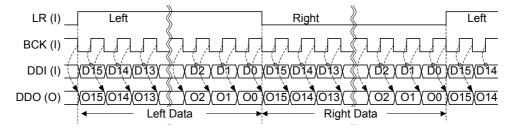

Access timing to the buffer memory with the I<sup>2</sup>S format is shown below:

During playback, the 16-bit playback data is input serially from the MSB to the DDI pin in synchronization with the clock signal of the BCK pin. The DDI pin input data is taken in the LSI at the rising edge of the BCK clock signal. The recording data is output from the DDO pin at the falling edge of the BCK clock signal during recording.

The left side data is input and output when the level of the LR pin is at "L" and the right side data is input and output when the level of the LR pin is at "H".

The status signal output (EMP, MID and FUL) of the buffer memory is also switched according to the input level of the LR pin. The right side status data is output when the level of the LR pin is at "L" and the left side status signal is output when the level is at "H". Note that the status of the opposite chanel is output when compared with the input and output of the data.

When the buffer memory is empty, the read data will be 0000h (hexadecimal) if reading is performed.

If the BCK clock signal is input for the duration of 16 clocks or more while the LR pin is at "H" or "L", then the 16-bit front-aligned data will become valid data.

The buffer memory access timing, when the BCK clock is 16-bit or more, is shown below:

It is necessary to access both the left and right sides of the buffer memory during monaural recording and playback as well. Since buffer memory access of an unused channel will be ignored, there will be no effect to the channels that are in use. The status signal of an unused channel retains the empty state, even for the status signals of the buffer meory (EMP, MID and FUL) as well.

For example, when recording with the left side channel, the audio data read from the right side channel will be 0000h (hexadecimal). When playing back, the values written in the right side of the buffer memroy will be ignored.

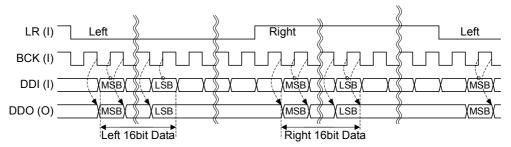

#### 2. At Front-Aligned MSB First Formatting

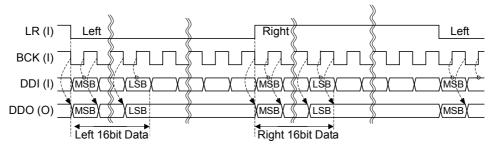

The buffer memory access timing for the front-aligned MSB first format is shown below:

During playback, the 16-bit playback data is input serially from the MSB to the DDI pin in synchronization with the clock signal of the BCK pin. The DDI pin input data is taken in the LSI at the rising edge of the BCK clock signal. The recording data is output from the DDO pin at the falling edge of the BCK clock signal during recording.

The left side data is input and output when the level of the LR pin is at "H" and the right side data is input and output when the level of the LR pin is at "L".

The status signal output (EMP, MID and FUL) of the buffer memory is also switched according to the input level of the LR pin. The right side status data is output when the level of the LR pin is at "H" and the left side status signal is output when the level is at "L". Note that the status of the opposite chanel is output when compared with the input and output of the data.

When the buffer memory is empty, the read data will be 0000h (hexadecimal) if reading is performed.

If the BCK clock signal is input for the duration of 16 clocks or more while the LR pin is at "H" or "L", then the 16-bit front-aligned data will become valid data.

The buffer memory access timing, when the BCK clock is 16-bit or more, is shown below:

It is necessary to access both the left and right sides of the buffer memory during monaural recording and playback as well. Since buffer memory access of an unused channel will be ignored, there will be no effect to the channels that are in use. The status signal of an unused channel retains the empty state, even for the status signals of the buffer memory (EMP, MID and FUL) as well.

For example, when recording with the left side channel, the audio data read from the right side channel will be 0000h (hexadecimal). When playing back, the values written in the right side of the buffer memroy will be ignored.

#### 3. Data Configurations for Respective Audio Synthesis Methods

The configuration of the audio data that is input to and output from the buffer memory during recording and playback, for each respective audio synthesis method, is shown in the table below:

| 1) 2-bit ADPCM2 method        |           |               |             |             |             |             |            |            |

|-------------------------------|-----------|---------------|-------------|-------------|-------------|-------------|------------|------------|

| ,                             | D15       | D14           | D13         | D12         | D11         | D10         | D9         | D8         |

|                               | MSB1      | LSB1          | MSB2        | LSB2        | MSB3        | LSB3        | MSB4       | LSB4       |

|                               | D7        | D6            | D5          | D4          | D3          | D2          | D1         | D0         |

|                               | MSB5      | LSB5          | MSB6        | LSB6        | MSB7        | LSB7        | MSB8       | LSB8       |

|                               |           |               |             |             |             |             |            |            |

| 2) 3-bit AD                   | PCM2 met  | hod           |             |             |             |             |            |            |

|                               | D15       | D14           | D13         | D12         | D11         | D10         | D9         | D8         |

|                               | 0         | MSB1          | 2SB1        | LSB1        | MSB2        | 2SB2        | LSB2       | MSB3       |

|                               | D7        | D6            | D5          | D4          | D3          | D2          | D1         | D0         |

|                               | 2SB3      | LSB3          | MSB4        | 2SB4        | LSB4        | MSB5        | 2SB5       | LSB5       |

|                               |           |               |             |             |             |             |            |            |

| 3) 4-bit AD                   |           |               | -           | -           |             | -           |            |            |

|                               | D15       | D14           | D13         | D12         | D11         | D10         | D9         | D8         |

|                               | MSB1      | 3SB1          | 2SB1        | LSB1        | MSB2        | 3SB2        | 2SB2       | LSB2       |

|                               | D7        | D6            | D5          | D4          | D3          | D2          | D1         | D0         |

|                               | MSB3      | 3SB3          | 2SB3        | LSB3        | MSB4        | 3SB4        | 2SB4       | LSB4       |

| 0.51.40                       |           | 1 1           |             |             |             |             |            |            |

| 4) 5-bit AD                   |           |               | D12         | D12         | D11         | D10         | DO         | 00         |

|                               | D15<br>0  | D14<br>MSB1   | D13<br>4SB1 | D12<br>3SB1 | D11<br>2SB1 | D10<br>LSB1 | D9<br>MSB2 | D8<br>4SB2 |

|                               |           |               |             |             |             |             |            |            |

|                               | D7        | D6            | D5          | D4          | D3          | D2          | D1         | D0         |

|                               | 3SB2      | 2SB2          | LSB2        | MSB3        | 4SB3        | 3SB3        | 2SB3       | LSB3       |

| 5) 6-bit AD                   | PCM2 met  | hod           |             |             |             |             |            |            |

| <i>c) c c c c c c c c c c</i> | D15       | D14           | D13         | D12         | D11         | D10         | D9         | D8         |

|                               | 0         | 0             | 0           | 0           | MSB1        | 5SB1        | 4SB1       | 3SB1       |

|                               | D7        | D6            | D5          | D4          | D3          | D2          | D1         | D0         |

|                               | 2SB1      | LSB1          | MSB2        | 5SB2        | 4SB2        | 3SB2        | 2SB2       | LSB2       |

|                               |           |               |             |             |             |             |            |            |

| 6) 7-bit AD                   | PCM2 met  | hod           |             |             |             |             |            |            |

|                               | D15       | D14           | D13         | D12         | D11         | D10         | D9         | D8         |

|                               | 0         | 0             | MSB1        | 6SB1        | 5SB1        | 4SB1        | 3SB1       | 2SB1       |

|                               | D7        | D6            | D5          | D4          | D3          | D2          | D1         | D0         |

|                               | LSB1      | MSB2          | 6SB2        | 5SB2        | 4SB2        | 3SB2        | 2SB2       | LSB2       |

|                               |           |               |             |             |             |             |            |            |

| 7) 8-bit AD                   | PCM2, 8-b | it straight l | PCM, 8-bit  | non-linear  | PCM, or µ   | ı-law PCM   | I method   |            |

|                               | D15       | D14           | D13         | D12         | D11         | D10         | D9         | D8         |

|                               | MSB1      | 7SB1          | 6SB1        | 5SB1        | 4SB1        | 3SB1        | 2SB1       | LSB1       |

|                               | D7        | D6            | D5          | D4          | D3          | D2          | D1         | D0         |

|                               | MSB2      | 7SB2          | 6SB2        | 5SB2        | 4SB2        | 3SB2        | 2SB2       | LSB2       |

|                               |           |               |             |             |             |             |            |            |

| 8) 16-bit str                 |           |               |             |             |             |             |            |            |

|                               | D15       | D14           | D13         | D12         | D11         | D10         | D9         | D8         |

|                               | MSB1      | 15SB1         | 14SB1       | 13SB1       | 12SB1       | 11SB1       | 10SB1      | 9SB1       |

|                               | D7        | D6            | D5          | D4          | D3          | D2          | D1         | D0         |

This concludes the descriptions on the serial interface. Refer to Section (3) for details concerning common items, such as command lists, operation flows and examples of applied circuits.

4SB1

3SB1

2SB1

LSB1

5SB1

6SB1

7SB1

8SB1

#### (2) PARALLEL INTERFACE

# **BLOCK DIAGRAM**

# **PIN CONFIGURATION (TOP VIEW)**

48-pin plastic VQFN (Parallel interface)

# **DESCRIPTION OF PINS**

| Pin number | Pin name | I/O | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|------------|----------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 28         | RESET    | I   | The reset input pin. At "L" level input, the LSI is initialized. At that time, oscillation is stopped and the power is shut off. When turning the power on, input at the "L" level, and change to the "H" level once the supplied power voltage has been stabilized.                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 29         | SERIAL   | Ι   | The CPU interface select pin.<br>The level is fixed to "L" when the parallel interface is selected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 10         | CS       | Ι   | The select input pin for the command interface and the audio interface.<br>The $\overline{WR}$ and $\overline{RD}$ inputs are accepted at the "L" level. The $\overline{WR}$ and $\overline{RD}$ signal inputs are ignored at the "H" level.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 9          | D/C      | I   | The select input pin for the command interface and the audio interface.<br>The level of the $D/\overline{C}$ pin is set to "L" and the "L" pulse is input to the $\overline{WF}$ and $\overline{RD}$ pins when inputting a command or outputting the internal status.<br>The audio interface becomes enabled when the level is at "H".                                                                                                                                                                                                                                                                                                                                                                                             |

| 5          | WR       | I   | The write pulse input pin. This pin is used in common by the command interface and the audio interface.<br>[The "L" level selected for the $D/\overline{C}$ pin]<br>The input data of the D7 to D0 pins is taken into the LSI as command data at the rising edge of the WR pin. Once the command data is taken in, the "L" level is output to the $\overline{CBUSY}$ pin, indicating that a command process is taking place.<br>A "L" level command input of the $\overline{CBUSY}$ pin will be ignored. The command is input while the level of the $\overline{CBUSY}$ pin is at "H".<br>[The "H" level selected for the $D/\overline{C}$ pin]<br>Refer to the descriptions on the audio interface related pins on the next page. |

| 4          | RD       | I   | The read pulse input pin. This pin is used in common by the command interface and the audio interface.<br>[The "L" level selected for the $D/\overline{C}$ pin]<br>Status data is output to the D7 to D0 pins while the level of the $\overline{RD}$ pin is at "L".<br>In order to read the internal status, the level of the $\overline{RD}$ pin is set to "L" after the input of the RDSTAT command.<br>Note that the status data will not be updated unless the RDSTAT command has been input.<br>[The "H" level selected for the $D/\overline{C}$ pin]<br>Refer to the descriptions on the audio interface related pins on the next page.                                                                                      |

| 16-23      | D7-D0    | I/O | Data is input or output with the bi-directional data bus.<br>These pins are used in common by the command interface and the audic<br>interface.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 12         | CBUSY    | 0   | This pin outputs data at "L" level during command processing. Commands can be input when the CBUSY pin is at the "H" level.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 11         | VOX      | 0   | The audio level detect signal output pin for recording. After recording has started, this pin outputs "H" once the recording input signal amplitude reaches the prescribed level.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

#### **OKI** Semiconductor

ML2308

|            | Audio Interface Related Pins |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

|------------|------------------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Pin number | Pin name                     | I/O | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| 10         | CS                           | I   | The select input pin for the command interface and the audio interface.<br>The $\overline{WR}$ and $\overline{RD}$ inputs are accepted when set to the "L" level. The $\overline{WR}$ and $\overline{RD}$ signal inputs are ignored when set to the "H" level.                                                                                                                                                                                                                                                                                |  |  |  |

| 9          | D/C                          | I   | The select input pin for the command interface and the audio interface.<br>When the audio data is input or output, the level of the $D/\overline{C}$ pin is set to "H" and the "L" level pulse is input to the $\overline{WR}$ and $\overline{RD}$ pins.<br>The command interface is enabled when the level is at "L".                                                                                                                                                                                                                        |  |  |  |

| 6          | СН                           | I   | The select input pin for the audio interface channel.<br>When the level is at "L", the buffer memory of the left side is selected and<br>the buffer memory status of the left side is output as status output of the<br>EMP, MID and FUL pins.<br>When the level is at "H", the buffer memory of the right side is selected and<br>the buffer memory status of the right side is output as status output of the<br>EMP, MID and FUL pins.                                                                                                     |  |  |  |

| 5          | WR                           | I   | The write pulse input pin. This pin is used in common by the command interface and the audio interface.<br>[The "H" level selected for the $D/\overline{C}$ pin]<br>The input data of the D7 to D0 pins are written into the buffer memory, which has been selected with the CH pin, at the rising edge of the $\overline{WR}$ pin.<br>The state of the $\overline{CS}$ pin is irrelevant.<br>[The "L" level selected for the $D/\overline{C}$ pin]<br>Refer to the descriptions on the command interface related pins on the preceding page. |  |  |  |

| 4          | RD                           | I   | The read pulse input pin. This pin is used in common by the command interface and the audio interface.<br>[The "H" level selected for the $D/\overline{C}$ pin]<br>While the level of the $\overline{RD}$ pin is at "L", the data read from the buffer memory, which has been selected with the CH pin, is output to the D7 to D0 pins.<br>[The "L" level selected for the $D/\overline{C}$ pin]<br>Refer to the descriptions on the command interface related pins on the preceding page.                                                    |  |  |  |

| 16-23      | D7-D0                        | I/O | Data is input or output with the bi-directional data bus.<br>These pins are used in common by the command interface and the audio<br>interface.                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| 1          | FUL                          | 0   | The status signal, indicating that the entire buffer memory is full of data, will be output. A "H" active or "L" active selection can be made with the OPT command.<br>Recordings made after the buffer memory becomes full are not stored in the buffer memory and are discarded.<br>Therefore, any data written after the buffer memory becomes full, will not be played back.                                                                                                                                                              |  |  |  |

| 2          | MID                          | 0   | The status signal, indicating that at least half of the buffer memory is filled with data, will be output. A "H" active or "L" active selection can be made with the OPT command.<br>Ordinarily, access to the buffer memory is controlled by the output of the MID pin.                                                                                                                                                                                                                                                                      |  |  |  |

| 3          | EMP                          | 0   | The status signal, indicating that there is no data in the entire buffer memory, will be output. A "H" active or "L" active selection can be made with the OPT command.                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

# Audio Interface Related Pins

| Pin number | Pin name | I/O | Description                                                                                                                                                        |  |  |  |

|------------|----------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 39         | MOUTL    | 0   | The output pin of the microphone amplifier on the left side.                                                                                                       |  |  |  |

| 40         | MINLM    | Ι   | The inverted input pin of the microphone amplifier on the left side.                                                                                               |  |  |  |

| 41         | MINLP    | Ι   | The non-inverted input pin of the microphone amplifier on the left side.                                                                                           |  |  |  |

| 42         | MOUTR    | 0   | The output pin of the microphone amplifier on the right side.                                                                                                      |  |  |  |

| 43         | MINRM    | Ι   | The inverted input pin of the microphone amplifier on the right side.                                                                                              |  |  |  |

| 44         | MINRP    | Ι   | The non-inverted input pin of the microphone amplifier on the right side.                                                                                          |  |  |  |

| 36         | LINL     | I   | The input pin of the line amplifier on the left side.                                                                                                              |  |  |  |

| 38         | LINR     | I   | The input pin of the line amplifier on the right side.                                                                                                             |  |  |  |

| 37         | SG       | 0   | The output pin for the reference voltage (signal ground) of the analog circuit.                                                                                    |  |  |  |

| 33         | OUTR     | ο   | This is the playback output pin for the right side. An external LC filter has been configured to eliminate a high-frequency component, as the PWM pulse is output. |  |  |  |

| 32         | OUTL     | 0   | This is the playback output pin for the left side. An external LC filter has been configured to eliminate a high-frequency component, as the PWM pulse is output.  |  |  |  |

| 14         | хт       | I   | An oscillator connection pin. When using an external clock, input it from this pin.                                                                                |  |  |  |

| 15         | ΧT       | ο   | An oscillator connection pin. When using an external clock, leave this open.                                                                                       |  |  |  |

| 25, 26, 27 | TEST2-0  | I   | Test pins. Keep these pins "L" level, as these pins don't have pull-up resistors.                                                                                  |  |  |  |

| 13         | TEST     | I   | A test pin. Fix it at "L". It has a built-in pull-down resistor                                                                                                    |  |  |  |

| 7, 8, 48   | TESTO2-0 | 0   | Test pins. Leave them open when the circuit board is connected.                                                                                                    |  |  |  |

| 30, 46     | DVDD     | _   | The digital power supply pins. Connect a bypass capacitor of $0.1 \mu F$ or more between these pins and the DGND pin.                                              |  |  |  |

| 24, 47     | DGND     | _   | The digital ground pins.                                                                                                                                           |  |  |  |

| 45         | AVDD     |     | The analog power supply pin. Connect a bypass capacitor of $0.1\mu F$ or more between this pin and the AGND pin.                                                   |  |  |  |

| 35         | AGND     |     | The ground supply pin.                                                                                                                                             |  |  |  |

| 31         | PVDD     | _   | The power supply pin for the PWM driver. Connect a bypass capacitor of $10\mu$ F or more between this pin and the PGND pin.                                        |  |  |  |

| 34         | PGND     |     | The ground pin for the PWM driver.                                                                                                                                 |  |  |  |

#### Analog, Clock or Power Supply Related Pins

# WHEN PLACING AN ORDER

Specify ML2308GD (Package: 48-pin plastic VQFN).

#### **ABSOLUTE MAXIMUM RATINGS**

| Parameter            | Symbol           | Condition         | Rating                        | Unit |

|----------------------|------------------|-------------------|-------------------------------|------|

| Power supply voltage | V <sub>DD</sub>  | Ta = 25°C         | –0.3 to +5.0                  | V    |

| Input voltage        | V <sub>IN</sub>  | —                 | -0.3 to V <sub>DD</sub> + 0.3 | V    |

| Power Dissipation    | PD               | Ta = 25°C         | 890                           | mW   |

| Output abort ourrant |                  | Ta = 25°C(Note 1) | 10                            | mA   |

| Output short current | ISC              | Ta = 25°C(Note 2) | 100                           | mA   |

| Storage temperature  | T <sub>STG</sub> | —                 | –55 to +150                   | °C   |

Notes: 1. Applies to output pins excluding OUTL and OUTR pins.

2. Applies to OUTL and OUTR pins.

# **RECOMMENDED OPERATING CONDITIONS**

| Parameter              | Symbol          | Condition         | Range      | Unit |

|------------------------|-----------------|-------------------|------------|------|

| Power supply voltage   | V <sub>DD</sub> | DGND = AGND = 0 V | 2.7 to 3.6 | V    |

| Operating temperature  | T <sub>op</sub> | —                 | –20 to +70 | °C   |

| Source clock frequency | fosc            | _                 | 20 to 25   | MHz  |

# **ELECTRICAL CHARACTERISTICS**

#### **DC** Characteristics

$DV_{DD}$  =  $AV_{DD}$  = 2.7 to 3.6 V DGND = AGND = 0 V, Ta = -20 to  $+70^{\circ}$ C

|                               |                  |                                             |                            |      | o , , ,              | 0 10 0 |

|-------------------------------|------------------|---------------------------------------------|----------------------------|------|----------------------|--------|

| Parameter                     | Symbol           | Condition                                   | Min.                       | Тур. | Max.                 | Unit   |

| "H" input voltage             | VIH              | —                                           | $V_{\text{DD}} \times 0.8$ |      | V <sub>DD</sub> +0.3 | V      |

| "L" input voltage             | VIL              | _                                           | -0.3                       |      | 0.6                  | V      |

| "H" output voltage            | V <sub>OH</sub>  | I <sub>ОН</sub> = –1 mA                     | $V_{DD} - 0.4$             |      |                      | V      |

| "L" output voltage            | V <sub>OL</sub>  | I <sub>OL</sub> = 2 mA                      | _                          |      | 0.4                  | V      |

| "H" input current (Note 1)    | I <sub>IH1</sub> | $V_{IH} = V_{DD}$                           |                            |      | 10                   | μA     |

| "H" input current (Note 2)    | I <sub>IH2</sub> | $V_{IH} = V_{DD}$                           | 0.3                        | _    | 20                   | μA     |

| "H" input current (Note 3)    | I <sub>IH3</sub> | $V_{IH} = V_{DD}$                           | 30                         |      | 150                  | μA     |

| "H" input current (Note 4)    | $I_{IL1}$        | V <sub>IL</sub> = GND                       | -10                        |      |                      | μA     |

| "L" input current (Note 2)    | I <sub>IL2</sub> | V <sub>IL</sub> = GND                       | -20                        |      | -0.3                 | μA     |

| Operating current consumption | I <sub>DD</sub>  | f <sub>OSC</sub> = 24.576 MHz at<br>no load | _                          | 30   | 40                   | mA     |

| Current consumption           |                  | Ta = –20 to +50°C                           | _                          | _    | 20                   | μA     |

| during power down             | I <sub>DDS</sub> | Ta = +50 to +70°C                           |                            |      | 100                  | μA     |

Applies to input pins excluding XT and TEST pins.

Applies to XT pin. Notes:

3. Applies to TEST pin.

4. Applies to input pins excluding XT pin.

#### **OKI** Semiconductor

# ML2308

# **Analog Section Characteristics**

$DV_{DD} = AV_{DD} = 2.7 \text{ to } 3.6 \text{ V}$ DGND = AGND = 0 V. Ta = -20 to +70°C