Preliminary This version: Sep. 2000

# **OKI** Semiconductor **MSM6779B**

# 160-DOT SEGMENT DRIVER (TCP)

# GENERAL DESCRIPTION

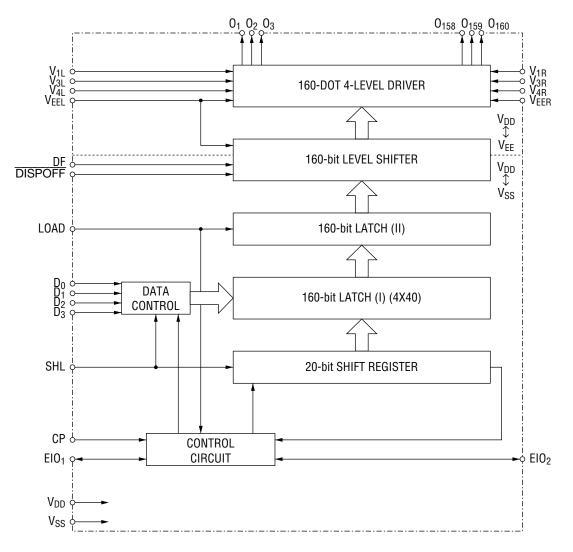

The MSM6779B is a LCD dot matrix segment driver. Fabricated in CMOS technology, the device consists of 160-bit latches I and II, a 160-bit level shifter, and a 4-level driver. The MSM6779B latches the 4-bit parallel display data sent from a microcontroller or a LCD controller to generate a LCD driving signal. This MSM6779B has a power-save function that sets all the drivers except one to the low supply current status (I<sub>DD</sub> SBY).

This driver's 3V-operation allows significant reduction in current consumption, suitable for battery-driving. The bias voltage to specify a drive level can be supplied externally. The MSM6779B can be used for various types of LCD panels.

# **FEATURES**

- Logic supply voltage

- LCD drive voltage

- : 2.7 V to 5.5 V

- : A wide range from 14 V to 28 V

- Applicable LCD duty : 1/64 to 1/256

- The bias voltage can be supplied externally.

- LCD outputs : 160

- A power-save function to reduce power consumption in a large-screen LCD panel.

- A 4-bit parallel data transfer to reduces its transfer speed to 1/4 of conventional serial transfer, providing low power consumption.

- Data transfer clock frequency : 6.5 MHz

- 35mm-wide-film TCP Tin-plating User area

: 8 mm

#### MSM6779B

# **BLOCK DIAGRAM**

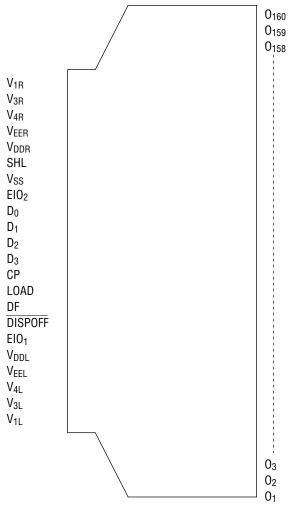

# **PIN CONFIGURATION (TOP VIEW)**

Note: The drawing shown does not specify the exact outline of the TCP; it only specifies the pin layout.

# **ABSOLUTE MAXIMUM RATINGS**

| Parameter           | Symbol                              | Condition | Rating                       | Unit |

|---------------------|-------------------------------------|-----------|------------------------------|------|

| Supply Voltage (1)  | V <sub>DD</sub>                     | Ta=25°C   | -0.3 to 6.5                  | V    |

| Supply Voltage (2)  | V <sub>DD</sub> –V <sub>EE</sub> *1 | Ta=25°C   | 0 to 30                      | V    |

| Input Voltage       | VI                                  | Ta=25°C   | -0.3 to V <sub>DD+</sub> 0.3 | V    |

| Storage Temperature | T <sub>STG</sub>                    |           | -30 to +85                   | °C   |

\*1  $V_1 > V_3 > V_4 > V_{EE}$ ,  $V_{DD} \ge V_1 > V_3 \ge V_{DD} - 10$  V,  $V_{EE} + 10$   $V \ge V_4 > V_{EE}$  $V_1 = V_{1L} = V_{1R}$ ,  $V_3 = V_{3L} = V_{3R}$ ,  $V_4 = V_{4L} = V_{4R}$ ,  $V_{EE} = V_{EEL} = V_{EER}$

# **RECOMMENDED OPERATING CONDITIONS**

| Parameter             | Symbol                              | Condition | Range      | Unit |

|-----------------------|-------------------------------------|-----------|------------|------|

| Supply Voltage (1)    | V <sub>DD</sub>                     | —         | 2.7 to 5.5 | V    |

| Supply Voltage (2)    | V <sub>DD</sub> –V <sub>EE</sub> *1 | —         | 14 to 28   | V    |

| Operating Temperature | Тор                                 | —         | -20 to +75 | °C   |

\*1  $V_1 > V_3 > V_4 > V_{EE}$ ,  $V_{DD} \ge V_1 > V_3 \ge V_{DD} - 7$  V,  $V_{EE} + 7$   $V \ge V_4 > V_{EE}$  $V_1 = V_{1L} = V_{1R}$ ,  $V_3 = V_{3L} = V_{3R}$ ,  $V_4 = V_{4L} = V_{4R}$ ,  $V_{EE} = V_{EEL} = V_{EER}$

Note: Unlike mold packages, TCP has a low light resistance. Therefore, they are protected from light.

**MSM6779B**

# **ELECTRICAL CHARACTERISTICS**

#### **DC Characteristics**

|                              |                 |                                                                                               | V to 5.5 V,          | / to 5.5 V, Ta=-20 to +75°C) |                     |      |

|------------------------------|-----------------|-----------------------------------------------------------------------------------------------|----------------------|------------------------------|---------------------|------|

| Parameter                    | Symbol          | Condition                                                                                     | Min.                 | Тур.                         | Max.                | Unit |

| "H" level Input Voltage      | VIH             | *1                                                                                            | 0.8 V <sub>DD</sub>  |                              | —                   | V    |

| "L" level Input Voltage      | VIL             | *1                                                                                            |                      |                              | 0.2 V <sub>DD</sub> | V    |

| "H" level Input Current      | IIH             | V <sub>I</sub> =V <sub>DD</sub> , V <sub>DD</sub> =5.5 V *1                                   |                      | _                            | 1                   | μA   |

| "L" level Input Current      | Ι <sub>ΙL</sub> | V <sub>I</sub> =0 V, V <sub>DD</sub> =5.5 V *1                                                |                      |                              | -1                  | μA   |

| "H" level output Voltage     | V <sub>OH</sub> | I <sub>0</sub> =-0.2 mA, V <sub>DD</sub> =2.7 V *2                                            | V <sub>DD</sub> -0.4 | _                            | _                   | V    |

| "L" level output Voltage     | V <sub>OL</sub> | I <sub>0</sub> =0.2 mA, V <sub>DD</sub> =2.7 V *2                                             |                      |                              | 0.4                 | V    |

| ON Resistance                | R <sub>ON</sub> | $V_{DD}-V_{EE}=25 V,$                                                                         |                      | 1.5                          | 3.0                 | kΩ   |

|                              |                 | V <sub>DD</sub> =2.7 V,                                                                       |                      |                              |                     |      |

|                              |                 | I V <sub>N</sub> -V <sub>0</sub>  =0.25 V *3 *4                                               |                      |                              |                     |      |

| Stand-by Current Consumption | I <sub>DD</sub> | f <sub>CP</sub> =6.5 MHz, V <sub>DD</sub> =3.0 V                                              |                      |                              | 300                 | μA   |

|                              | SBY             | V <sub>DD</sub> –V <sub>EE</sub> =25 V,<br>No load *5, f <sub>LOAD</sub> =21.6kHz             |                      |                              |                     |      |

| Current Consumption (1)      | I <sub>DD</sub> | f <sub>CP</sub> =6.5 MHz, V <sub>DD</sub> =3.0 V                                              |                      | _                            | 1.5                 | mA   |

|                              |                 | V <sub>DD</sub> –V <sub>EE</sub> =25 V,<br>No load *6, f <sub>LOAD</sub> =21.6kHz             |                      |                              |                     |      |

| Current Consumption (2)      | I <sub>EE</sub> | f <sub>CP</sub> =6.5 MHz, V <sub>DD</sub> =3.0 V                                              | _                    | _                            | 2.0                 | mA   |

|                              |                 | V <sub>DD</sub> –V <sub>EE</sub> =25 V,<br>No load *7, f <sub>LOAD</sub> =21.6kHz             |                      |                              |                     |      |

| Current Consumption (3)      | Iv              | f <sub>CP</sub> =6.5 MHz, V <sub>DD</sub> =3.0 V                                              | _                    | _                            | ±200                | μA   |

|                              |                 | V <sub>DD</sub> –V <sub>EE</sub> =25 V,<br>No load <sup>*8</sup> , f <sub>LOAD</sub> =21.6kHz |                      |                              |                     |      |

| Input Capacitance            | CI              | f=1 MHz                                                                                       | —                    | 5                            |                     | pF   |

\*1 Applicable to LOAD, CP, D<sub>0</sub>~D<sub>3</sub>, EIO<sub>1</sub>, EIO<sub>2</sub>, SHL, DF, DISPOFF pins

\*2 Applicable to EIO<sub>1</sub>, EIO<sub>2</sub> pins

\*3  $V_N=V_{DD}$  to  $V_{EE}$ ,  $V_4=14/16$  ( $V_{DD}-V_{EE}$ ),  $V_3=2/16$  ( $V_{DD}-V_{EE}$ ),  $V_{DD}=V_1$

- \*4 Applicable to  $O_1$  to  $O_{160}$  pins

- \*5 Display data 1010.....f<sub>DF</sub> = 45 Hz, Current from V<sub>DD</sub> to V<sub>SS</sub> when the display data is not fetching.

- \*6 Display data 1010..... $f_{DF}$  = 45 Hz, Current from  $V_{DD}$  to  $V_{SS}$  when the display data is fetching.

- \*7 Display data 1010.....f<sub>DF</sub> = 45 Hz, Current from  $V_{DD}$  to  $V_{EE}$

- \*8 Display data 1010.... $f_{DF}$  = 45 Hz, Current on V<sub>1</sub>, V<sub>3</sub>, and V<sub>4</sub> pins.

$V_1 = V_{IL} = V_{IR}, V_3 = V_{3L} = V_{3R}, V_4 = V_{4L} = V_{4R}, V_{EE} = V_{EEL} = V_{EER}$

Note: The above values are quaranteed when TCP is protected from light.

#### MSM6779B

|                                                 |                                 |                       | (V <sub>DD</sub> =2.7V to 5.5 V, Ta=-20 to +75°C) |      |      |      |

|-------------------------------------------------|---------------------------------|-----------------------|---------------------------------------------------|------|------|------|

| Parameter                                       | Symbol                          | Condition             | Min.                                              | Тур. | Max. | Unit |

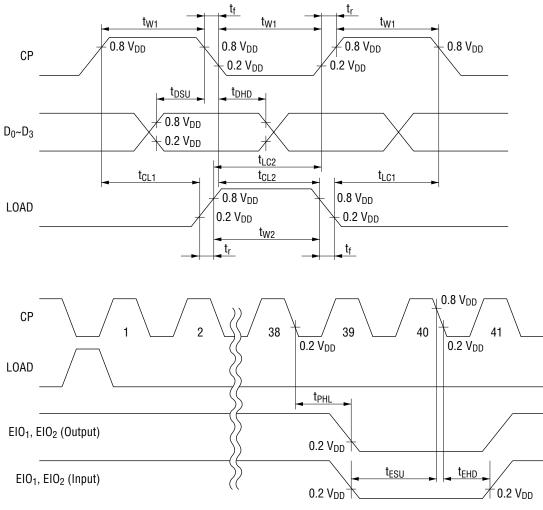

| Clock Frequency                                 | f <sub>CP</sub>                 | DUTY=50%              |                                                   | _    | 6.5  | MHz  |

| Clock Pulse Width                               | tw1                             | _                     | 56                                                |      | _    | ns   |

| Load Pulse Width                                | t <sub>W2</sub>                 | —                     | 70                                                |      | _    | ns   |

| Clock Pulse Rise/Fall Time                      | t <sub>r</sub> , t <sub>f</sub> | _                     |                                                   |      | 20   | ns   |

| Data Set-up Time                                | t <sub>DSU</sub>                | _                     | 50                                                | _    | _    | ns   |

| Data Hold Time                                  | t <sub>DHD</sub>                | _                     | 40                                                | _    | _    | ns   |

| Clock Load Time 1                               | t <sub>CL1</sub>                | _                     | 0                                                 | _    | _    | ns   |

| Clock Load Time 2                               | t <sub>CL2</sub>                | —                     | 65                                                | _    | _    | ns   |

| Load Clock Time 1                               | t <sub>LC1</sub>                | _                     | 65                                                | _    | —    | ns   |

| Load Clock Time 2                               | t <sub>LC2</sub>                | _                     | 65                                                | _    | _    | ns   |

| Propagation Delay Time                          | t <sub>PHL</sub>                | C <sub>L</sub> =15 pF |                                                   | _    | 236  | ns   |

| EIO <sub>1</sub> , EIO <sub>2</sub> Set-up Time | t <sub>ESU</sub>                | _                     | 50                                                | _    | _    | ns   |

| EIO <sub>1</sub> , EIO <sub>2</sub> Hold Time   | t <sub>EHD</sub>                | —                     | 50                                                | _    |      | ns   |

#### **Switching Characteristics**

Note: The above values are quaranteed when TCP is protected from light.

# FUNCTIONAL DESCRIPTION

#### **Pin Descriptions**

#### $V_{DD}, V_{SS}$

Power supply for the device.  $V_{DD}$  is set to 2.7 V to 5.5 V.  $V_{SS}$  is set to 0 V.

# $V_{1L}, V_{1R}, V_{3L}, V_{3R}, V_{4L}, V_{4R}, V_{EEL}, V_{EER}$

Bias power supply for the LCD drive voltages. Power supply should be  $V_{DD} \ge V_1 > V_3 > V_4 > V_{EE}$ .

#### DISPOFF

Input for controlling the output level of  $O_1$  to  $O_{160}$ . The  $V_1$  level is output from  $O_1$  to  $O_{160}$  pins during "L" level input. Refer to Truth Table.

# DF

Input for LCD drive wave form AC synchronization.

# O<sub>1</sub>~O<sub>160</sub>

LCD drive outputs that correspond to each bit of the latch (II). Depending on the combination of the contents of the latch (display data) and DF signal, one of 4 levels ( $V_1$ ,  $V_3$ ,  $V_4$ ,  $V_{EE}$ ) is output. Refer to Truth Table.

#### СР

Clock pulse input for display data reading. Data is taken into the latch (I) at the falling edge of the clock pulse.

Use an even number for the clock number per line (the number of the clock pulses during the period from Load input to the next Load input).

# EIO<sub>1</sub>, EIO<sub>2</sub>

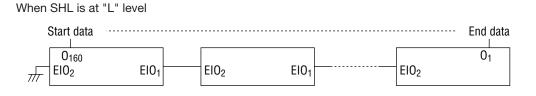

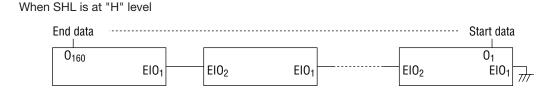

Chip Select Signal Input/Output. Input/Output are controlled by the SHL input. If the SHL input at "L"level, $EIO_1$  is output and  $EIO_2$  is input. If the SHL input is at "H" level, $EIO_1$  is input and  $EIO_2$  is output. If the SHL is at "L" level, the first  $EIO_2$  is fixed to "L"level, and the following  $EIO_2$  is connected to the preceding  $EIO_1$ . If the SHL is at "H" level, the first  $EIO_2$  as shown below.

# D<sub>0</sub>, D<sub>1</sub>, D<sub>2</sub>, D<sub>3</sub>

These are display data inputs that input data with clock synchronization. The table below shows the relationship between the LCD output for the display data and DFs and the LCD.

| Display Data | DF | LCD drive output         | LCD |

|--------------|----|--------------------------|-----|

| L            | L  | Non-selection level (V3) | OFF |

| Н            | L  | Selection level (V1)     | ON  |

| L            | Н  | Non-selection level (V4) | OFF |

| Н            | Н  | Selection level (VEE)    | ON  |

# LOAD

This is an input to simultaneously output the display data of one line stored in the latch (I). At the falling edge, the data in the latch (I) is transferred to the latch (II) end is output.

# SHL

Input to select for display data reading direction. Input of "L" level at Vss level fetches data in the direction from  $O_{160}$  to  $O_1$  sequentially, while input of "H" level at  $V_{DD}$  fetches data in the direction from  $O_1$  to  $O_{160}$ . The table below shows the relationship between read data and driver outputs ( $O_1$  to  $O_{160}$ ).

| SHL | EIO <sub>1</sub> | EIO <sub>2</sub> | Data           | Numbers of the clock pulse |                  |                  |  |                  |                  |                  |

|-----|------------------|------------------|----------------|----------------------------|------------------|------------------|--|------------------|------------------|------------------|

| ONE |                  | 2.02             | input          | 40 clocks                  | 39 clocks        | 38 clocks        |  | 3 clocks         | 2 clocks         | 1 clocks         |

|     |                  |                  | D <sub>0</sub> | 01                         | 05               | 09               |  | 0149             | 0 <sub>153</sub> | 0157             |

| I   | Outputs          | Innute           | D <sub>1</sub> | 02                         | 06               | 0 <sub>10</sub>  |  | 0 <sub>150</sub> | 0 <sub>154</sub> | 0 <sub>158</sub> |

| L   | Outputs          | inputs           | D <sub>2</sub> | 03                         | 07               | 0 <sub>11</sub>  |  | 0 <sub>151</sub> | 0 <sub>155</sub> | 0 <sub>159</sub> |

|     |                  |                  | D <sub>3</sub> | 04                         | 08               | 012              |  | 0 <sub>152</sub> | 0 <sub>156</sub> | 0 <sub>160</sub> |

|     |                  |                  | D <sub>0</sub> | 0 <sub>160</sub>           | 0 <sub>156</sub> | 0 <sub>152</sub> |  | 0 <sub>12</sub>  | 0 <sub>8</sub>   | 04               |

| н   | Innute           | Outputs          | D <sub>1</sub> | 0159                       | 0 <sub>155</sub> | 0151             |  | 011              | 07               | 03               |

|     | mputo            | outputs          | D <sub>2</sub> | O <sub>158</sub>           | 0154             | O <sub>150</sub> |  | 010              | 06               | 02               |

|     |                  |                  | D <sub>3</sub> | 0 <sub>157</sub>           | 0 <sub>153</sub> | 0 <sub>149</sub> |  | 09               | 05               | 01               |

# TRUTH TABLE

| DF | Display Data | DISPOFF | Driver output (01~0160) |

|----|--------------|---------|-------------------------|

| L  | L            | Н       | V <sub>3</sub>          |

| L  | Н            | Н       | V1                      |

| Н  | L            | Н       | V4                      |

| Н  | Н            | Н       | V <sub>EE</sub>         |

| Х  | Х            | L       | V <sub>1</sub>          |

X : don't care

# NOTES ON USAGE (when turning the power ON or OFF)

If a high voltage is applied to a LCD drive system while the logic supply is floating, over-current may destroy the device, because the voltage over the LCD drive system is high. Follow the sequence below when turning the power ON or OFF. Power ON : Logic system ON  $\rightarrow$  LCD drive system ON, or both ON Power OFF : LCD drive system OFF  $\rightarrow$  logic system OFF, or both OFF NOTICE

- 1. The information contained herein can change without notice owing to product and/or technical improvements. Before using the product, please make sure that the information being referred to is up-to-date.

- 2. The outline of action and examples for application circuits described herein have been chosen as an explanation for the standard action and performance of the product. When planning to use the product, please ensure that the external conditions are reflected in the actual circuit, assembly, and program designs.

- 3. When designing your product, please use our product below the specified maximum ratings and within the specified operating ranges including, but not limited to, operating voltage, power dissipation, and operating temperature.

- 4. Oki assumes no responsibility or liability whatsoever for any failure or unusual or unexpected operation resulting from misuse, neglect, improper installation, repair, alteration or accident, improper handling, or unusual physical or electrical stress including, but not limited to, exposure to parameters beyond the specified maximum ratings or operation outside the specified operating range.

- 5. Neither indemnity against nor license of a third party's industrial and intellectual property right, etc. is granted by us in connection with the use of the product and/or the information and drawings contained herein. No responsibility is assumed by us for any infringement of a third party's right which may result from the use thereof.

- 6. The products listed in this document are intended for use in general electronics equipment for commercial applications (e.g., office automation, communication equipment, measurement equipment, consumer electronics, etc.). These products are not authorized for use in any system or application that requires special or enhanced quality and reliability characteristics nor in any system or application where the failure of such system or application may result in the loss or damage of property, or death or injury to humans. Such applications include, but are not limited to, traffic and automotive equipment, safety devices, aerospace equipment, nuclear power control, medical equipment, and life-support systems.

- 7. Certain products in this document may need government approval before they can be exported to particular countries. The purchaser assumes the responsibility of determining the legality of export of these products and will take appropriate and necessary steps at their own expense for these.

- 8. No part of the contents contained herein may be reprinted or reproduced without our prior permission.

- 9. MS-DOS is a registered trademark of Microsoft Corporation.

Copyright 2000 Oki Electric Industry Co., Ltd.