**PEDL9371-01** Issue Date: Dec. 9, 2002

# **ML9371**

# **Preliminary**

64-Channel Organic EL Cathode Driver

#### **GENERAL DESCRIPTION**

The ML9371 is an organic EL cathode driver LSI with 64 outputs. Since this LSI has the output condition setting function, which allows setting of all outputs High, all outputs Low, and all outputs High Impedance, the user can set driving methods suited to the characteristics of individual organic EL panel. When combined with ML9361 the organic EL anode driver, the ML9371 can drive a  $64 \times 128$  full-dot panel.

#### **FEATURES**

Logic power supply voltage

EL drive voltage

Cathode outputs

Cathode low output current

Cathode high output current

Cathode low ON-resistance

Cathode high ON-resistance

Cathode low ON-resistance

Cathode low ON-resistance

• All outputs High, all outputs Low, all outputs High Impedance

• Package : Gold bump chip (TCP is tailored for each customer requirement)

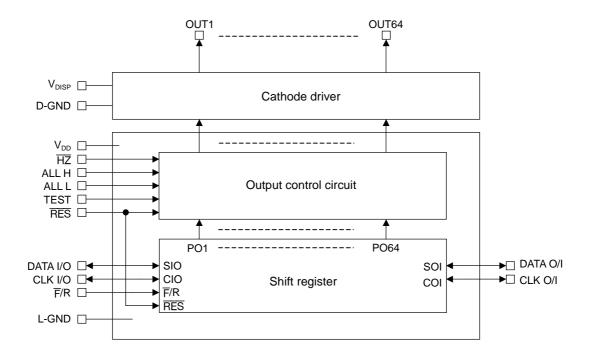

### **BLOCK DIAGRAM**

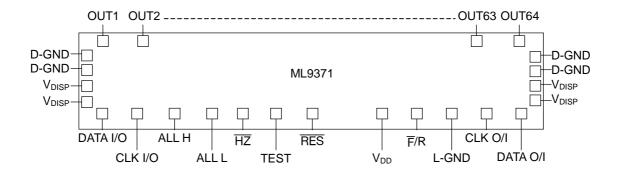

## PIN CONFIGURATION (View from the Pad Layout Side)

## PIN DESCRIPTION

| V <sub>DISP</sub> V <sub>DD</sub> D-GND L-GND L-GND  RES  V <sub>DISP</sub> is the cathode driver circuit power supply pin.  V <sub>DD</sub> is the logic circuit power supply pin.  D-GND is a ground pin for cathode driver circuit.  L-GND is a ground pin for logic circuit.  D-GND and L-GND should be connected outside the LSI.  Input pin for register initialization signal.  When this pin is set low, the LSI enters the following initial setting states:  • Shift register outputs (POm): all "low" (m = 1 to 64)  • All cathode drive signal outputs (OUT1 to OUT64): "high impedance" |        |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| V <sub>DD</sub> D-GND L-GND L-GND  RES  V <sub>DD</sub> is the logic circuit power supply pin. D-GND is a ground pin for cathode driver circuit. L-GND is a ground pin for logic circuit. D-GND and L-GND should be connected outside the LSI.  Input pin for register initialization signal. When this pin is set low, the LSI enters the following initial setting states: Shift register outputs (POm): all "low" (m = 1 to 64)                                                                                                                                                                   |        |

| D-GND L-GND L-GND L-GND is a ground pin for cathode driver circuit. L-GND is a ground pin for logic circuit. D-GND and L-GND should be connected outside the LSI.  Input pin for register initialization signal. When this pin is set low, the LSI enters the following initial setting states: • Shift register outputs (POm): all "low" (m = 1 to 64)                                                                                                                                                                                                                                              |        |

| L-GND is a ground pin for logic circuit.  D-GND and L-GND should be connected outside the LSI.  Input pin for register initialization signal.  When this pin is set low, the LSI enters the following initial setting states:  • Shift register outputs (POm): all "low" (m = 1 to 64)                                                                                                                                                                                                                                                                                                               |        |

| RES  D-GND and L-GND should be connected outside the LSI.  Input pin for register initialization signal.  When this pin is set low, the LSI enters the following initial setting states:  • Shift register outputs (POm): all "low" (m = 1 to 64)                                                                                                                                                                                                                                                                                                                                                    |        |

| RES  When this pin is set low, the LSI enters the following initial setting states:  • Shift register outputs (POm): all "low" (m = 1 to 64)                                                                                                                                                                                                                                                                                                                                                                                                                                                         |        |

| • Shift register outputs (POm): all "low" (m = 1 to 64)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |        |

| • Shift register outputs (POm): all "low" (m = 1 to 64)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |        |

| • All cathode drive signal outputs (OUT1 to OUT64): "high impedance"                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |        |

| , , , , , , , , , , , , , , , , , , , ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |        |

| Input pin for data transfer direction select signal for shift register.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |        |

| F/R I • When this pin is low, data is transferred starting at PO1 toward PO64.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |        |

| When this pin is high, data is transferred starting at PO64 toward PO1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |        |

| Cathode scan data input-output pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |        |

| DATA I/O I/O When the F/R pin is low, this pin is an input pin, and when it is high, this pin is an o                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | utput  |

| pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |        |

| Cathode scan data input-output pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |        |

| DATA O/I I/O When the F/R pin is low, this pin is an output pin, and when it is high, this pin is an                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | nput   |

| pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |        |

| Cathode scan data transfer clock input-output pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |        |

| CLK I/O I/O When the F/R pin is low, this pin is an input pin, and when it is high, this pin is an o                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | utput  |

| pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |        |

| Cathode scan data transfer clock input-output pin.  CLK O/I I/O When the F/R pin is low, this pin is an output pin, and when it is high, this pin is an                                                                                                                                                                                                                                                                                                                                                                                                                                              | :      |

| CLK O/I I/O When the F/R pin is low, this pin is an output pin, and when it is high, this pin is an pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | nput   |

| Input pin for cathode drive signal output control signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |        |

| HZ   I When this pin is low, all cathode drive signal outputs (OUT1 to OUT64) are                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | hiah   |

| impedance.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | iligii |

| Input pin for cathode drive signal output control signal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |        |

| ALL H  When this pin is high, all cathode drive signal outputs (OUT1 to OUT64) are high.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |        |

| Input nin for cathode drive signal output control signal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |        |

| ALL L   I   When this pin is high, all cathode drive signal outputs (OUT1 to OUT64) are low.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |        |

| TEST — Pin for production tests. Leave this pin open or connect it to L-GND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |        |

| OUT 1 to 64 O Cathode drive signal output pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |        |

## **FUNCTION TABLE**

1. Shift Register Operation during Cathode Scan Data Transfer

| Input/Output |     |                |             |            |             |            | Shift Registe | r Parallel Out |           |   |  |  |  |  |   |        |            |  |

|--------------|-----|----------------|-------------|------------|-------------|------------|---------------|----------------|-----------|---|--|--|--|--|---|--------|------------|--|

| RES          | F/R | CLK<br>I/O     | DATA<br>I/O | CLK<br>O/I | DATA<br>O/I | PO<br>1    | PO<br>2       | PO<br>63       | PO<br>64  |   |  |  |  |  |   |        |            |  |

|              | L   | Input          | Input       | Output     | Output      | L          | L             | L              | L         |   |  |  |  |  |   |        |            |  |

| L            | Η   | Output         | Output      | Input      | Input       | L          | L             | L              | L         |   |  |  |  |  |   |        |            |  |

| Н            | L   | Ļ              | L           |            |             | L          | PO<br>1n      | PO<br>62n      | PO<br>63n |   |  |  |  |  |   |        |            |  |

|              |     | ·              | Н           | Output     | Output      | Н          | PO<br>1n      | PO<br>62n      | PO<br>63n |   |  |  |  |  |   |        |            |  |

|              |     |                | L<br>H      |            |             | Invariable |               |                |           |   |  |  |  |  |   |        |            |  |

|              | н   |                |             |            | <b>★</b>    | L          | PO<br>2n      | PO<br>3n       | PO<br>64n | L |  |  |  |  |   |        |            |  |

|              |     | H Output Outpu | Output      |            | Н           | PO<br>2n   | PO<br>3n      | PO<br>64n      | Н         |   |  |  |  |  |   |        |            |  |

|              |     |                |             |            |             |            |               |                |           |   |  |  |  |  | Ŧ | L<br>H | Invariable |  |

PO1n to PO64n: States of PO1 to PO64 immediately before the clock rises

## 2. Operation of Output Section

| RES | HZ | ALL H | ALL L | POm | OUTm           |      |

|-----|----|-------|-------|-----|----------------|------|

| L   | Х  | Χ     | X L   |     | High impedance |      |

|     | L  | Х     | Χ     | X   | High impedance |      |

|     | Н  |       | Н     | X   | X              | High |

| Н   |    |       | Н     | Х   | Low            |      |

|     |    | L     | L     | Н   | Low            |      |

|     |    |       |       | L   | High           |      |

X: Don't Care

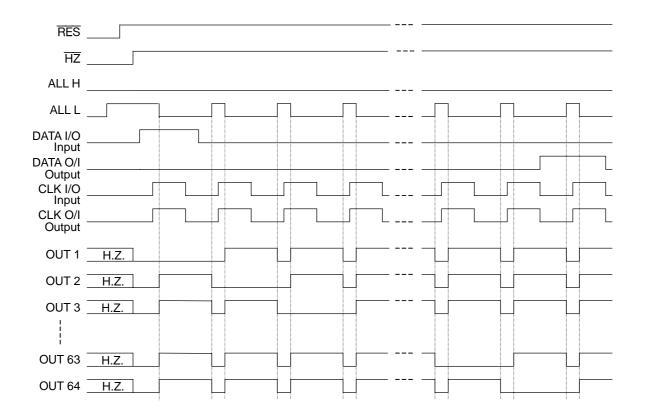

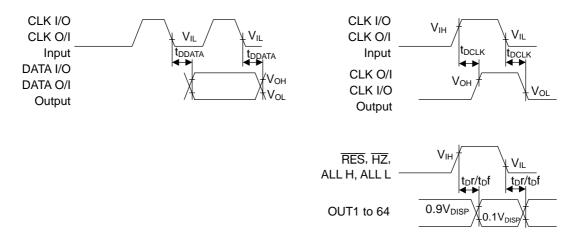

## **OUTPUT WAVEFORMS**

When  $\overline{F}/R$  is low

## ABSOLUTE MAXIMUM RATINGS

| Parameter                                      | Symbol                    | Condition                | Rating                                      | Unit |

|------------------------------------------------|---------------------------|--------------------------|---------------------------------------------|------|

| Logic power supply voltage                     | $V_{DD}$                  | Ta = 25°C                | -0.3 to +6.5                                | V    |

| EL drive power supply voltage (cathode)        | $V_{DISP}$                | Ta = 25°C                | -0.3 to +35                                 | V    |

| Logic input voltage                            | V <sub>IN</sub>           | Ta = 25°C                | $-0.3$ to $V_{DD} + 0.3$                    | V    |

| Logic output voltage                           | V <sub>OUT</sub>          | Ta = 25°C                | $-0.3$ to $V_{DD} + 0.3$                    | V    |

| EL driver output voltage                       | V <sub>OUT-EL</sub>       | Applied to OUT1 to OUT64 | -0.3 to V <sub>DISP</sub> + 0.3             | V    |

| EL driver output voltage (pulse) <sup>*1</sup> | V <sub>OUT-ELP</sub>      | Applied to OUT1 to OUT64 | -V <sub>DISP</sub> to 2 × V <sub>DISP</sub> | V    |

| El driver output ourrent                       | I <sub>ELL</sub> (sink)   | Applied to OUT1 to       | 200                                         | mA   |

| EL driver output current                       | I <sub>ELH</sub> (source) | OUT64                    | <b>–70</b>                                  | mA   |

| Storage temperature                            | Tstg                      | _                        | -40 to +125                                 | °C   |

<sup>\*1</sup> Consult Oki for customization of pulse width.

## RECOMMENDED OPERATING CONDITIONS

| Parameter                               | Symbol                    | Condition        |                                                            | Range             | Unit |

|-----------------------------------------|---------------------------|------------------|------------------------------------------------------------|-------------------|------|

| Logic power supply voltage              | $V_{DD}$                  |                  | _                                                          | 3.0 to 5.5        | V    |

| EL drive power supply voltage (cathode) | $V_{DISP}$                |                  | _                                                          | 8 to 30           | V    |

| Logic input voltage                     | V <sub>IN</sub>           | _                |                                                            | $0.0$ to $V_{DD}$ | V    |

|                                         | I <sub>ELL</sub> (sink)   | Applied to       | $V_0 = 0.75 \text{ V}$                                     | 150               | mA   |

| EL driver output current                | I <sub>ELH</sub> (source) | OUT1 to<br>OUT64 | $V_{DISP} = 14 \text{ V}$ $V_{O} = V_{DISP} - 5 \text{ V}$ | <b>–</b> 50       | mA   |

| Junction operating temperature Tj       |                           |                  | _                                                          | -40 to +125       | °C   |

## **ELECTRICAL CHARACTERISTICS**

### **DC** Characteristics

$V_{DD} = 3.0 \text{ to } 5.5 \text{ V}, V_{DISP} = 8 \text{ to } 30 \text{ V}, \text{Tjop} = -40 \text{ to } +125^{\circ}\text{C}$

| Parameter            | Symbol             | Applicable Pins                                       | $v_{DD} = 3.0 to 3.3 v, v_{DISI}$ Condition                                | Min.               | Тур. | = -40 to +         | Unit |

|----------------------|--------------------|-------------------------------------------------------|----------------------------------------------------------------------------|--------------------|------|--------------------|------|

| "H" input voltage    | V <sub>IH</sub>    | All input pins                                        | Condition                                                                  | 0.8V <sub>DD</sub> | τyp. | V <sub>DD</sub>    | V    |

| "L" input voltage    |                    | ·                                                     | _                                                                          | 0.6 V DD           |      | 0.2V <sub>DD</sub> | V    |

| Schmitt voltage      | V <sub>IL</sub>    | All input pins<br>CLK I/O, CLK O/I                    | _                                                                          | U                  | _    | 0.2 V DD           |      |

| width                | $V_{SH}$           | ALL H, ALL L                                          | $V_{DD} = 5.0 \text{ V}$                                                   | 0.4                | _    | 0.9                | V    |

|                      |                    | DATA I/O, DATA O/I                                    | V <sub>DD</sub> = 5.5 V                                                    | 4.0                |      | 40                 | μА   |

| "H" input current    | I <sub>IH1</sub>   | CLK I/O, CLK O/I<br>Input state                       | $V_1 = 5.5 \text{ V}$                                                      | -10                | _    | 10                 |      |

| Tr input current     | I <sub>IH2</sub>   | RES, F/R, HZ                                          | $V_{DD} = 5.5 \text{ V}$                                                   | 30                 |      | 140                | μΑ   |

|                      | 'IH2               | ALL H, ALL L                                          | V <sub>I</sub> = 5.5 V                                                     | - 50               |      | 140                | μπ   |

| "L" input current    | I <sub>IL1</sub>   | DATA I/O, DATA O/I<br>CLK I/O, CLK O/I<br>Input state | $V_{DD} = 5.5 \text{ V}$<br>$V_{I} = 0.0 \text{ V}$                        | -10                | _    | 10                 | μА   |

| 2 input ourion       | I <sub>IL2</sub>   | RES, F/R, HZ<br>ALL H, ALL L                          | $V_{DD} = 5.5 \text{ V}$<br>$V_{I} = 0.0 \text{ V}$                        | -10                | _    | 10                 | μΑ   |

| (III)                | .,                 | DATA I/O, DATA O/I                                    | V <sub>DD</sub> = 3.0 V                                                    | 0.01/              |      | _                  | .,   |

| "H" output voltage   | V <sub>OH</sub>    | CLK I/O, CLK O/I Output state                         | $I_0 = -200  \mu A$                                                        | $0.8V_{DD}$        | _    |                    | V    |

|                      |                    | DATA I/O, DATA O/I                                    | V <sub>DD</sub> = 3.0 V                                                    |                    |      | 0.2V <sub>DD</sub> | V    |

| "L" output voltage   | $V_{OL}$           | CLK I/O, CLK O/I Output state                         | $I_0 = 200 \mu A$                                                          | _                  | _    |                    |      |

|                      |                    | - Garpar Grato                                        | V <sub>DISP</sub> = 14 V                                                   |                    |      | _                  |      |

| "H" output current   | I <sub>ELH</sub>   | OUT1 to OUT64                                         | $V_0 = 9 \text{ V}$<br>Only one output is high                             | <b>–</b> 50        | _    |                    | mA   |

|                      |                    |                                                       | $V_{DISP} = 14 \text{ V}$                                                  |                    |      |                    |      |

| "L" output current 1 | I <sub>ELL1</sub>  | OUT1 to OUT64                                         | $V_0 = 0.75 \text{ V}$                                                     | 150                | _    | _                  | mA   |

|                      |                    |                                                       | Only one output is low $V_{DISP} = 14 \text{ V}$                           |                    |      |                    |      |

| "L" output current 2 | I <sub>ELL2</sub>  | OUT1 to OUT64                                         | $V_0 = 5 V$                                                                | 50                 | _    | _                  | mΑ   |

| -                    |                    |                                                       | ALL L = high                                                               |                    |      |                    |      |

|                      |                    |                                                       | $V_{DD} = 5.5 \text{ V}, V_{DISP} = 30 \text{ V}$<br>Clock = 100 kHz       |                    | _    |                    | mA   |

|                      | I <sub>DISP1</sub> | $V_{DISP}$                                            | The low state of only one                                                  | _                  |      | 30                 |      |

|                      |                    |                                                       | output is scanned.                                                         |                    |      |                    |      |

|                      |                    |                                                       | No load $V_{DD} = 5.5 \text{ V}, V_{DISP} = 30 \text{ V}$                  |                    |      |                    |      |

|                      |                    |                                                       | $V_{DD} = 5.5 \text{ V}, V_{DISP} = 50 \text{ V}$ $Clock = 10 \text{ kHz}$ |                    |      |                    |      |

|                      | I <sub>DISP2</sub> | $V_{DISP}$                                            | The low state of only one                                                  | _                  | _    | 3                  | mA   |

|                      |                    |                                                       | output is scanned. 1                                                       |                    |      |                    |      |

| 0                    |                    |                                                       | No load                                                                    |                    |      |                    |      |

| Supply current       |                    |                                                       | $V_{DD} = 5.5 \text{ V}, V_{DISP} = 30 \text{ V}$ Clock stopped            |                    | _    |                    | μΑ   |

|                      | I <sub>DISPS</sub> | $V_{DISP}$                                            | $\overline{RES} = low$                                                     | _                  |      | 30                 |      |

|                      |                    |                                                       | No load                                                                    |                    |      |                    |      |

|                      |                    |                                                       | $V_{DD} = 5.5 \text{ V}, V_{DISP} = 30 \text{ V}$                          |                    |      |                    |      |

|                      |                    |                                                       | Clock = 100 kHz                                                            |                    | _    | 3                  | mA   |

|                      | I <sub>DD</sub>    | $V_{DD}$                                              | The low state of only one output is scanned.*1                             | _                  |      |                    |      |

|                      |                    |                                                       | No load                                                                    |                    |      |                    |      |

|                      | I <sub>DDS</sub>   | V                                                     | RES = low                                                                  |                    |      | 10                 | ^    |

|                      |                    | $V_{DD}$                                              | No load                                                                    |                    |      | 10                 | μА   |

<sup>\*1</sup> See the section of "OUTPUT WAVEFORMS".

## **AC Characteristics**

$V_{DD} = 3.0 \text{ to } 5.5 \text{ V}, V_{DISP} = 8 \text{ to } 30 \text{ V}, \text{ Tjop} = -40 \text{ to } +125^{\circ}\text{C}$

| VDD = 3.0 to 3.3 v, VDISP = 0  |                    |                                        |            |           |      | ρ – <del>-4</del> 0 ι | 7 + 123 0 |

|--------------------------------|--------------------|----------------------------------------|------------|-----------|------|-----------------------|-----------|

| Parameter Symbo                |                    | Applicable pins                        | Condition  | Min.      | Тур. | Max.                  | Unit      |

| CLK frequency f <sub>CLK</sub> |                    | CLK I/O, CLK O/I                       | _          | _         | _    | 100                   | kHz       |

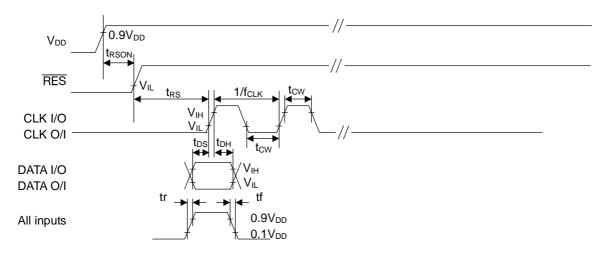

| CLK pulse width                | t <sub>CW</sub>    | CLK I/O, CLK O/I                       | _          | 5         | _    | _                     | μS        |

| DATA → CLK                     |                    | CLK I/O, DATA I/O                      |            | <b>50</b> |      | _                     |           |

| setup time                     | t <sub>DS</sub>    | CLK O/I, DATA O/I                      | _          | 50        | _    |                       | ns        |

| $CLK \to DATA$                 |                    | CLK I/O, DATA I/O                      |            | 50        |      | _                     |           |

| hold time                      | t <sub>DH</sub>    | CLK O/I, DATA O/I                      | _          | 50        |      |                       | ns        |

| Reset execution time           | t <sub>RSON</sub>  | V <sub>DD</sub> , RES                  | _          | 250       | _    | _                     | ns        |

| $\overline{RES} \to CLK$       | 4                  | t <sub>RS</sub> CLK I/O, CLK O/I RES — |            | 250       | _    | _                     | 20        |

| reset recovery time            | <sup>L</sup> RS    |                                        |            |           |      |                       | ns        |

| CLK input/output               | 4                  |                                        | Cl 45 pF   |           |      | 100                   | 20        |

| delay time                     | t <sub>DCLK</sub>  | CLK I/O, CLK O/I                       |            | _         | _    | 100                   | ns        |

| Data output delay              | 4                  | CLK I/O, DATA O/I                      | Cl 45 pF   |           |      | 100                   | 20        |

| time                           | t <sub>DDATA</sub> | CLK O/I, DATA I/O                      |            | _         | _    | 100                   | ns        |

| Cathode output delay           | t <sub>D</sub> r   | RES, HZ, ALL H,                        |            |           |      |                       |           |

| time                           | t <sub>D</sub> f   | ALL L                                  | CL = 45 pF | _         | _    | 2.0                   | μS        |

|                                | (D)                | OUT1 to OUT64                          |            |           |      |                       |           |

| Input signal rise/fall         | tr                 | All input pins                         |            | _         | _    | 500                   | ns        |

| time                           | tf                 | 7 til lilput pillo                     |            |           |      | 500                   | 113       |

#### **TIMING DIAGRAMS**

### **Data Input**

### **Output Delay**

## POWER APPLYING SEQUENCE

When applying power, apply it to the logic power supply  $(V_{DD})$  first, then to the EL drive power supply  $(V_{DISP})$ . When turning the power off, turn off the EL drive power supply  $(V_{DISP})$  first, then the logic power supply  $(V_{DD})$ .

Make the  $\overline{RES}$  pin high at least 250 ns after applying power to  $V_{DD}$ . (Refer to Reset execution time in AC Characteristics.)

# **REVISION HISTORY**

| Dogument        |              | Page                |                    |                       |  |

|-----------------|--------------|---------------------|--------------------|-----------------------|--|

| Document<br>No. | Date         | Previous<br>Edition | Current<br>Edition | Description           |  |

| PEDL9371-01     | Dec. 9, 2002 | _                   | -                  | Preliminary edition 1 |  |

#### NOTICE

1. The information contained herein can change without notice owing to product and/or technical improvements. Before using the product, please make sure that the information being referred to is up-to-date.

- 2. The outline of action and examples for application circuits described herein have been chosen as an explanation for the standard action and performance of the product. When planning to use the product, please ensure that the external conditions are reflected in the actual circuit, assembly, and program designs.

- 3. When designing your product, please use our product below the specified maximum ratings and within the specified operating ranges including, but not limited to, operating voltage, power dissipation, and operating temperature.

- 4. Oki assumes no responsibility or liability whatsoever for any failure or unusual or unexpected operation resulting from misuse, neglect, improper installation, repair, alteration or accident, improper handling, or unusual physical or electrical stress including, but not limited to, exposure to parameters beyond the specified maximum ratings or operation outside the specified operating range.

- 5. Neither indemnity against nor license of a third party's industrial and intellectual property right, etc. is granted by us in connection with the use of the product and/or the information and drawings contained herein. No responsibility is assumed by us for any infringement of a third party's right which may result from the use thereof.

- 6. The products listed in this document are intended for use in general electronics equipment for commercial applications (e.g., office automation, communication equipment, measurement equipment, consumer electronics, etc.). These products are not authorized for use in any system or application that requires special or enhanced quality and reliability characteristics nor in any system or application where the failure of such system or application may result in the loss or damage of property, or death or injury to humans. Such applications include, but are not limited to, traffic and automotive equipment, safety devices, aerospace equipment, nuclear power control, medical equipment, and life-support systems.

- 7. Certain products in this document may need government approval before they can be exported to particular countries. The purchaser assumes the responsibility of determining the legality of export of these products and will take appropriate and necessary steps at their own expense for these.

- 8. No part of the contents contained herein may be reprinted or reproduced without our prior permission.

Copyright 2002 Oki Electric Industry Co., Ltd.