| Oki, | Network Solutions    |

|------|----------------------|

|      | for a Global Society |

PEDL9361-01 Issue Date:Dec. 12, 2002

# **Preliminary**

128-Channel Organic EL Anode Driver

# **GENERAL DESCRIPTION**

The ML9361 is an organic EL anode driver LSI with 128 drivers. The anode driver is constant current output type and allows adjustment of current and pulse width for each output. Since this LSI has the output condition setting function, which allows setting of all outputs High, all outputs Low, and all outputs High Impedance, the user can set driving methods suited to the characteristics of individual organic EL panel. When combined with ML9371 the organic EL cathode driver, the ML9361 can drive a 64 × 128 full-dot panel.

# **FEATURES**

- : 3.0 to 5.5 V Logic power supply voltage EL drive voltage : 8.0 to 30 V (max.) • Anode outputs : 128 outputs • Anode high output current : -1.0 mA (constant current output, current adjustment range = at • 100%) • Anode low output current : 40 mA (max.) Anode low ON-resistance :  $500\Omega$  (max.) • Anode output current adjustment range : 0%, 33%, 66%, and 100% (for each output) . : Adjustable in 16 different degrees (adjusted by external clock input, • Output pulse width adjustment for each output) All outputs High, all outputs Low, and all outputs High Impedance can be set as output conditions : Gold bump chip (TCP is tailored for each customer requirement)

- Package

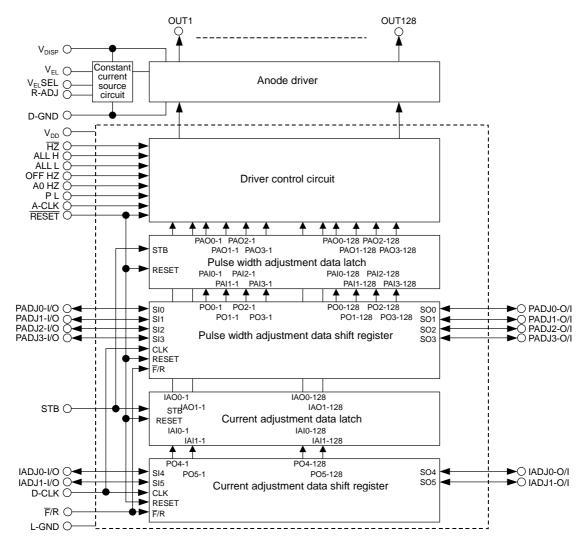

#### **BLOCK DIAGRAM**

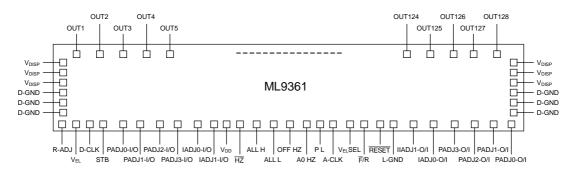

### PIN CONFIGURATION (Gold bump chip)

# **PIN DESCRIPTION**

| Mos         Power supply         DegNo         DegNo <thdegno< th=""> <thdegno< th=""> <thdegno< th="">         &lt;</thdegno<></thdegno<></thdegno<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Symbol          | I/O | Connected to    | Description                                                                                                                 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-----|-----------------|-----------------------------------------------------------------------------------------------------------------------------|

| V <sub>pc</sub> —         Power suppy         U <sub>c</sub> is the logic circuit power suppy pin.           D-GND         —         Power suppy         D-GND is a ground pin for logic circuit.         D-GND is a ground pin for logic circuit.           U-GND is a ground pin for logic circuit.         D-GND and L-GND should be connected outside the LSI.           Via.         I         Power suppy         D'UT to CUT128 output current adjusting voltage input pin.           Via.         I         Power suppy         Pin for selecting the output current adjusting voltage input pin.           Via.         I         Microcontroller         When this pin is low, LSI's internal voltage (S V) is selected.           R-ADJ         I         Resistor         OUT1 to CUT128 output current adjusting voltage input on the Via. pin is selected.           R-ADJ         I         Resistor         OUT1 to CUT128 output current adjusting at POn-128 toward POn-128. (n = 1 to 5)           IADJ0-IO         Via         Microcontroller         When this pin is high, data is transferred starting at POn-128 toward POn-128. (n = 1 to 5)           IADJ0-IO         Via         Microcontroller.         When the FR pin is log, these pins are input pins and data is read into at the rising edge of D-CLK.           PADJ0-IO         Via         Microcontroller.         Anode output current adjusting data input-output pins.           PADJ0-OI         Via                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | VDISP           |     |                 | $V_{\text{DISP}}$ is a power supply pin for anode driver circuit and constant current source circuit.                       |

| D-SND         —         Power supply           U-GND         D-SND is a ground pin for logic circuit.         L-GND and L-GND should be connected outside the LSI.           Vet.         1         Power supply         DUTTs output current sating voltage input pin.           Vet.         1         Power supply         DUTTs output a voltage within the guaranteed operating range.           Vet.SEL         1         Microcontroller         When this pin is enabled when Vs_SEL is high, and disabled when it is low.           R-ADJ         1         Resistor         OUTT to OUT28 output current adjusting voltage for anode driver circuit.           Pin for selecting the output current adjusting voltage (V) is selected.         •When this pin is high, the input voltage to the current adjusting data shift register and the voltage is the voltage is selected.           F/R         1         Microcontroller         •When this pin is high, these pins are input pins.           r/ADJ0-I/O         I/O         Microcontroller         •When the F/R pin is logid tata input-output pins.           r/ADJ0-0/O         0/I         Microcontroller         •Circl.K. When the F/R pin is high, these pins are input pins and data is read into at the rising edge di D-CLK.           PADJ0-1/O         0/I         Microcontroller         Anode output pulse width adjusting data input-output pins.           PADJ0-1/O         0/I         Microcontroller         F                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                 |     | _               |                                                                                                                             |

| L-GND         L-GND is a gloudo pin for logic circuit.           U-GND is a gloudo pin for logic circuit.         D-GND and L-GND Should be connected outside the LSI.           Vet.         1         Power supply           Input voltage to this pin is enabled when V_SEL is high, and disabled when it is low.           Leave this pin copen or input a voltage within the guaranteed operating range.           Vet.SEL         1           Microcontroller         •When this pin is low, LSI's internal voltage (5V) is selected.           R-ADJ         1         Resistor           OUT1 to OUT128 output current adjusting data shift register.         •When this pin is low, Lat is transferred starting at POn-1 toward POn-128. (n = 1 to 5)           IADJ0-I/O         I/O         Outfload as the transferred starting at POn-1 toward POn-128. (n = 1 to 5)           IADJ0-I/O         I/O         Wincrocontroller, or ML381 on the F/R pin is low, these pins are input pins and that is read into at the rising edge of D-CLK. When the F/R pin is low, these pins are output pins.           PADJ0-I/O         O/I         Microcontroller, or ML381 on next stage         Anode output use with adjusting data input-output pins.           PADJ2-I/O         O/I         Anode output use with adjusting data input-output pins.           PADJ2-O/I         O/I         Anode output use with adjusting data input-output pins.           PADJ2-O/I         O/I         Anode output us                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                 | _   | Power supply    |                                                                                                                             |

| Vel.         I         Develop and compare volume of controlling voltage input pin.           Vel.         I         Power supply         Power supply           Vel.SEL         I         Microcontroller         Yes between this pin is enabled when Velse (Lishigh, and disabled when it is low.           Leave this pin open or input a voltage within the guaranteed operating range.         Phi for selecting the output current adjusting voltage (5 V) is selected.           R-ADJ         I         Resistor         OUT1 to OUT128 output current adjusting voltage (5 V) is selected.           F/R         I         Microcontroller         When this pin is high, the input voltage at the Vel protocomposition pin.           IADJ0-VO         IOT         OUT18 output current adjusting data infit register and pulse width adjusting data is hift register.           IADJ0-VO         I/O         Nicrocontroller         When this pin is ligh, these pins are output pins.           Microcontroller         node output current adjusting data input-output pins.         When the F/R pin is high, these pins are output pins and the output status changes at the falling edge of D-CLK.           PADJ0-VO         I/O         Nicrocontroller         Anode output urrent adjusting data input-output pins.           PADJ0-VO         I/O         Nicrocontroller         Anode output use width adjusting data input-output pins.           PADJ0-VO         I/O         Nicrocontroller <td>-</td> <td></td> <td></td> <td>5 1 5</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | -               |     |                 | 5 1 5                                                                                                                       |

| V <sub>Et</sub> I         Power supply<br>Leave this pin open or input a voltage within the guaranteed operating range.<br>Leave this pin open or input a voltage within the guaranteed operating range.           V <sub>E3</sub> SEL         I         Microcontroller         •When this pin is pin, LSS internal voltage (5 V) is selected.           R-ADJ         I         Resistor         OUT1 to UT128 output current adjusting voltage (5 V) is selected.           F/R         I         Microcontroller         •When this pin is low, these pins are input pin for current adjusting data shift register and<br>Data transfer direction select signal input pin for current adjusting data shift register and<br>within the sustain select starting at POn-128 toward POn-128. (n = 1 to 5)           IADJ0-V0<br>IADJ1-V0         I/O         Microcontroller         •When this pin is low, data is transferred starting at POn-128 toward POn-128. (n = 1 to 5)           IADJ0-V0<br>IADJ1-V0         I/O         Microcontroller,<br>or ML3361 on<br>or ML3361 on                                                   | L-OND           |     |                 |                                                                                                                             |

| Leave this pin open or input a voltage within the guaranteed operating range.           Pin for selecting the output current adjusting voltage for anode driver circuit.           Wicrocontroller         • When this pin is high, the input voltage at the X-gua pin is selected.           R-ADJ         I         Resistor         OUT1 to OUT128 output current setting resistor connection pin.           Bin         Data transfer direction select sign and provide the X-guaranteed operating at POn-1 to ward POn-128. In = 1 to 5)           IADJO-I/O         V/O         Microcontroller         • When this pin is low, data is transferred starting at POn-1 toward POn-128. In = 1 to 5)           IADJO-I/O         V/O         Microcontroller         • When the F/R pin is high, data is transferred starting at POn-128 toward POn-1. (In = 1 to 5)           IADJO-I/O         V/O         Microcontroller         • When the F/R pin is high, data is transferred starting at POn-128 toward POn-1. (In = 1 to 5)           IADJO-0/I         V/O         Microcontroller         • When the F/R pin is high, these pins are output pins and data is read into at the rising edge of D-CLK. When the F/R pin is high, these pins are output pins.           PADJ-1/O         V/O         Microcontroller         • Anode output pulse width adjusting data input-output pins.           PADJ-1/O         V/O         Microcontroller         • Anode output pulse width adjusting data and anode output pins and the output status othaga set the failing edge of D-CLK.      <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                 |     |                 |                                                                                                                             |

| V <sub>R.</sub> SEL         I         Microcontroller         When this pin is low, LSF is internal voltage (5 V) is selected.           R-ADJ         I         Resistor         OUT I to OUT128 output current setting resistor connection pin.           Detains         Data transfer direction select signal input pin for current adjusting data shift register and pulse width adjusting data sith register.           IADJ0-I/O         I/O         Data transfer direction select signal input pin for current adjusting data sith register and pulse width adjusting data input-output pins.           IADJ0-I/O         I/O         Anode output current adjusting data input-output pins.           IADJ0-I/O         I/O         Microcontroller         When the F/R pin is low, these pins are input pins and data is read into at the rising edge of D-CLK.           IADJ0-0/I         On         I/O         Microcontroller         Ch-CK when the F/R pin is low, these pins are input pins and data is read into at the rising edge of D-CLK.           PADJ0-1/O         On         Microcontroller         Anode output pulse width adjusting data input-output pins.           PADJ0-0/I         PADJ2-0/I         I/O         Anode output pulse width adjusting data input-output pins.           PADJ2-0/I         O/I         Microcontroller         Anode output pulse width adjusting data input-output pins.           <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | V <sub>EL</sub> | I   | Power supply    | Input voltage to this pin is enabled when $V_{EL}$ SEL is high, and disabled when it is low.                                |

| V <sub>RL</sub> SEL         I         Microcontroller         •When this pin is low, LSTs internal voltage (5 V) is selected.           R-ADJ         I         Resistor         OUT1 to OUT128 output current sating resistor connection pin.           F/R         I         Microcontroller         Data transfer direction select signal input pin for current adjusting data shift register.           IADJ0-I/O         I/O         Microcontroller         Data transfer direction select signal input pin for current adjusting data shift register.           IADJ0-I/O         I/O         Anode output current adjusting data input-output pins.         Anode output current adjusting data input-output pins.           IADJ0-I/O         I/O         Anode output current adjusting data input-output pins.         Anode output current adjusting data input-output pins.           IADJ0-I/O         O/I         Nicrocontroller         Anode output current adjusting data input-output pins.           PADJ0-I/O         O/I         Nicrocontroller         Anode output current adjusting data input-output pins.           PADJ0-I/O         Nicrocontroller         Anode output pulse width adjusting tai anput-output pins.           PADJ0-I/O         Nicrocontroller         Anode output pulse width adjusting data input-output pins.           PADJ0-I/O         Nicrocontroller         CLK. When the F/R pin is low, these pins are output pins and the output status chanast seed into at the rising edge of D-CLK.     <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                 |     |                 |                                                                                                                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                 |     | Missessatusllau | 5 1 , 5 5                                                                                                                   |

| R-ADJ         I         Resistor         OUT1 to OUT128 output current setting resistor connection pin.           Data transfer direction select signal inputs with adjusting data shift register.         •When this pin is low, data is transferred starting at POn-1 toward POn-128. (n = 1 to 5)           IADJ0-I/O<br>IADJ1-I/O         V/O         •When this pin is low, data is transferred starting at POn-128 toward POn-128. (n = 1 to 5)           IADJ0-I/O<br>IADJ1-I/O         V/O         Microcontroller         •When this pin is low, thats is transferred starting at POn-128 toward POn-128. (n = 1 to 5)           IADJ0-I/O<br>IADJ1-O1         V/O         Microcontroller, or Microsontroller, device and be output set state the falling edge of D-CLK.           PADJ-01/O         V/O         Microcontroller, device and be output current adjusting data input-output pins.           PADJ-01/O         Microsontroller, or Microsontroller, or Microsontroller, or Microsontroller, or Microsontroller, device and be output set state and be output state state and be output strestand be adjusting data input-output pins. <td>VELSEL</td> <td>I</td> <td>Wicrocontroller</td> <td><b>3</b> ( )</td>                                                                                                                                                                                                    | VELSEL          | I   | Wicrocontroller | <b>3</b> ( )                                                                                                                |

| F/R         I         Data transfer direction select signal input pin for current adjusting data shift register.           IADJ0-I/C         I/C         When this pin is low, data is transferred starting at POn-1 toward POn-16. (n = 1 to 5)           IADJ0-I/C         I/C         Microcontroller, or ML9361 on the F/R pin is low, these pins are input pins.         When the F/R pin is low, these pins are output pins.           IADJ0-0/I         I/C         Microcontroller, or CLK. When the F/R pin is high, these pins are output pins.         When the F/R pin is high, these pins are output pins.           IADJ0-0/I         O/I         Microcontroller, or CLK. When the F/R pin is low, these pins are output pins.         When the F/R pin is low, these pins are output pins.           PADJ0-1/O         PADJ0-1/O         I/C         Anode output current adjusting data input-output pins.         When the F/R pin is low, these pins are output pins and the output status changes at the falling edge of D-CLK.           PADJ0-1/O         I/O         Microcontroller, or ML9361 on next stage         Anode output pulse width adjusting data input-output pins.           PADJ3-0/I         O/I         Microcontroller, or ML9361 on next stage         Anode output urrent adjusting data and anode output pins and the output status changes at the falling edge of D-CLK.           PADJ3-0/I         O/I         Microcontroller, or ML9361 on next stage         Anode output urrent adjusting data and anode output urrent adjusting data and anode output urrent adjusting data and anode out                                                                                                                                                                                                                                                                                                                                                                                                                                          |                 |     |                 |                                                                                                                             |

| F/R         I         Microcontroller         pulse width adjusting data shift register.           IADJ0-I/O         I/O         Microcontroller         When this pin is kow, data is transferred starting at POn-1 toward POn-128. (n = 1 to 5)           IADJ0-I/O         I/O         Microcontroller         Numen this pin is low, these pins are input pins and data is read into at the rising edge of D-CLK.           IADJ0-O/I         O/I         mext stage         When the F/R pin is low, these pins are output pins.           VADJ0-I/O         next stage         When the F/R pin is low, these pins are output pins.           PADJ1-I/O         O/I         Microcontroller, the H/R pin is low, these pins are output pins and data is read into at the rising edge of D-CLK.           PADJ0-I/O         PADJ2-I/O         Microcontroller, the F/R pin is low, these pins are output pins and the output status changes at the falling edge of D-CLK.           PADJ2-OI         O/I         Microcontroller, the F/R pin is low, these pins are input pins and the output status changes at the falling edge of D-CLK.           PADJ2-OI         O/I         Node output pulse width adjusting data input-output pins.           PADJ2-OI         O/I         Anode output current adjusting data and anode output pins.           PADJ2-OI         O/I         Anode output current adjusting data and anode output pins.           PADJ3-OI         Microcontroller         Anode output current adjusting data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | R-ADJ           |     | Resistor        |                                                                                                                             |

| F/R         1         Microcontroller         • When this pin is low, data is transferred starting at POn-128 toward POn-12. (n = 1 to 5)           IADJ0-I/O         I/O         Microcontroller, then this pin is loigh, data is transferred starting at POn-128 toward POn-1. (n = 1 to 5)           IADJ0-I/O         I/O         Microcontroller, then this pin is loigh, data is transferred starting at POn-128 toward POn-1. (n = 1 to 5)           IADJ0-O/I         O/I         Microcontroller, the F/R pin is low, these pins are input pins and data is read into at the rising edge of D-CLK. When the F/R pin is high, these pins are output pins and the output status changes at the falling edge of D-CLK.           PADJ0-I/O         O/I         Microcontroller, or ML9361 on next stage         Microcontroller, the F/R pin is high, these pins are output pins.           PADJ0-I/O         PADJ3-OI         O/I         Nicrocontroller, or ML9361 on next stage         Anode output pulse width adjusting data input-output pins.           PADJ3-OI         O/I         Nicrocontroller, or ML9361 on next stage         Anode output pulse width adjusting data input-output pins.           PADJ3-OI         O/I         Nicrocontroller, or doe output pulse width adjusting data and anode output pins and the output status changes at the falling edge of D-CLK.           PADJ3-OI         O/I         Nicrocontroller         Anode output current adjusting data and anode output pins and data is read into at the rising edge of D-CLK.           PADJ3-OI         I <td< td=""><td>_</td><td></td><td></td><td></td></td<>                                                                                                                                                                                                                                                                                                                                                                                                                     | _               |     |                 |                                                                                                                             |

| IADJ0-I/O<br>IADJ1-I/O         I/O<br>IADJ1-I/O         •When this pin is high, data is transferred starting at POn-128 toward POn-1. (n = 1 to 5)           IADJ0-I/O<br>IADJ1-I/O         I/O         Microcontroller,<br>or ML3361 on<br>next stage         Anode output current adjusting data input-output pins and data is read into at the rising edge<br>of D-CLK. When the F/R pin is low, these pins are output pins and data is read into at the rising edge<br>of D-CLK. When the F/R pin is low, these pins are output pins and data is read into at the rising edge<br>of D-CLK. When the F/R pin is low, these pins are output pins and data is read into at the rising edge<br>of D-CLK. When the F/R pin is low, these pins are output pins and data is read into at the rising edge<br>of D-CLK. When the F/R pin is low, these pins are output pins and data is read into at the rising edge<br>of D-CLK. When the F/R pin is low, these pins are output pins and data is read into at the rising edge<br>of D-CLK. When the F/R pin is low, these pins are output pins and data is read into at the rising edge<br>of D-CLK. When the F/R pin is low, these pins are output pins and data is read into at the rising edge<br>of D-CLK. When the F/R pin is low, these pins are output pins and data is read into at the rising edge<br>of D-CLK. When the F/R pin is low, these pins are output pins and the output status<br>changes at the falling edge of D-CLK.           PADJ3-0/I         O/I         Microcontroller         Anode output current adjusting data input-output pins.           PADJ3-0/I         Microcontroller         Anode output current adjusting data and anode output pulse width adjusting data transfer<br>clock input pin (Schmitt input)           STB         I         Microcontroller         Anode output current adjusting data and anode output pulse width adjus                                                                                                                                                          | F/R             | I   | Microcontroller |                                                                                                                             |

| IADJ0-I/O         I/O           IADJ1-I/O         I/O           IADJ1-I/O         I/O           IADJ1-I/O         I/O           IADJ0-O/I         O/I           IADJ0-O/I         O/I           IADJ0-O/I         O/I           IADJ0-O/I         O/I           IADJ1-O/I         O/I           PADJ0-O/I         O/I           PADJ0-O/I         O/I           PADJ0-O/I         PADJ1-I/O           PADJ0-I/O         PADJ1-I/O           PADJ0-I/O         PADJ3-I/O           PADJ0-O/I         Microcontroller,<br>or MLS361 on<br>next stage           PADJ0-O/I         Microcontroller,<br>or MLS361 on<br>next stage           PADJ3-O/O         Microcontroller,<br>or MLS361 on<br>next stage         Anode output pulse width adjusting data input-output pins.           PADJ3-O/I         Microcontroller,<br>or MLS361 on<br>next stage         Anode output pulse width adjusting data input-output pins and data is read into at the rising edge<br>of D-CLK. When the F/R pin is low, these pins are output pins and data is read into at the rising edge<br>of D-CLK. When the F/R pin is low, these pins are output pins and data is read into at the rising edge<br>of D-CLK.           PADJ3-O/I         Microcontroller         Anode output current adjusting data input-output pins and data is read into at the rising edge<br>of D-CLK.           PLCLK         I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                 |     |                 |                                                                                                                             |

| IADJ0-I/O       I/O       Microcontroller, or ML381 on next stage       When the F/R pin is low, these pins are input pins and data is read into at the rising edge of D-CLK.         PADJ1-0/1       O/1       O/1       D+CLK. When the F/R pin is high, these pins are output pins and the output status of D+CLK. When the F/R pin is high, these pins are output pins and the output status of D+CLK. When the F/R pin is high, these pins are output pins and the output status of D+CLK. When the F/R pin is high, these pins are output pins and the output status of D+CLK. When the F/R pin is high, these pins are output pins and the output status of D+CLK. When the F/R pin is high, these pins are output pins and the output status of D+CLK. When the F/R pin is high, these pins are output pins and the output status of D+CLK. When the F/R pin is high, these pins are output pins and the output status of D+CLK. When the F/R pin is high, these pins are output pins and the output status of D+CLK. When the F/R pin is high, these pins are output pins.         PADJ1-0/1       O/1       Microcontroller, or ML3981 on next stage       Anode output pulse width adjusting data input-output pins.         PADJ2-01       Microcontroller       Anode output current adjusting data and anode output pins and the output status of D+CLK. When the F/R pin is low, these pins are output pins and the output status of D+CLK.         PADJ3-01       Microcontroller       Anode output current adjusting data and anode output pulse width adjusting data transfer clock input pin (Schmitt input).         PALK       Microcontroller       Anode output sail alten outputs: "high inpedance".         Microcontroller       Microcontroller                                                                                                                                                                                                                                                                                                            |                 |     |                 |                                                                                                                             |

| IADJ1-I/O       Wicrocontroller,<br>or ML3961 on<br>Next stage       of D-CLK. When the F/R pin is high, these pins are output pins.         IADJ0-0/I       O/I       on de output current adjusting data input-output pins.         PADJ0-I/O       PADJ0-I/O         PADJ0-I/O       I/O         PADJ0-I/O       I/O         PADJ0-I/O       I/O         PADJ3-I/O       I/O         PADJ3-I/O       I/O         PADJ0-O/I       or ML3961 on<br>next stage         PADJ0-O/I       or ML3961 on<br>next stage         PADJ3-O/I       next stage         PADJ3-O/I       node output current adjusting data input-output pins and the output status<br>changes at the falling edge of D-CLK.         PADJ3-O/I       Microcontroller       Anode output current adjusting data and anode output pins and the output status<br>changes at the falling edge of D-CLK.         D-CLK       I       Microcontroller       Anode output current adjusting data and anode output pins and the output status<br>changes athe falling edge of D-CLK.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | IADJ0-I/O       | 1/0 |                 |                                                                                                                             |

| IADJ0-0/I<br>IADJ1-0/I         Orl         UL381 on<br>ext stage         Chardee sat the failing edge of D-CLK.<br>When the F/R pin is high, these pins are input pins and data is read into at the rising edge<br>of D-CLK. When the F/R pin is low, these pins are output pins and the output status<br>changes at the falling edge of D-CLK.           PADJ0-I/O<br>PADJ2-I/O<br>PADJ2-I/O<br>PADJ2-I/O<br>PADJ3-I/O<br>PADJ3-I/O<br>PADJ3-O/I         I/O<br>Microcontroller,<br>or ML9361 on<br>next stage         Anode output pulse width adjusting data input-output pins.           PADJ1-0/I<br>PADJ3-0/I         Microcontroller,<br>or ML9361 on<br>next stage         Anode output pulse width adjusting data input-output pins.           PADJ3-0/I<br>PADJ3-0/I         Microcontroller,<br>or ML9361 on<br>next stage         Anode output pulse width adjusting data input-output pins.           PADJ3-0/I<br>PADJ3-0/I         Microcontroller,<br>of D-CLK. When the F/R pin is log, these pins are input pins and data is read into at the rising edge<br>of D-CLK. When the F/R pin is log, these pins are output pins and the output status<br>changes at the falling edge of D-CLK.           PADJ3-0/I<br>PADJ3-0/I         Microcontroller         Anode output current adjusting data and anode output pulse width adjusting data transfer<br>clock input pin (Schmit input)           STB         I         Microcontroller         Anode drive signal input pin.           RESET         I         Microcontroller         Anode drive signal outputs control signal.           NHE         I         Microcontroller         Input pin for anode drive signal output control signal.           HZ         <                                                                                                                                                                                                                                                                                                                                              | IADJ1-I/O       | 1/0 | Microcontrollor | of D-CLK. When the F/R pin is high, these pins are output pins and the output status                                        |

| IADJ0-0/I<br>IADJ1-0/I         or/l         Anode output current adjusting data input-output pins.<br>When the F/R pin is high, these pins are nutput pins and data is read into at the rising edge<br>of D-CLK. When the F/R pin is low, these pins are output pins and the output status<br>changes at the falling edge of D-CLK.           PADJ0-I/O<br>PADJ1-IO<br>PADJ2-IO<br>PADJ2-IO<br>PADJ2-IO<br>PADJ2-IO<br>PADJ2-O/I         I/O         Anode output pulse width adjusting data input-output pins.<br>When the F/R pin is high, these pins are output pins and the output status<br>changes at the falling edge of D-CLK.           PADJ2-O/I<br>PADJ2-O/I<br>PADJ2-O/I<br>PADJ2-O/I         of D-CLK. When the F/R pin is high, these pins are output pins and the output status<br>changes at the falling edge of D-CLK.           PADJ3-O/I         of D-CLK. When the F/R pin is low, these pins are output pins and the output status<br>changes at the falling edge of D-CLK.           D-CLK         I         Microcontroller         Anode output current adjusting data and anode output pulse width adjusting data transfer<br>clock input pin (Schmitt input)           STB         I         Microcontroller         Anode output current adjusting data and anode output pulse width adjusting data latch<br>strobe signal outputs: all "low"           RESET         I         Microcontroller         Anode output current adjusting data and anode output pulse width adjusting data latch<br>strobe signal outputs: all "low"           ALL H         I         Microcontroller         Shift register outputs and latch outputs: all "low"           ALL H         I         Microcontroller         Input pin for ano                                                                                                                                                                                                                                                                                                                                 |                 |     | ,               | changes at the falling edge of D-CLK.                                                                                       |

| MD0-0/I       Ori       When the F/R pin is high, these pins are input pins and data is read into at the rising edge of D-CLK. When the F/R pin is low, these pins are output pins and the output status changes at the falling edge of D-CLK.         PADJ0-I/O       Microcontroller, or ML3361 on next stage       Anode output pulse width adjusting data input-output pins.         PADJ0-O/I       Microcontroller, or ML3361 on next stage       Anode output pulse width adjusting data input-output pins.         PADJ0-O/I       PADJ0-O/I       Microcontroller, or ML3361 on next stage       Anode output pulse width adjusting data input-output pins.         PADJ2-O/I       O/I       Nicrocontroller, or ML3361 on next stage       Anode output pulse width adjusting data input-output pins.         PADJ3-O/I       O/I       Nicrocontroller, or ML3361 on next stage       Anode output pulse width adjusting data input-output pins.         PADJ3-O/I       Microcontroller, or MLS and the input pin Som data is read into at the rising edge of D-CLK.       When the F/R pin is low, these pins are output pins and the output status phab.         PADJ3-O/I       Microcontroller       Anode output current adjusting data and anode output pulse width adjusting data transfer clock input pin.         STB       I       Microcontroller       Anode output rurrent adjusting data and anode output pulse width adjusting data states:         • Shift register outputs and latch outputs: "high impedance."       Input pin for anode drive signal outputs: "high impedance." <tr< td=""><td></td><td></td><td></td><td>Anode output current adjusting data input-output pins.</td></tr<>                                                                                                                                                                                                                                                                                                                                                            |                 |     |                 | Anode output current adjusting data input-output pins.                                                                      |

| IADJ1-0/I       Microcontroller,         PADJ0-I/O       PADJ1-I/O         PADJ1-I/O       PADJ1-I/O         PADJ1-I/O       Microcontroller,         PADJ2-I/O       or         Microcontroller,       or         PADJ2-I/O       O/I         PADJ2-I/O       or         PADJ2-I/O       or         PADJ2-O/I       nitrocontroller <td>IADJ0-0/I</td> <td>0/1</td> <td>next stage</td> <td>When the F/R pin is high, these pins are input pins and data is read into at the rising edge</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | IADJ0-0/I       | 0/1 | next stage      | When the F/R pin is high, these pins are input pins and data is read into at the rising edge                                |

| PADJ0-I/O<br>PADJ1-V/O<br>PADJ2-V/O<br>PADJ2-V/O<br>PADJ3-V/O         V/O<br>PADJ3-V/O         Anode output pulse width adjusting data input-output pins.<br>When the F/R pin is low, these pins are input pins and data is read into at the rising edge<br>of D-CLK. When the F/R pin is low, these pins are output pins and the output status<br>PADJ3-O/I           PADJ3-O/I<br>PADJ2-O/I<br>PADJ2-O/I<br>PADJ3-O/I         O/I         Anode output pulse width adjusting data input-output pins.<br>When the F/R pin is low, these pins are output pins and the output status<br>PADJ3-O/I           D-CLK         I         Microcontroller<br>O/I         Anode output current adjusting data and anode output pins and the output status<br>PADJ3-O/I           D-CLK         I         Microcontroller<br>O-CLK. When the F/R pin is low, these pins are output pins and the output status<br>changes at the falling edge of D-CLK.           D-CLK         I         Microcontroller<br>Microcontroller         Anode output current adjusting data and anode output pulse width adjusting data transfer<br>clock input pin.           STB         I         Microcontroller         Anode output strument adjusting data and anode output pulse width adjusting data latch<br>strobe signal input pin.           RESET         I         Microcontroller         Nonde drive signal outputs: all 'inw'<br>- All anode drive signal outputs control signal.           ALL H <td>IADJ1-0/I</td> <td>0/1</td> <td></td> <td>of D-CLK. When the F/R pin is low, these pins are output pins and the output status</td>                                                                                                                 | IADJ1-0/I       | 0/1 |                 | of D-CLK. When the F/R pin is low, these pins are output pins and the output status                                         |

| PADJ1-I/O       I/O         PADJ2-I/O       I/O         Microcontroller       Microcontroller         PADJ3-I/O       Microcontroller         O/I       next stage         PADJ3-O/I       Microcontroller         Anode output pulse width adjusting data input-output pins.         When the F/R pin is high, these pins are input pins and data is read into at the rising edge of D-CLK.         PADJ3-O/I       Anode output current adjusting data and anode output pulse width adjusting data transfer clock input pin (Schmitt input)         STB       I       Microcontroller         Anode output current adjusting data and anode output pulse width adjusting data latch strobe signal input pin.         When the signal input pin.       When this pin is set low, the LSI enters the following initial setting states:         • Shift register outputs and latch outputs: all "low"       • All anode drive signal output control signal.         HZ       I       Microcontroller       Input pin for anode drive signal output control signal.         HZ       I       Microcontroller       Input pin for anode drive signal output control signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                 |     |                 | changes at the falling edge of D-CLK.                                                                                       |

| PADJ2-I/O         I/O           PADJ3-I/O         Microcontroller,<br>or ML9361/0         Microcontroller,<br>or ML9361/0         Microcontroller,<br>or ML9361/0         Microcontroller,<br>or ML9361/0         Microcontroller,<br>or ML9361/0         Microcontroller         Anode output pulse width adjusting data input-output pins.<br>When the F/R pin is high, these pins are output pins and the output status<br>changes at the falling edge of D-CLK.           D-CLK         I         Microcontroller         Anode output pulse width adjusting data and anode output pulse width adjusting data transfer<br>clock input pin (Schmitt input)           STB         I         Microcontroller         Anode output current adjusting data and anode output pulse width adjusting data latch<br>strobe signal input pin (Schmitt input)           RESET         I         Microcontroller         Anode output eurrent adjusting data and anode output pulse width adjusting data latch<br>strobe signal input pin (Schmitt input)           IIII         Microcontroller         Initialization signal input pin (Schmitt input)         Initialization signal input pin (Schmitt input)           RESET         I         Microcontroller         Input pin for anode drive signal outputs: and lato outputs are constant current output.           HZ         I         Microcontroller         Input pin for anode drive signal output control signal.         Microcontroller           ALL H         I         Microcontroller         Input pin for anode drive signal output control signal.         Mi                                                                                                                                                                                                                                                                                                                                                                                                                                                         | PADJ0-I/O       |     |                 | Anode output pulse width adjusting data input-output pins.                                                                  |

| PADJ2-I/O       Microcontroller,<br>PADJ3-I/O       Microcontroller,<br>or ML9361 on<br>next stage       Microcontroller,<br>or ML9361 on<br>next stage       Microcontroller,<br>PADJ-O/I       Microcontroller,<br>PADJ2-O/I       Anode output pulse width adjusting data input-output pins.         PADJ3-O/I       O/I       Microcontroller,<br>PADJ3-O/I       Microcontroller,<br>PADJ3-O/I       Anode output pulse width adjusting data input-output pins and data is read into at the rising edge<br>of D-CLK. When the F/R pin is low, these pins are output pulse width adjusting data transfer<br>clock input pin (Schmitt input)         STB       I       Microcontroller       Anode output current adjusting data and anode output pulse width adjusting data latch<br>strobe signal input pin (Schmitt input)         RESET       I       Microcontroller       Anode output current adjusting data and anode output pulse width adjusting data latch<br>strobe signal input pin (Schmitt input)         MEX       I       Microcontroller       Ned output current adjusting data and anode output pulse width adjusting data latch<br>strobe signal outputs: "high impedance"         HZ       I       Microcontroller       Input pin for anode drive signal outputs: "high impedance"         HZ       I       Microcontroller       Input pin for anode drive signal output control signal.<br>When this pin is high, all anode drive signal outputs are high impedance.         HZ       I       Microcontroller       Input pin for anode drive signal output control signal.<br>When this pin is high, anole drive signal output control signal.                                                                                                                                                                                                                                                                                                                                                                                                            | PADJ1-I/O       | 1/0 |                 | When the $\overline{F}/R$ pin is low, these pins are input pins and data is read into at the rising edge                    |

| Holdsolve       or ML39361 on next stage       Anode output pulse width adjusting data input-output pins.         PADJ2-0/I       O/I       Anode output pulse width adjusting data input-output pins.         When the F/R pin is high, these pins are input pins and data is read into at the rising edge of D-CLK. When the F/R pin is low, these pins are output pins and the output status changes at the falling edge of D-CLK.         D-CLK       I       Microcontroller       Anode output current adjusting data and anode output pulse width adjusting data transfer clock input pin (Schmitt input)         STB       I       Microcontroller       Anode output current adjusting data and anode output pulse width adjusting data latch strobe signal input pin (Schmitt input)         RESET       I       Microcontroller       Institut register outputs and latch outputs: all "low"         • All anode drive signal outputs:       "high impedance"       Input pin for anode drive signal output control signal.         MLL H       I       Microcontroller       Input pin for anode drive signal output control signal. (Schmitt input).         ALL H       I       Microcontroller       Input pin for anode drive signal output control signal.         Vhen this pin is high, all anode drive signal outputs are high impedance.       Input pin for anode drive signal output control signal.         ALL H       I       Microcontroller       Input pin for anode drive signal output control signal.         OFF HZ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | PADJ2-I/O       | 1/0 |                 | of D-CLK. When the F/R pin is high, these pins are output pins and the output status                                        |

| PADJ0-O/I<br>PADJ1-O/I<br>PADJ3-O/I       O/I       Inext stage       Anode output pulse width adjusting data input-output pins.<br>When the F/R pin is high, these pins are input pins and data is read into at the rising edge<br>of D-CLK. When the F/R pin is low, these pins are output pins and the output status<br>changes at the falling edge of D-CLK.         D-CLK       I       Microcontroller       Anode output current adjusting data and anode output pulse width adjusting data transfer<br>clock input pin (Schmitt input)         STB       I       Microcontroller       Anode output current adjusting data and anode output pulse width adjusting data latch<br>strobe signal input pin (Schmitt input)         RESET       I       Microcontroller       Anode output current adjusting data and anode output pulse width adjusting data latch<br>strobe signal input pin (Schmitt input)         HZ       I       Microcontroller       Anode drive signal outputs: "high impedance"         HZ       I       Microcontroller       Input pin for anode drive signal output control signal.<br>When this pin is low, all anode drive signal outputs are constant current output.         ALL H       I       Microcontroller       Input pin for anode drive signal output control signal (Schmitt input).         When this pin is high, all anode drive signal output control signal (Schmitt input).       When this pin is high, all anode drive signal output control signal.         ALL H       I       Microcontroller       Input pin for anode drive signal output control signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | PADJ3-I/O       |     |                 | changes at the falling edge of D-CLK.                                                                                       |

| PADJ1-0/I<br>PADJ2-0/I<br>PADJ2-0/I       O/I       IteXt stage       Andoe output plase within adjusting data input-output plass.         When the F/R pin is high, these pins are input pins and data is read into at the rising edge<br>of D-CLK. When the F/R pin is low, these pins are output pins and the output status<br>changes at the falling edge of D-CLK.         D-CLK       I       Microcontroller       Anode output current adjusting data and anode output pulse width adjusting data transfer<br>clock input pin (Schmitt input)         STB       I       Microcontroller       Anode output current adjusting data and anode output pulse width adjusting data latch<br>strobe signal input pin (Schmitt input)         RESET       I       Microcontroller       Initialization signal input pin<br>(Schmitt input)         MET       I       Microcontroller       Initialization signal outputs: migh impedance"         HZ       I       Microcontroller       Input pin for anode drive signal outputs: migh impedance.         HZ       I       Microcontroller       Input pin for anode drive signal outputs are constant current output.         HZ       I       Microcontroller       Input pin for anode drive signal outputs are constant current output.         HZ       I       Microcontroller       Input pin for anode drive signal output control signal.       When this pin is high, all anode drive signal outputs are high impedance.         ML H       I       Microcontroller       Input pin for anode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | PADJ0-0/I       |     |                 |                                                                                                                             |

| PADJ2-0/I       O/I       When the PM is the E/R bit is low, these pins are output pins and the output status changes at the falling edge of D-CLK.         PADJ3-0/I       Microcontroller       Anode output current adjusting data and anode output pulse width adjusting data transfer clock input pin (Schmitt input)         STB       I       Microcontroller       Anode output current adjusting data and anode output pulse width adjusting data latch strobe signal input pin (Schmitt input)         RESET       I       Microcontroller       Anode output current adjusting data and anode output pulse width adjusting data latch strobe signal input pin (Schmitt input)         RESET       I       Microcontroller       Initialization signal input pin       When this pin is set low, the LSI enters the following initial setting states:       • Shift register outputs and latch outputs: all "low"       • All anode drive signal output control signal.         HZ       I       Microcontroller       Input pin for anode drive signal output control signal.       When this pin is high, all anode drive signal outputs are constant current output.         ALL H       I       Microcontroller       Input pin for anode drive signal output control signal.       Unset output pins are output condition at the time that is OFF to either low or high impedance with the combination of A0 HZ, P L, and anode output pulse width adjusting data.         ALL H       I       Microcontroller       Input pin for anode drive signal output condition at the time that dot is OFF to either low or high impedance with                                                                                                                                                                                                                                                                                                                                                                                                                                 |                 |     | next stage      |                                                                                                                             |

| PADJ3-0/I         changes at the falling edge of D-CLK.           D-CLK         I         Microcontroller         Anode output current adjusting data and anode output pulse width adjusting data transfer clock input pin (Schmitt input)           STB         I         Microcontroller         Anode output current adjusting data and anode output pulse width adjusting data latch strobe signal input pin (Schmitt input)           RESET         I         Microcontroller         Initialization signal input pin.           When this pin is set low, the LSI enters the following initial setting states:         • Shift register outputs and latch outputs: "light impedance"           HZ         I         Microcontroller         Input pin for anode drive signal outputs are high impedance.           ALL H         I         Microcontroller         Input pin for anode drive signal outputs are constant current output.           MLL L         I         Microcontroller         Input pin for anode drive signal output control signal.           When this pin is high, all anode drive signal outputs are entrol tiput.         When this pin is high, anode drive signal outputs are all low.           Input pin for anode drive signal output control signal.         Used to set the anode drive signal output control signal.           VF HZ         I         Microcontroller         Input pin for anode drive signal output control signal.           OFF HZ         I         Microcontroller         In                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                 | O/I |                 | of D-CLK. When the E/R nin is low, these nins are output nins and the output status                                         |

| PAD3-SO/I       Import of the second se |                 |     |                 | changes at the falling edge of D-CLK.                                                                                       |

| DECLK       1       Microcontroller       clock input pin (Schmitt input)         STB       I       Microcontroller       Anode output current adjusting data and anode output pulse width adjusting data latch strobe signal input pin (Schmitt input)         RESET       I       Microcontroller       Initialization signal input pin.         When this pin is set low, the LSI enters the following initial setting states:       • Shift register outputs and latch outputs: "high impedance"         HZ       I       Microcontroller       Input pin for anode drive signal outputs: "high impedance"         ALL H       I       Microcontroller       Input pin for anode drive signal output control signal. (Schmitt input).         ALL H       I       Microcontroller       Input pin for anode drive signal output control signal (Schmitt input).         ALL L       I       Microcontroller       Input pin for anode drive signal output control signal (Schmitt input).         When this pin is high, all anode drive signal outputs are constant current output.       Input pin for anode drive signal output control signal.         OFF HZ       I       Microcontroller       Input pin for anode drive signal output control signal.         Vsed to set the anode drive signal output control signal.       Used to set the anode drive signal output control signal.         A0 HZ       I       Microcontroller       Input pin for anode drive signal output control signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | PADJ3-0/I       |     |                 |                                                                                                                             |

| STB       I       Microcontroller       strobe signal input pin (Schmitt input)         RESET       I       Microcontroller       Initialization signal input pin.         When this pin is set low, the LSI enters the following initial setting states:       • Shift register outputs and latch outputs: all "low"         • All anode drive signal outputs:       "high impedance"         Imput pin for anode drive signal outputs control signal.         When this pin is low, all anode drive signal outputs are high impedance.         Input pin for anode drive signal output control signal.         When this pin is high, all anode drive signal outputs are constant current output.         ALL H       I         Microcontroller       Input pin for anode drive signal output control signal.         Vhen this pin is high, all anode drive signal outputs are all low.         Input pin for anode drive signal output control signal.         OFF HZ       I         Microcontroller       Input pin for anode drive signal output control signal.         Used to set the anode drive signal output condition at the time that dot is OFF to either low or high impedance with the combination of AO HZ, P L, and anode output pulse width adjusting data.         A0 HZ       I       Microcontroller         P L       I       Microcontroller         Input pin for anode drive signal output condition at the time that dot is OFF to either low or high im                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | D-CLK           | I   | Microcontroller | Anode output current adjusting data and anode output pulse width adjusting data transfer<br>clock input pin (Schmitt input) |

| RESET       I       Microcontroller       Initialization signal input pin.<br>When this pin is set low, the LSI enters the following initial setting states:         HZ       I       Microcontroller       Shift register outputs and latch outputs: all "low"         HZ       I       Microcontroller       Input pin for anode drive signal output control signal.<br>When this pin is low, all anode drive signal outputs are high impedance.<br>Input pin for anode drive signal output control signal (Schmitt input).<br>When this pin is high, all anode drive signal outputs are constant current output.         ALL H       I       Microcontroller       Input pin for anode drive signal output control signal (Schmitt input).<br>When this pin is high, all anode drive signal outputs are constant current output.<br>When this pin is high, anode drive signal output control signal.         OFF HZ       I       Microcontroller       Input pin for anode drive signal output control signal.<br>Used to set the anode drive signal output condition at the time that is OFF to either low or high impedance with the combination of A0 HZ, P L, and anode output pulse width adjusting data.         A0 HZ       I       Microcontroller       Input pin for anode drive signal output condition at the time that dot is OFF to either low or high impedance with the combination of OFF HZ, P L, and anode output pulse width adjusting data.         P L       I       Microcontroller       Input pin for anode drive signal output control signal.<br>Used to set the anode drive signal output control signal.<br>Used to set the anode drive signal output control signal.<br>Used to set the anode drive signal output condition at the                                                                                                                                                                                                                                                                                                                   | STB             | I   | Microcontroller | Anode output current adjusting data and anode output pulse width adjusting data latch                                       |

| RESET       I       Microcontroller       When this pin is set low, the LSI enters the following initial setting states:<br>Shift register outputs and latch outputs: all "low" <ul> <li>All anode drive signal outputs: "high impedance"</li> <li>Input pin for anode drive signal output control signal.<br/>When this pin is low, all anode drive signal outputs are high impedance.<br/>When this pin is high, all anode drive signal outputs are constant current output.<br/>Microcontroller               ALL H             I             Microcontroller             Input pin for anode drive signal output control signal.<br/>When this pin is high, all anode drive signal outputs are constant current output.<br/>Microcontroller               ALL L             I             Microcontroller             Input pin for anode drive signal output control signal (Schmitt input).<br/>When this pin is high, anode drive signal outputs are all low.               ALL L             I             Microcontroller             Input pin for anode drive signal output control signal.<br/>Used to set the anode drive signal output control signal.<br/>Used to set the anode drive signal output control signal.<br/>Used to set the anode drive signal output control signal.<br/>Used to set the anode drive signal output control signal.<br/>Used to set the anode drive signal output control signal.<br/>Used to set the anode drive signal output control signal.<br/>Used to set the anode drive signal output control signal.<br/>Used to set the anode drive signal output control signal.<br/>Used to set the anode drive signal output condrition at the time that</li></ul>                                                                                                                                                                                                                                                                                                                                                                             |                 |     |                 |                                                                                                                             |

| RESET       I       Microcontroller       • Shift register outputs and latch outputs: all "low"         HZ       I       Microcontroller       Input pin for anode drive signal outputs control signal.<br>When this pin is low, all anode drive signal outputs are high impedance.         ALL H       I       Microcontroller       Input pin for anode drive signal output control signal (Schmitt input).<br>When this pin is high, all anode drive signal outputs are constant current output.         ALL L       I       Microcontroller       Input pin for anode drive signal output control signal (Schmitt input).<br>When this pin is high, anode drive signal outputs are all low.         OFF HZ       I       Microcontroller       Input pin for anode drive signal output control signal.<br>Used to set the anode drive signal output control signal.<br>Used to set the anode drive signal output condition at the time that is OFF to either low or<br>high impedance with the combination of A0 HZ, P L, and anode output pulse width<br>adjusting data.         A0 HZ       I       Microcontroller       Input pin for anode drive signal output condition at the time that dot is OFF to either<br>low or high impedance with the combination of OFF HZ, P L, and anode output pulse<br>width adjusting data.         P L       I       Microcontroller       Input pin for anode drive signal output condition at the time that dot is OFF to either<br>low or high impedance with the combination of OFF HZ, P L, and anode output pulse<br>width adjusting data.         P L       I       Microcontroller       Input pin for anode drive signal output condition at the time that dot                                                                                                                                                                                                                                                                                                                                                                     |                 |     |                 |                                                                                                                             |