# **OKI Semiconductor**

Network Solutions Oki. for a Global Society

FEDL9226-01 Issue Date: Dec. 11, 2002

# ML9226

32-Bit Duplex/Triplex VFD Controller/Driver with Digital Dimming, ADC and Keyscan

# **GENERAL DESCRIPTION**

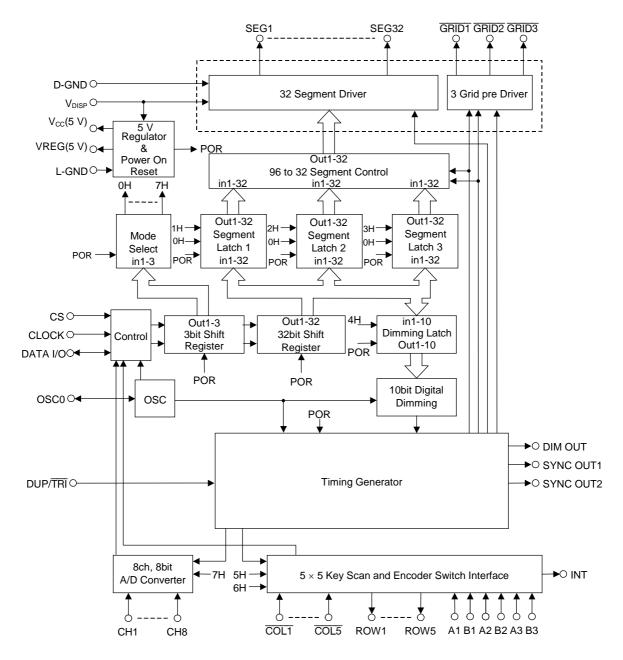

The ML9226 is a full CMOS controller/driver for Duplex or Triplex vacuum fluorescent display tube. It conststs of 32-segment driver outputs and 3-grid pre-driver outputs, so that it can drive directly up to 96-segment VFD. ML9226 features a digital dimming function, a 8-ch ADC, a  $5 \times 5$  keyscan circuit and an encoder type switch interface.

ML9226 provides an interface with a microcontroller only by four signal lines: DATA I/O, CLOCK, CS.

## FEATURES

| <ul> <li>Supply voltage (V<sub>DISP</sub>)</li> <li>Duplex/Triplex selectable</li> </ul> | : 8 to 18.5V (Built-in 5V regulator for logic)                                                                                                                                         |

|------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| • Applicable VFD tube                                                                    | : 2 Grids $\times$ 32 Anodes VFD tube                                                                                                                                                  |

|                                                                                          | : 3 Grids × 32 Anodes VFD tube                                                                                                                                                         |

| • 32-segment driver outputs                                                              | : $I_{OH} = -5$ mA at $V_{OH} = V_{DISP} - 0.8$ V (SEG1 to 22)<br>$I_{OH} = -10$ mA at $V_{OH} = V_{DISP} - 0.8$ V (SEG23 to 32)<br>$I_{OL} = 500$ uA at $V_{OL} = 2.0$ V (SEG1 to 32) |

| • 3-grid pre-driver outputs                                                              | : $I_{OH} = -5.0$ mA at $V_{OH} = V_{DISP} - 0.8V$<br>$I_{OL} = 10$ mA at $V_{OL} = 2.0V$                                                                                              |

| • Built-in digital dimming circuit (10-                                                  | -bit resolution)                                                                                                                                                                       |

| • Built-in 8-ch A/D converter                                                            |                                                                                                                                                                                        |

- Built-in 8-ch A/D converter

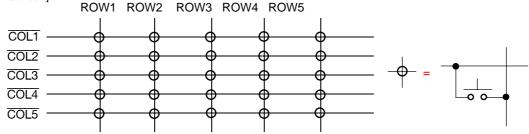

- Built-in  $5 \times 5$  keyscan circuit

- 3 interface circuits for an encoder type rotary switch

- Built-in oscillation circuit (external R and C)

- Built-in Power-On-Reset circuit

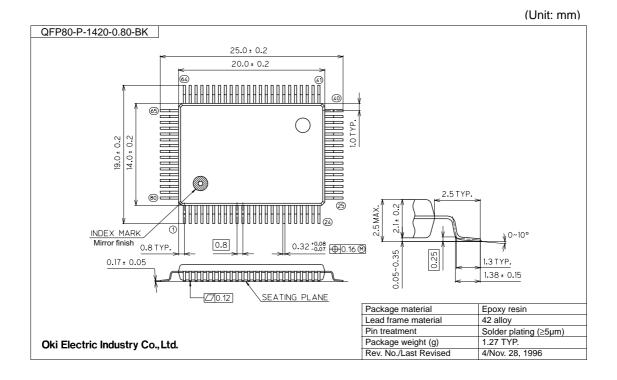

- Package:

80-pin plastic QFP (QFP80-P-1420-0.80-BK) ( ML9226GA)

#### **BLOCK DIAGRAM**

#### FEDL9226-01

ML9226

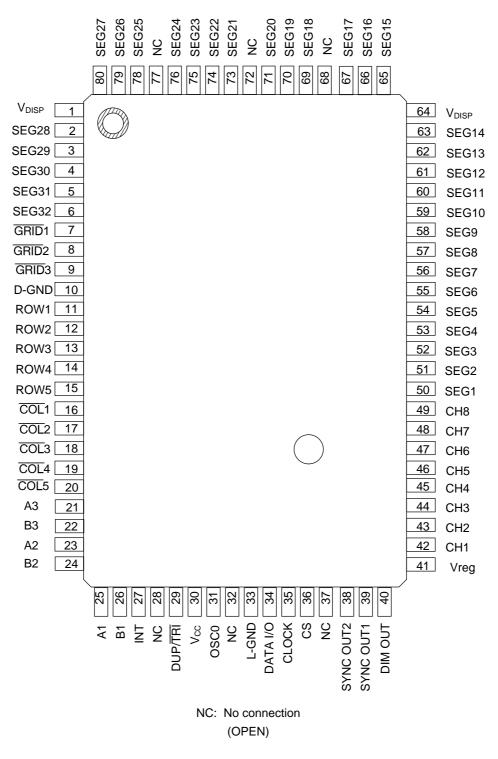

#### **PIN CONFIGURATION (TOP VIEW)**

80-pin Plastic QFP

#### **PIN DESCRIPTIONS**

| Pin                                           | Symbol                                     | Туре | Description                                                                                                                                                                                                                                                                                                       |

|-----------------------------------------------|--------------------------------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 64                                         | V <sub>DISP</sub>                          | —    | Power supply pins.<br>Pin1 and pin64 should be connected externally.                                                                                                                                                                                                                                              |

| 10                                            | D-GND                                      | _    | D-GND is ground pin for the VFD driver circuit. L-GND is ground pin for                                                                                                                                                                                                                                           |

| 33                                            | L-GND                                      | —    | the logic circuit. Pins 10 and 33 should be connected externally.                                                                                                                                                                                                                                                 |

| 30                                            | V <sub>cc</sub>                            | 0    | 5 V output pin for internal logic portion and external logic circuit.                                                                                                                                                                                                                                             |

| 41                                            | V <sub>REG</sub>                           | 0    | Reference voltage (5 V) output pin for A/D converter.                                                                                                                                                                                                                                                             |

| 50 to 63,<br>65 to 67,<br>69 to 71,<br>73, 74 | SEG1 to 22                                 | ο    | Segment (anode) signal output pins for a VFD tube. These pins can be directly connected to the VFD tube. External circuit is not required. $I_{OH} \le -5$ mA                                                                                                                                                     |

| 75, 76,<br>78 to 80,<br>2 to 6                | SEG23 to 32                                | 0    | Segment (anode) signal output pins for a VFD tube.<br>These pins can be directly connected to the VFD tube. External circuit is not required. $I_{OH} \le -10$ mA                                                                                                                                                 |

| 7, 8, 9                                       | GRID1 to 3                                 | 0    | Inverted Grid signal output pins. For pre-driver, the external circuit is requiend. $I_{OL} \leq 10 \text{ mA}$                                                                                                                                                                                                   |

| 36                                            | CS                                         | I    | Chip Select input pin.<br>Data input/output operation is valid when this pin is set at a High level.                                                                                                                                                                                                              |

| 35                                            | CLOCK                                      | I    | Serial clock input pin.<br>Data is input and/or output through the DATA I/O pin at the rising edge of<br>the serial clock.                                                                                                                                                                                        |

| 34                                            | DATA I/O                                   | I/O  | Serial data input/output pin.<br>Data is input to/comes out from the shift register at the rising edge of the serial clock.                                                                                                                                                                                       |

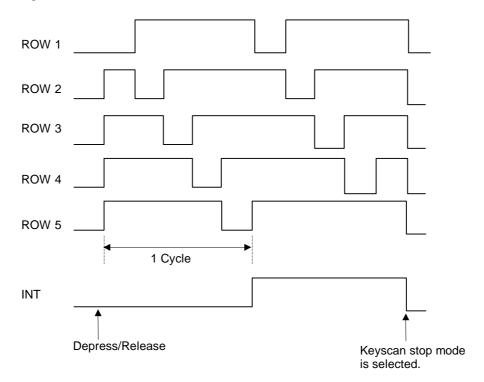

| 27                                            | INT                                        | 0    | Interrupt signal output to microcontroller. When any key of key matrix is pressed or released, key scanning is started. After the completion of the one cycle, this pin goes to high level and keeps the high level until keyscan stop mode is selected.                                                          |

| 29                                            | DUP/TRI                                    | I    | Duplex/Triplex operation select input pin.<br>Duplex (1/2 duty) operation is selected when this pin is set at a $V_{CC}$ level.<br>Triplex (1/3 duty) operation is selected when this pin is set at a GND level.                                                                                                  |

| 42 to 49                                      | CH1 to 8                                   | I    | Analog voltage input pin for the 8-bit A/D converter.                                                                                                                                                                                                                                                             |

| 21 to 26                                      | A1 to A3<br>B1 to B3                       | Ι    | Input pin for the encoder type rotary switch. The phase of an An/Bn input is detected.                                                                                                                                                                                                                            |

| 16 to 20                                      | $\overline{\text{COL1}}$ to $\overline{5}$ | I    | Return inputs from the key matrix.<br>These pins are active low. When key matrix are in the inactive sate, these<br>pins are at high level through the internal pull-up resistors. All the inputs<br>do not have the cahttering absorption function for the keyscans.                                             |

| 11 to 15                                      | ROW1 to 5                                  | 0    | Key switch scanning outputs.<br>Normally low level is output through these pin. When any switch of key<br>matrix is depressed or released, key scanning is started and is continued<br>until keyscan stop mode is selected. When keyscan stop mode is<br>selected, all outputs of ROW1 to 5 go back to low level. |

| Pin                       | Symbol        | Туре | Description                                                                                                                                            |

|---------------------------|---------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| 40                        | DIM OUT       | 0    | Dimming pulse output.<br>Connect this pin to the slave side DIM IN pin.                                                                                |

| 38, 39                    | SYNC OUT 1, 2 | 0    | Synchronous signal input.<br>Connect these pins to the SYNC IN1 and SYNC IN2 pins of a slave side.                                                     |

| 31                        | OSC0          | I/O  | RC oscillator connecting pins.<br>Oscillation frequency depends on display tubes to<br>be used.<br>For details refer to ELECTRICAL<br>CHARACTERISTICS. |

| 28,32,<br>37,68,<br>72,77 | NC            | -    | OPEN pins.                                                                                                                                             |

# ABSOLUTE MAXIMUM RATINGS

| Parameter           | Symbol            |                               | Condition            | Rating         | Unit |

|---------------------|-------------------|-------------------------------|----------------------|----------------|------|

| Supply Voltage      | V <sub>DISP</sub> |                               | —                    | -0.3 to +20    | V    |

| Input Voltage       | V <sub>IN</sub>   |                               | —                    | -0.3 to +6.0   | V    |

| Power Dissipation   | PD                | Ta = 85°C                     | QFP80-P-1420-0.80-BK | 263            | mW   |

| Storage Temperature | T <sub>STG</sub>  |                               | —                    | -55 to +150    | °C   |

|                     | I <sub>O1</sub>   |                               | SEG1 to 22           | -10.0 to +2.0  | mA   |

| Output Current      | I <sub>O2</sub>   |                               | SEG23 to 32          | -20.0 to +2.0  | mA   |

| Output Current      | I <sub>O3</sub>   | GRID1 to 3                    |                      | -10.0 to +20.0 | mA   |

|                     | I <sub>04</sub>   | DIM OUT, SYNC OUT1, SYNC OUT2 |                      | -2.0 to +2.0   | mA   |

# **RECOMMENDED OPERATING CONDITIONS**

| Parameter                | Symbol            | Condition                      | Min.     | Тур. | Max. | Unit |     |

|--------------------------|-------------------|--------------------------------|----------|------|------|------|-----|

| Driver Supply Voltage    | V <sub>DISP</sub> | —                              |          | 8.0  | 13.0 | 18.5 | V   |

| High Level Input Voltage | VIH               | All inputs except O            | SC0      | 3.8  | _    |      | V   |

| Low Level Input Voltage  | V <sub>IL</sub>   | All inputs except O            | SC0      | _    | _    | 0.8  | V   |

| Clock Frequency          | fc                | —                              |          | —    | —    | 2.0  | MHz |

| Oscillation Frequency    | fosc              | R = 10 k $\Omega$ ±5%, Co = 27 | 7 pF ±5% | 2.2  | 3.3  | 4.4  | MHz |

|                          | f                 | R = 10 kΩ ±5%                  | 1/3 Duty | 179  | 269  | 358  | Hz  |

| Frame Frequency          | f <sub>FR</sub>   | Co = 27 pF ±5% 1/2 Duty        |          | 268  | 403  | 538  | Hz  |

| Operating Temperature    | T <sub>OP</sub>   | _                              |          | -40  | _    | +85  | °C  |

## **ELECTRICAL CHARACTERISTICS**

#### **DC Characteristics**

|                              | (Ta = −40 to +85°C, V <sub>DISP</sub> = 8.0 to 18.5 \ |                                             |                                   |                                                                    |                         |      |      |  |  |

|------------------------------|-------------------------------------------------------|---------------------------------------------|-----------------------------------|--------------------------------------------------------------------|-------------------------|------|------|--|--|

| Parameter                    | Symbol                                                | Applied pin                                 | Co                                | ndition                                                            | Min.                    | Max. | Unit |  |  |

| High Level Input<br>Voltage  | VIH                                                   | *1)                                         |                                   | _                                                                  | 3.8                     | _    | V    |  |  |

| Low Level Input<br>Voltage   | VIL                                                   | *1)                                         |                                   | _                                                                  | _                       | 0.8  | V    |  |  |

| High Level Input             | I <sub>IH1</sub>                                      | *2)                                         | VIH                               | = 3.8 V                                                            | -5.0                    | +5.0 | μΑ   |  |  |

| Current                      | I <sub>IH2</sub>                                      | *3)                                         | VIH                               | = 3.8 V                                                            | -70                     | -5.0 | μA   |  |  |

| Low Level Input              | I <sub>IL1</sub>                                      | *2)                                         | V <sub>IL</sub>                   | = 0.0 V                                                            | -5.0                    | +5.0 | μΑ   |  |  |

| Current                      | I <sub>IL2</sub>                                      | *3)                                         | V <sub>IL</sub>                   | = 0.0 V                                                            | -160                    | -10  | μΑ   |  |  |

|                              | V <sub>OH1</sub>                                      | SEG1 to 22                                  | ]                                 | I <sub>ОН1</sub> = -5 mA                                           | $V_{\text{DISP}} - 0.8$ | _    | V    |  |  |

|                              | V <sub>OH2</sub>                                      | SEG23 to 32                                 |                                   | $I_{OH2} = -10 \text{ mA}$                                         | $V_{\text{DISP}} - 0.8$ | _    | V    |  |  |

| High Level<br>Output Voltage | V <sub>OH3</sub>                                      | $\overline{\text{GRID1}}$ to $\overline{3}$ | $V_{\text{DISP}} = 9.5 \text{ V}$ | $I_{\text{DISP}} = 9.5 \text{ V}$ $I_{\text{OH3}} = -5 \text{ mA}$ |                         |      | V    |  |  |

| Output Voltage               | V                                                     | *4)                                         |                                   | I <sub>OH4</sub> = -200 μA                                         | 4.0                     |      | V    |  |  |

|                              | V <sub>OH4</sub>                                      | 4)                                          |                                   | Output Open                                                        | 4.5                     |      | V    |  |  |

|                              | V <sub>OL1</sub>                                      | SEG1 to 22                                  |                                   | I <sub>OL1</sub> = 500 μA                                          | _                       | 2.0  | V    |  |  |

| Low Level                    | V <sub>OL2</sub>                                      | SEG23 to 32                                 | V <sub>DISP</sub> = 9.5 V         | I <sub>OL2</sub> = 500 μA                                          | _                       | 2.0  | V    |  |  |

| Output Voltage               | V <sub>OL3</sub>                                      | $\overline{\text{GRID1}}$ to $\overline{3}$ | $v_{\text{DISP}} = 9.5 \text{ v}$ | I <sub>OL3</sub> = 10 mA                                           | _                       | 2.0  | V    |  |  |

|                              | V <sub>OL4</sub>                                      | *5)                                         |                                   | I <sub>OL4</sub> = 300 μA                                          | _                       | 0.4  | V    |  |  |

| Supply Current               |                                                       | N/                                          | R = 10 kΩ ±5%                     | %, Co = 27 pF ±5%                                                  |                         | 10   |      |  |  |

| Supply Current               | IDISP                                                 | V <sub>DISP</sub>                           | no                                | no load                                                            |                         | 10   | mA   |  |  |

| Supply Voltage for Logic     | VL                                                    | V <sub>cc</sub>                             |                                   | 1 μF ± 10%,<br>to –10 mA                                           | 4.5                     | 5.5  | V    |  |  |

\*1) CS, CLOCK, DATA I/O DUP/TRI, A1 to A3, B1 to B3, COL1 to 5

\*2) CS, CLOCK, DATA I/O DUP/TRI, A1 to A3, B1 to B3

\*3)  $\overline{\text{COL1}}$  to  $\overline{5}$

\*4) DATA I/O, INT, DIM OUT, SYNC OUT1, SYNC OUT2 \*5) DATA I/O, INT, DIM OUT, SYNC OUT1, SYNC OUT2, ROW1 to 5

#### OKI Semiconductor

#### ML9226

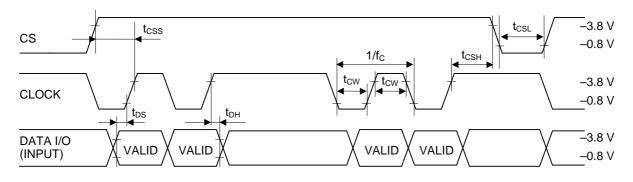

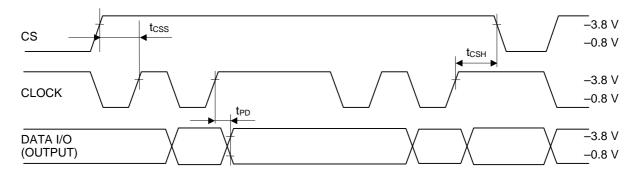

#### **AC Characteristics**

| $(1a = -40 \text{ to } +63 \text{ C}, \text{ v}_{\text{DISP}} = 8.0 \text{ to } 18.3 \text{ v}_{\text{DISP}}$ |                    |                                                      |                     |      |      |      |  |

|---------------------------------------------------------------------------------------------------------------|--------------------|------------------------------------------------------|---------------------|------|------|------|--|

| Parameter                                                                                                     | Symbol             | Conc                                                 | lition              | Min. | Max. | Unit |  |

| Clock Frequency                                                                                               | f <sub>C</sub>     | _                                                    | _                   |      | 2.0  | MHz  |  |

| Clock Pulse Width                                                                                             | t <sub>CW</sub>    | _                                                    | _                   | 200  |      | ns   |  |

| Data Setup Time                                                                                               | t <sub>DS</sub>    | -                                                    | _                   | 200  | _    | ns   |  |

| Data Hold Time                                                                                                | t <sub>DH</sub>    | -                                                    | _                   | 200  | _    | ns   |  |

| CS Off Time                                                                                                   | t <sub>CSL</sub>   | R = 10 kΩ ±5%,                                       | Co = 27 pF ±5%      | 20   |      | μS   |  |

| CS Setup Time<br>(CS-Clock)                                                                                   | t <sub>CSS</sub>   | _                                                    | 200                 | _    | ns   |      |  |

| CS Hold Time<br>(Clock-CS)                                                                                    | t <sub>CSH</sub>   | -                                                    | _                   | 200  | _    | ns   |  |

| DATA Output Delay Time<br>(Clock-DATA I/O)                                                                    | t <sub>PD</sub>    | -                                                    | _                   | _    | 1.0  | μS   |  |

| Output Slow Data Time                                                                                         | t <sub>R</sub>     | C 100 pF                                             | $t_R = 20\%$ to 80% |      | 2.0  | μS   |  |

| Output Slew Rate Time                                                                                         | t <sub>F</sub>     | $C_L = 100 \text{ pF}$ $t_F = 80\% \text{ to } 20\%$ |                     |      | 2.0  | μS   |  |

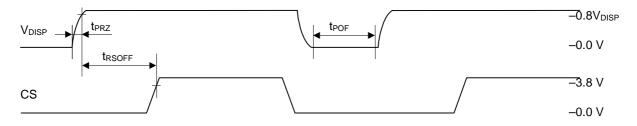

| V <sub>DISP</sub> Rise Time                                                                                   | t <sub>PRZ</sub>   | Mounted in a unit                                    |                     |      | 100  | μS   |  |

| V <sub>DISP</sub> Off Time                                                                                    | t <sub>POF</sub>   | Mounted in a ur                                      | 5.0                 |      | ms   |      |  |

| CS Wait Time                                                                                                  | t <sub>RSOFF</sub> | -                                                    | _                   | 400  |      | μS   |  |

#### **TIMING DIAGRAM**

#### **Data Input Timing**

#### **Data Output Timing**

#### **Reset Timing**

#### **Driver Output Timing**

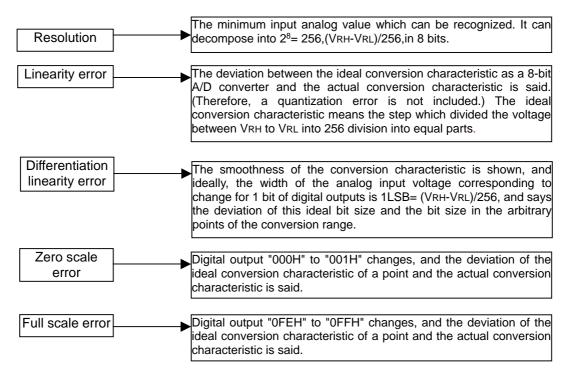

# A/D Converter Characteristics

|                                       |                                       | (Ta = –40 | 0 to +85°C, | V <sub>DISP</sub> = 8.0 t | o 18.5 V) |

|---------------------------------------|---------------------------------------|-----------|-------------|---------------------------|-----------|

| Parameter                             | Condition                             | Min.      | Тур.        | Max.                      | Unit      |

| Reference Voltage (V <sub>REG</sub> ) | —                                     | 4.5       | 5.0         | 5.5                       | V         |

| Output Current                        | —                                     | —         | —           | -10                       | mA        |

| Input Voltage Range                   | —                                     | GND       | —           | V <sub>REG</sub>          | V         |

| Conversion Time/Channel               | R = 10 k $\Omega$ ±5%, C2 = 27 pF ±5% | 256       | 310         | 394                       | μS        |

| Resolution                            |                                       | —         | —           | 8                         | bit       |

| Linearity error                       |                                       | —         | —           | ±2.0                      | LSB       |

| Differentiation linearity error       |                                       | —         | —           | ±2.0                      | LSB       |

| Zero scale error                      |                                       | _         | _           | +2.0                      | LSB       |

| Full-scale error                      |                                       | _         | _           | -2.0                      | LSB       |

#### Terminological definition

#### ML9226

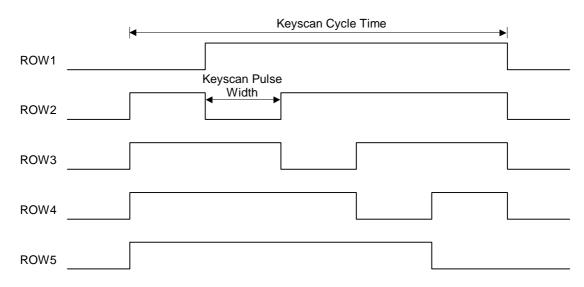

#### **Keyscan Characteristics**

#### $(Ta = -40 \text{ to } +85^{\circ}\text{C}, V_{\text{DISP}} = 8.0 \text{ to } 18.5 \text{ V})$

| Parameter           | Condition                             | Min. | Тур. | Max. | Unit |

|---------------------|---------------------------------------|------|------|------|------|

| Keyscan Cycle Time  | R = 10 k $\Omega$ ±5%, Co = 27 pF ±5% | 160  | 194  | 246  | μS   |

| Keyscan Pulse Width | R = 10 k $\Omega$ ±5%, Co = 27 pF ±5% | 32   | 39   | 49   | μS   |

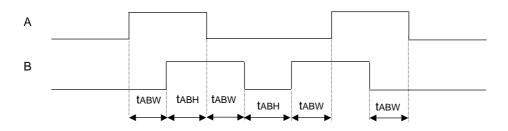

#### **Rotary switch characteristic**

$(Ta = -40 \text{ to } +85^{\circ}\text{C}, V_{\text{DISP}} = 8.0 \text{ to } 18.5 \text{ V})$

| Parameter              | Sign             | Condition                                           | Min. | Тур. | Max. | Unit |

|------------------------|------------------|-----------------------------------------------------|------|------|------|------|

| Phase input time       | t <sub>ABW</sub> | R = 10 kΩ ±5%, C <sub>O</sub> = 27 pF ±5%           | 950  |      |      |      |

| Phase input fixed time | t <sub>ABH</sub> | $R = 10 R2 \pm 5\%$ , $C_0 = 27 \text{ pr} \pm 5\%$ | 900  |      |      | μs   |

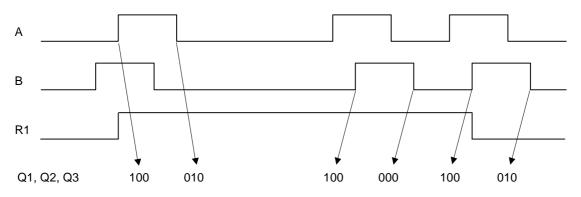

#### Rotary switch input timing

#### **Keyscan Timing**

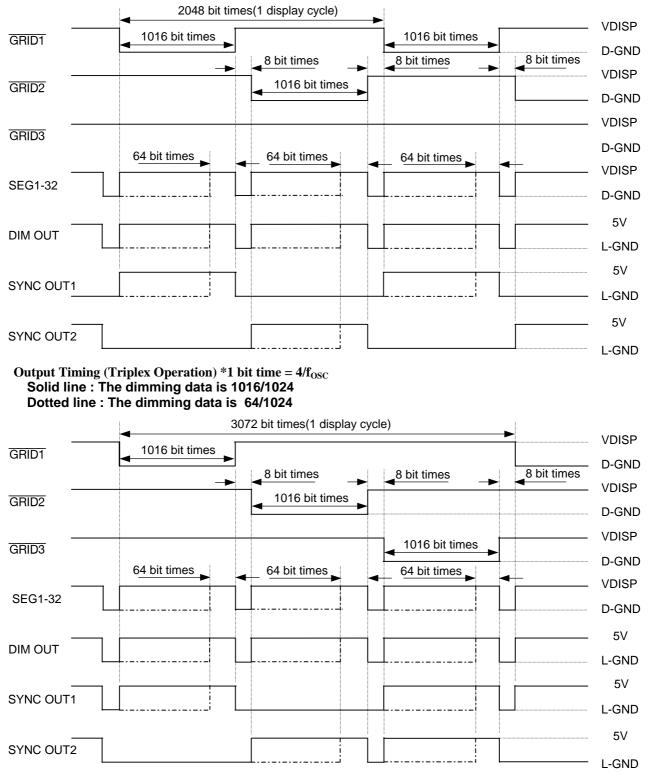

# $\begin{array}{l} Output \ Timing \ (Duplex \ Operation) \ *1 \ bit \ time = 4/f_{OSC} \\ Solid \ line : \ The \ dimming \ data \ is \ 1016/1024 \\ Dotted \ line : \ The \ dimming \ data \ is \ \ 64/1024 \end{array}$

#### FUNCTIONAL DESCRIPTION

#### **Power-on Reset**

When power is turned on, ML9226 is initialized by the internal power-on reset circuit. The status of the internal circuit after initialization is as follows:

- The contents of the shift registers and latches are set to "0".

- The contents of the sint registers and fatches are set to

The digital dimming duty cycle is set to "0".

- All segment outputs are set to Low level.

- All segment outputs are set to Low leve

- <u>GRID1</u> outputs are set to Low level.

- $\overline{\mathsf{GRID2}}$  to  $\overline{\mathsf{3}}$  outputs are set to High level.

- All the ROW outputs are set to Low level.

- INT output is set to Low level.

#### Mode Data

ML9226 has the seven function modes. The function mode is selected by the mode data (M0 to M2). The relation between function mode and mode data (M0 to M2) is as follows:

| FUNCTION MODE | OPERATING MODE                 | FUNCTION DATA |    |    |  |  |  |

|---------------|--------------------------------|---------------|----|----|--|--|--|

| FUNCTION MODE | OPERATING MODE                 | MO            | M1 | M2 |  |  |  |

| 0             | Segment Data for GRID1-3 Input | 0             | 0  | 0  |  |  |  |

| 1             | Segment Data for GRID1 Input   | 1             | 0  | 0  |  |  |  |

| 2             | Segment Data for GRID2 Input   | 0             | 1  | 0  |  |  |  |

| 3             | Segment Data for GRID3 Input   | 1             | 1  | 0  |  |  |  |

| 4             | Digital Dimming Data Input     | 0             | 0  | 1  |  |  |  |

| 5             | Keyscan Stop                   | 1             | 0  | 1  |  |  |  |

| 6             | Switch Data Output             | 0             | 1  | 1  |  |  |  |

| 7             | A/D Data Output                | 1             | 1  | 1  |  |  |  |

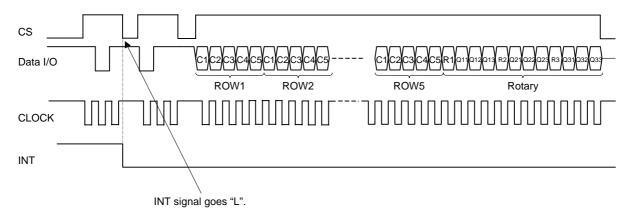

#### **Data Input and Output**

Data input and output through the DATA I/O pin is valid only when the CS pin is set at a High level.

The input data to DATA I/O pin is shifted into the shift register at the rising edge of the serial clock. The data is automatically loaded to the latches when the CS pin is set at a Low level.

10-bit dimming data (D1 to D10) and 32-bit segment data (S1 to S32) are used for inputting of dimming data and display data. To transfer these two data, the mode data (M0 to M2) must be sent after each of these data succeddingly.

The output data from the DATA I/O pin is output from the shift register at the rising edge of the serial clock.

ML9226 outputs 64-bit (8 ch  $\times$  8 bits) A/D data (A11 to A88) and 37-bit key data (S11 to S55, R1, Q11 to Q13, R2, Q21 to Q23, R3 and Q31 to Q33). To receive these data, the mode data (M0 to M2) mast be sent first and then CS must be set once to Low level and set again to High level.

Then inputting serial clocks, these data are output from the DATA I/O pin.

When the CS pin is set at a Low level, the DATA I/O pin returns to an input pin.

To stop the keyscan, the only mode data (M0 to M2) must be sent. After the mode data transfer, the key scanning is stopped immediately.

#### Segment Data Input [Function Mode: 0 to 3]

- ML9226 receives the segment data when function mode 0 to 3 are selected.

- The same segment data is transferred to the 3 segment data latch correspond to GRID1 to 3 at the same time when the function mode 0 is selected.

- The segment data is transferred to only one segment data latch that is selected by mode data, when the function mode is 1, 2 or 3 is selected.

- Segment output (SEG1 to 32) becomes High level when the segment data (S1 to 32) is High level.

#### [Data Format]

Input Data: 35 bitsSegment Data: 32 bitsMode Data: 3 bits

| Bit                                          | 1  | 2  | 3  | 4  |  | 29  | 30  | 31  | 32  | 33 | 34 | 35 |

|----------------------------------------------|----|----|----|----|--|-----|-----|-----|-----|----|----|----|

| Input Data                                   | S1 | S2 | S3 | S4 |  | S29 | S30 | S31 | S32 | M0 | M1 | M2 |

| LSBSegment Data (32 bits) Mode Data (3 bits) |    |    |    |    |  |     |     |     |     |    |    |    |

[Bit correspondence between segment output and segment data]

| SEG n           | 1   | 2   | 3   | 4   | 5   | 6   | 7   | 8   | 9   | 10  | 11  | 12  | 13  | 14  | 15  | 16  |

|-----------------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| Segment<br>data | S1  | S2  | S3  | S4  | S5  | S6  | S7  | S8  | S9  | S10 | S11 | S12 | S13 | S14 | S15 | S16 |

| SEG n           | 17  | 18  | 19  | 20  | 21  | 22  | 23  | 24  | 25  | 26  | 27  | 28  | 29  | 30  | 31  | 32  |

| Segment<br>data | S17 | S18 | S19 | S20 | S21 | S22 | S23 | S24 | S25 | S26 | S27 | S28 | S29 | S30 | S31 | S32 |

#### **Digital Dimming Data Input [Function Mode: 4]**

- ML9226 receives the digital dimming data when function mode 4 is selected.

- The output duty changes in the range of 0/1024 (0%) to 1016/1024 (99.2%) for each grid.

- The 10-bit digital dimming data is input from LSB.

[Data Format]

| Input Data           | : | 13 bits |

|----------------------|---|---------|

| Digital Dimming Data | : | 10 bits |

| Mode Data            | : | 3 bits  |

| Bit        | 1        | 2  | 3    | 4       | 5     | 6     | 7      | 8     | 9  | 10       | 11 | 12               | 13    |

|------------|----------|----|------|---------|-------|-------|--------|-------|----|----------|----|------------------|-------|

| Input Data | D1       | D2 | D3   | D4      | D5    | D6    | D7     | D8    | D9 | D10      | M0 | M1               | M2    |

|            | LSB<br>◀ |    | — Di | gital [ | Dimmi | ng Da | ta (10 | bits) | ·  | MSB<br>► |    | ode D<br>(3 bits | ata → |

| (LSB) |    |    |    | Dimmir | ng Data |    |    |    | (MSB) |            |

|-------|----|----|----|--------|---------|----|----|----|-------|------------|

| D1    | D2 | D3 | D4 | D5     | D6      | D7 | D8 | D9 | D10   | Duty Cycle |

| 0     | 0  | 0  | 0  | 0      | 0       | 0  | 0  | 0  | 0     | 0/1024     |

| 1     | 0  | 0  | 0  | 0      | 0       | 0  | 0  | 0  | 0     | 1/1024     |

|       |    |    |    | ÷      |         |    |    |    |       | ÷          |

| 1     | 1  | 1  | 0  | 1      | 1       | 1  | 1  | 1  | 1     | 1015/1024  |

| 0     | 0  | 0  | 1  | 1      | 1       | 1  | 1  | 1  | 1     | 1016/1024  |

| 1     | 0  | 0  | 1  | 1      | 1       | 1  | 1  | 1  | 1     | 1016/1024  |

|       |    |    |    | ÷      |         |    |    |    |       | ÷          |

| 1     | 1  | 1  | 1  | 1      | 1       | 1  | 1  | 1  | 1     | 1016/1024  |

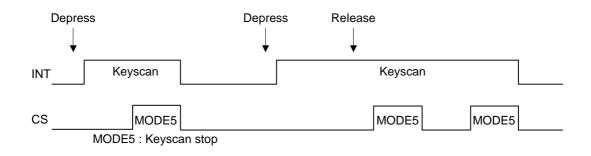

#### Keyscan Stop [Function Mode: 5]

- ML9226 stops a key scanning when function mode 5 are selected.

- To select this mode, the only mode data (M0 to M2) is needed.

- The actual time lag range between receipt of the keyscan stop command and the ceasing of scanning is 2.4  $\mu s$  to 3.6  $\mu s$

| [Ir | nput Data Forr<br>Input Dat<br>Mode Da | ta | : 3 bits<br>: 3 bits  |    |

|-----|----------------------------------------|----|-----------------------|----|

|     | Bit                                    | 28 | 29                    | 30 |

| _   | Input Data                             | MO | M1                    | M2 |

| _   |                                        | •  | Mode Data<br>(3 bits) |    |

#### Switch Data Output [Function Mode: 6]

- ML9226 output the switch data when function mode 6 is selected.

- To select this mode, the only mode data (M0 to M2) is needed.

- When ML9226 recieves this mode, the DATA I/O pin is changed to an output pin.

- 37-bit switch data come out from the DATA I/O pin synchronizing with the rise edge of the clock.

- When the CS pin is set at the low level, the DATA I/O pin returns to an input pin.

- R1, R2, R3 = 0, implies Right rotation of the knob (Clockwise)

- R1, R2, R3 = 1, implies Left rotation of the knob (Counter Clockwise)

- Contact Count bits are Q11 (LSB) to Q13 (MSB), Q21 (LSB) to Q23 (MSB) and Q31 (LSB) to Q33 (MSB)

#### [Input Data Format]

| Input Dat<br>Mode Da |    | : 3 bits<br>: 3 bits  |    |

|----------------------|----|-----------------------|----|

| Bit                  | 28 | 29                    | 30 |

| Input Data           | M0 | M1                    | M2 |

|                      | •  | Mode Data<br>(3 bits) | •  |

#### [Output Data Format]

| Output Data                   | : | 37 bits |

|-------------------------------|---|---------|

| $5 \times 5$ push swithe Data | : | 25 bits |

| Encoder switch Data           | : | 12 bits |

| Bit            | 1   | 2   | 3   | 4   | 5   | 6   | 7   | 8   | 9   | 10  | 11  | 12  | 13  | 14  | 15  | 16  | 17  | 18  | 19  | 20  | 21  | 22  | 23  | 24  | 25  |

|----------------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| Output<br>Data | S11 | S12 | S13 | S14 | S15 | S21 | S22 | S23 | S24 | S25 | S31 | S32 | S33 | S34 | S35 | S41 | S42 | S43 | S44 | S45 | S51 | S52 | S53 | S54 | S55 |

| Bit            | 26  | 27  | 28  | 29  | 30  | 31  | 32  | 33  | 34  | 35  | 36  | 37  |     |     |     |     |     |     |     |     |     |     |     |     |     |

| Output<br>Data | R1  | Q11 | Q12 | Q13 | R2  | Q21 | Q22 | Q23 | R3  | Q31 | Q32 | Q33 |     |     |     |     |     |     |     |     |     |     |     |     |     |

Sij: i = ROW1 to 5, j =  $\overline{\text{COL1}}$  to  $\overline{5}$

Sij = 1: Switch ON

Sij = 0: Switch OFF

[5x5 Push switch]

#### Keyscan

Keyscanning is started only when depression or release of any key is detected in order to minimize noise caused by scanning signal. Then, keyscanning is continued until the keyscan stop mode is sent from a microcomputer. The INT pin goes to the high level at the completion of 1-cycle scanning after the keyscan start, so the (high level) signal sent from the INT pin can be used as an interrupt signal.

[Keyscan Timing]

Note: Keyscanning cannot be stopped by selecting the keyscan stop mode only once if: - keyscanning is started after depression or release of any key is detected, and then - a key is depressed or released again before the keyscan stop mode is selected. To stop keyscanning, it is required to select the keyscan stop mode once again.

#### A/D Data Output [Function Mode: 7]

- ML9226 output the A/D data when function mode 7 is selected.

- To select this mode, the only mode data (M0 to M2) is needed.

- When ML9226 recieves this mode, the DATA I/O pin is changed to an output pin.

- 64-bit A/D data come out from the DATA I/O pin synchronizeing with the rise edge of the clock.

- When the CS pin is set at the low level, the DATA I/O pin returns to an input pin.

#### [Input Data Format]

| Input Dat<br>Mode Da |    | : 3 bits<br>: 3 bits  |    |

|----------------------|----|-----------------------|----|

| Bit                  | 28 | 29                    | 30 |

| Input Data           | M0 | M1                    | M2 |

|                      | •  | Mode Data<br>(3 bits) |    |

# [Output Data Format]

| Output Data | : 64 bits |

|-------------|-----------|

| A/D Data    | : 64 bits |

| Bit    | 1     | 2   | 3   | 4   | 5            | 6   | 7   | 8     | 9     | 10  | 11  | 12  | 13  | 14  | 15  | 16    |

|--------|-------|-----|-----|-----|--------------|-----|-----|-------|-------|-----|-----|-----|-----|-----|-----|-------|

| Output | A11   | A12 | A13 | A14 | A15          | A16 | A17 | A18   | A21   | A22 | A23 | A24 | A25 | A26 | A27 | A28   |

| Data   | (LSB) |     |     |     |              |     |     | (MSB) | (LSB) |     |     |     |     |     |     | (MSB) |

| A/D    |       |     | •   | CI  | -<br>-<br>11 | -   |     |       | CH2   |     |     |     |     |     |     |       |

| Bit    | 17    | 18  | 19  | 20  | 21           | 22  | 23  | 24    | 25    | 26  | 27  | 28  | 29  | 30  | 31  | 32    |

| Output | A31   | A32 | A33 | A34 | A35          | A36 | A37 | A38   | A41   | A42 | A43 | A44 | A45 | A46 | A47 | A48   |

| Data   | (LSB) |     |     |     |              |     |     | (MSB) | (LSB) |     |     |     |     |     |     | (MSB) |

| A/D    | CH3   |     |     |     |              |     |     |       | CH4   |     |     |     |     |     |     |       |

| Bit    | 33    | 34  | 35  | 36  | 37           | 38  | 39  | 40    | 41    | 42  | 43  | 44  | 45  | 46  | 47  | 48    |

| Output | A51   | A52 | A53 | A54 | A55          | A56 | A57 | A58   | A61   | A62 | A63 | A64 | A65 | A66 | A67 | A68   |

| Data   | (LSB) |     |     |     |              |     |     | (MSB) | (LSB) |     |     |     |     |     |     | (MSB) |

| A/D    |       |     |     | Cl  | H5           |     |     |       |       |     |     | CI  | H6  |     |     |       |

| Bit    | 49    | 50  | 51  | 52  | 53           | 54  | 55  | 56    | 57    | 58  | 59  | 60  | 61  | 62  | 63  | 64    |

| Output | A71   | A72 | A73 | A74 | A75          | A76 | A77 | A78   | A81   | A82 | A83 | A84 | A85 | A86 | A87 | A88   |

| Data   | (LSB) |     |     |     |              |     |     | (MSB) | (LSB) |     |     |     |     |     |     | (MSB) |

| A/D    |       |     |     | CI  | -<br>-<br>17 |     |     |       | CH8   |     |     |     |     |     |     |       |

#### The rotary encoder switch function.

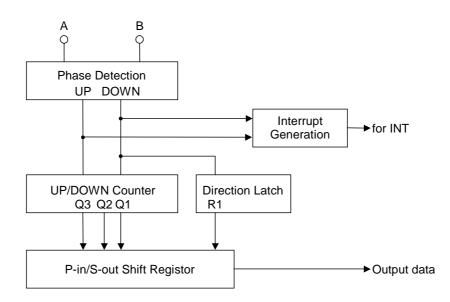

As figure 1 shows, the rotary encoder switch circuit is consisted of Phase detection, Interrupt generation, Up/down counter, Direction latch and Parallel-in serial-out shift register.

Fig.1 The Rotary Encoder Switch Circuit

1) Phase detection

#### 1-1) Clockwise

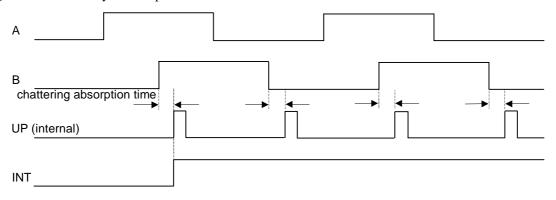

When signal A and B input as fig. 2, the phase detection circuit outputs UP signal after the chattering absorption period. At this time, the output INT also goes to high level, so this signal can be used as an interrupt. The INT stays High level until the key scan stop mode is selected.

Fig.2 The Input and Output Timing in Case of Clockwise.

#### **OKI** Semiconductor

# 1-2) counter clockwise

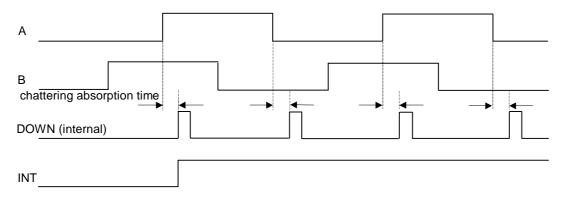

When signal A and B input as fig. 3, the phase detection circuit outputs Down signal after the chattering absorption period. At this time, the output INT also goes to High level. The INT stays High level until the key scan stop mode is selected.

#### Fig.3 The Input and Output Timing in Case of Counter Clockwise.

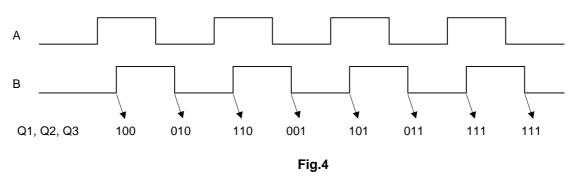

#### 2) UP/DOWN COUNTER

When the UP/DOWN COUNTER is input UP, it counts up and when it is input DOWN, it counts down. But if overcounte of "111" occurs the UP/DOWN COUNTER stays "111".

3) Direction latch

When the Direction latch is input DOWN the output R goes "1". But if the UP pulse is input and the counts value change to plus value, the output R goes to "0".

#### **OKI** Semiconductor

#### 4) P-in/S-out shift resistor

When the key scan stop mode is selected and SC goes L, INT signal goes "L".

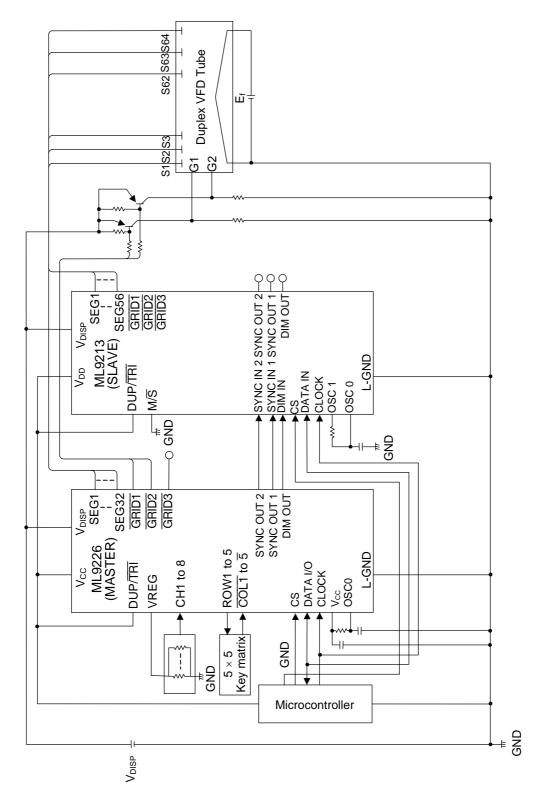

#### 1. Circuit for the duplex VFD tube with 128 segments (2 Grid × 64 Anode)

# S62 S63 S64 Triplex VFD Tube ш S1 S2 S3 588 --SEG56 GRID1 GRID2 GRID2 GRID3 SEG1 V<sub>DD</sub> V<sub>DISP</sub> ML9213 (SLAVE) L-GND DUP/TRI M/S OSC 0 GND € GND + <u>GRID2</u> <u>GRID3</u> DUP/TRI SYNC OUT 2 SYNC OUT 1 DIM OUT L-GND ROW1 to 5 ► COL1 to 5 CS DATA I/O CLOCK CH1 to 8 Vcc VREG V<sub>cc</sub> OSC0 4 5 × 5 Key matrix -11 GND į GND Microcontroller GND≇ V<sub>DISP</sub>

#### 2. Circuit for the triplex VFD tube with 192 segments (3 Grid × 64 Anode)

## PACKAGE DIMENSIONS

Notes for Mounting the Surface Mount Type Package

The surface mount type packages are very susceptible to heat in reflow mounting and humidity absorbed in storage.

Therefore, before you perform reflow mounting, contact Oki's responsible sales person for the product name, package name, pin number, package code and desired mounting conditions (reflow method, temperature and times).

# **REVISION HISTORY**

| Doc  | Document<br>No. |               | Pa                  | ge                 |                       |

|------|-----------------|---------------|---------------------|--------------------|-----------------------|

|      |                 | Date          | Previous<br>Edition | Current<br>Edition | Description           |

| FEDL | .9226-01        | Dec. 11, 2002 | _                   | Ι                  | Preliminary edition 1 |

#### NOTICE

- 1. The information contained herein can change without notice owing to product and/or technical improvements. Before using the product, please make sure that the information being referred to is up-to-date.

- 2. The outline of action and examples for application circuits described herein have been chosen as an explanation for the standard action and performance of the product. When planning to use the product, please ensure that the external conditions are reflected in the actual circuit, assembly, and program designs.

- 3. When designing your product, please use our product below the specified maximum ratings and within the specified operating ranges including, but not limited to, operating voltage, power dissipation, and operating temperature.

- 4. Oki assumes no responsibility or liability whatsoever for any failure or unusual or unexpected operation resulting from misuse, neglect, improper installation, repair, alteration or accident, improper handling, or unusual physical or electrical stress including, but not limited to, exposure to parameters beyond the specified maximum ratings or operation outside the specified operating range.

- 5. Neither indemnity against nor license of a third party's industrial and intellectual property right, etc. is granted by us in connection with the use of the product and/or the information and drawings contained herein. No responsibility is assumed by us for any infringement of a third party's right which may result from the use thereof.

- 6. The products listed in this document are intended for use in general electronics equipment for commercial applications (e.g., office automation, communication equipment, measurement equipment, consumer electronics, etc.). These products are not, unless specifically authorized by Oki, authorized for use in any system or application that requires special or enhanced quality and reliability characteristics nor in any system or application where the failure of such system or application may result in the loss or damage of property, or death or injury to humans.

Such applications include, but are not limited to, traffic and automotive equipment, safety devices, aerospace equipment, nuclear power control, medical equipment, and life-support systems.

- 7. Certain products in this document may need government approval before they can be exported to particular countries. The purchaser assumes the responsibility of determining the legality of export of these products and will take appropriate and necessary steps at their own expense for these.

- 8. No part of the contents contained herein may be reprinted or reproduced without our prior permission.

Copyright 2002 Oki Electric Industry Co., Ltd.