# OKI Semiconductor ML9059

**PEDL9059-02** Issue Date: Dec. 27, 2004

# Preliminary

# 132-Channel LCD Driver with Built-in RAM for LCD Dot Matrix Displays

# **GENERAL DESCRIPTION**

The ML9059 is an LSI for dot matrix graphic LCD devices carrying out bit map display. This LSI can drive a dot matrix graphic LCD display panel under the control of an 8-bit microcomputer (hereinafter described MPU). Since all the functions necessary for driving a bit map type LCD device are incorporated in a single chip, using the ML9059 makes it possible to realize a bit map type dot matrix graphic LCD display system with only a few chips. Since the bit map method in which one bit of display RAM data turns ON or OFF one dot in the display panel, it is possible to carry out displays with a high degree of freedom such as Chinese character displays, etc. With one chip, it is possible to construct a graphic display system with a maximum of  $49 \times 132$  dots. The display can be expanded further using two chips. However, the ML9059 is not used in a multiple chip configuration when a line reversal drive is set.

The ML9059 is made using a CMOS process. Because it has a built-in RAM, low power consumption is one of its features, and is therefore suitable for displays in battery-operated portable equipment.

The ML9059 has 49 common signal outputs and 132 segment signal outputs and one chip can drive a display of up to  $49 \times 132$  dots.

# FEATURES

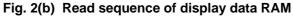

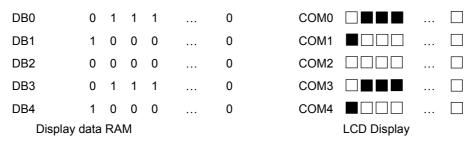

- Direct display of the RAM data using the bit map method Display RAM data "1" ... Dot is displayed Display RAM data "0" ... Dot is not displayed (during forward display)

- Display RAM capacity  $65 \times 132 = 8580$  bits

- LCD Drive circuits

- 49 common outputs, 132 segment outputs

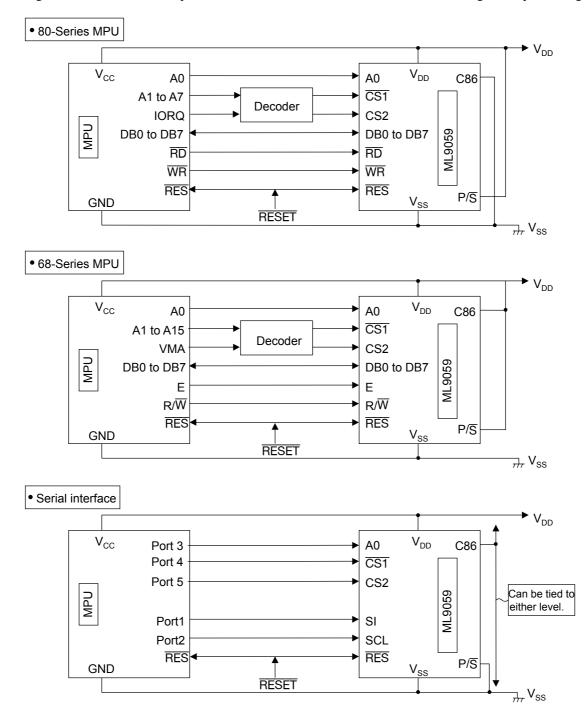

- MPU interface: Can select an 8-bit parallel or serial interface

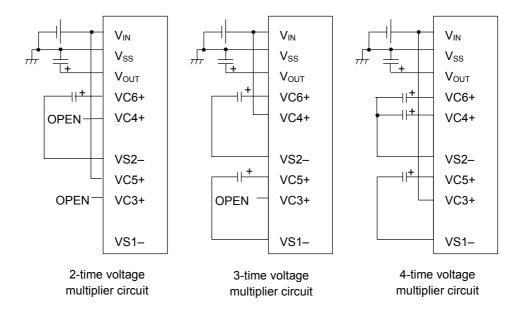

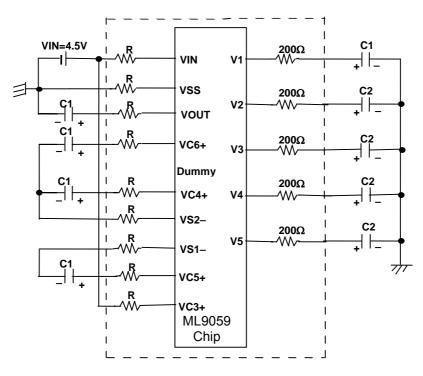

- Built-in voltage multiplier circuit for the LCD drive power supply

- Built-in LCD drive voltage adjustment circuit

- Built-in LCD drive bias generator circuit

- Can select frame reversal drive or line reversal drive by command

- Built-in oscillator circuit (Internal RC oscillator/external clock input)

- A variety of commands

Read/write of display data, display ON/OFF, forward/reverse display, all dots ON/all dots OFF, set page address, set display start address, etc.

- Power supply voltage

Logic power supply: VDD-VSS = 3.7 V to 5.5 V

Voltage multiplier reference voltage: VIN-VSS = 3.7 V to 5.5 V

(2- to 4-time multiplier available)

LCD Drive voltage: VBI-VSS = 6.0 to 18 V

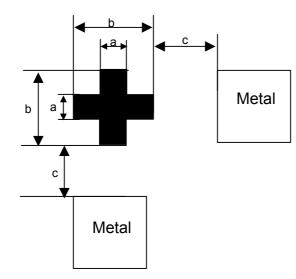

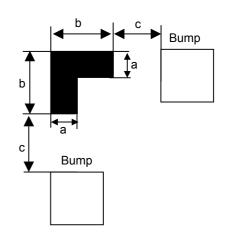

- Package : Gold bump chip (Bump hardness: Low, DV) : Gold bump chip (Bump hardness: High, CV)

- This device is not resistant to radiation and light.

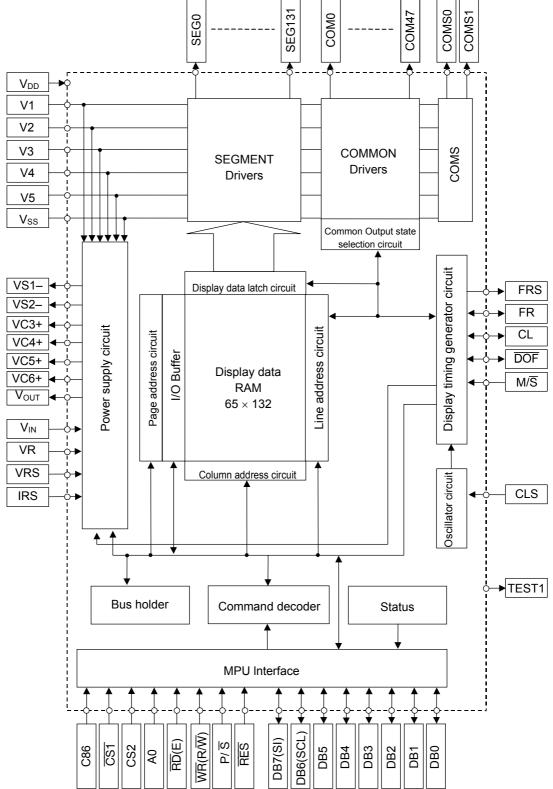

# **BLOCK DIAGRAM**

|                                      |                  |                                                                         |                                              |      | V <sub>SS</sub> = 0 V |

|--------------------------------------|------------------|-------------------------------------------------------------------------|----------------------------------------------|------|-----------------------|

| Parameter                            | Symbol           | Condition                                                               | Rated value                                  | Unit | Applicable pins       |

| Power supply voltage                 | V <sub>DD</sub>  | Tj = 25°C                                                               | -0.3 to +6.5                                 | V    | V <sub>DD</sub>       |

| Bias voltage                         | V <sub>BI</sub>  | Tj = 25°C                                                               | -0.3 to +20                                  | V    | V1 to V5              |

| Voltage multiplier output voltage    | V <sub>OUT</sub> | Tj = 25°C                                                               | –0.3 to +20                                  | V    | V <sub>OUT</sub>      |

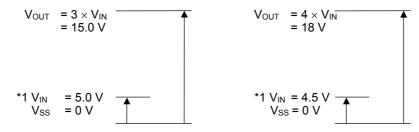

| Voltage multiplier reference voltage | V <sub>IN</sub>  | 2-time multiplication<br>3-time multiplication<br>4-time multiplication | -0.3 to +5.5<br>-0.3 to +5.5<br>-0.3 to +5.0 | v    | V <sub>IN</sub>       |

| Input voltage                        | VI               | Tj = 25°C                                                               | –0.3 to V <sub>DD</sub> +0.3                 | V    | All inputs            |

| Storage temperature range            | T <sub>STG</sub> | Chip                                                                    | -55 to +125                                  | °C   | —                     |

# ABSOLUTE MAXIMUM RATINGS

Tj: Chip surface temperature

# **RECOMMENDED OPERATING CONDITIONS**

|                                      |                  |                                                                         |                                        |      | $V_{SS} = 0 V$   |

|--------------------------------------|------------------|-------------------------------------------------------------------------|----------------------------------------|------|------------------|

| Parameter                            | Symbol           | Condition                                                               | Rated value                            | Unit | Applicable pins  |

| Power supply voltage                 | V <sub>DD</sub>  |                                                                         | 3.7 to 5.5                             | V    | V <sub>DD</sub>  |

| Bias voltage                         | V <sub>BI</sub>  |                                                                         | 6 to 18                                | V    | V1 to V5         |

| Voltage multiplier reference voltage | V <sub>IN</sub>  | 2-time multiplication<br>3-time multiplication<br>4-time multiplication | 3.7 to 5.5<br>3.7 to 5.5<br>3.7 to 4.5 | v    | V <sub>IN</sub>  |

| Voltage multiplier output voltage    | V <sub>OUT</sub> | External input                                                          | 6.0 to 18                              | V    | V <sub>OUT</sub> |

| Operating temperature range          | T <sub>JOP</sub> | —                                                                       | -40 to +85                             | °C   | —                |

Note 1: The electrical characteristics are influenced by COG trace resistance. This LSI always has to be evaluated before using.

Note 2: The voltages  $V_{DD}$ , V1 to V5, and  $V_{OUT}$  are values taking  $V_{SS} = 0$  V as the reference.

Note 3: The highest bias potential is V1 and the lowest is  $V_{SS}$ .

Note 4: Always maintain the relationship  $V1 \ge V2 \ge V3 \ge V4 \ge V5 \ge V_{SS}$  among these voltages.

**OKI** Semiconductor

| Note 5: | When using an external power supply, follow the procedure for power application.               |

|---------|------------------------------------------------------------------------------------------------|

|         | When applying external power to the $V_{OUT}$ pin only, apply $V_{OUT}$ after $V_{DD}$ .       |

|         | When applying external power to the V1 pin only, apply V1 after V <sub>DD</sub> .              |

|         | When applying external power to the V1 pin to V5 pin, apply V1 to V5 after $V_{DD}$ .          |

|         | Note that the above (Note 4) must be satisfied including transient state at power application. |

| Note 6: | When using an external power supply, follow the procedure for power removal described below.   |

|         | When external power is in use for the $V_{OUT}$ pin only, remove $V_{OUT}$ after $V_{DD}$ .    |

|         | When external power is in use for the V1 pin only, remove V1 after V <sub>DD</sub> .           |

|         | When external power is in use for the V1 pin to V5 pin, remove V1 to V5 after $V_{DD}$ .       |

|         | Note that the above (Note 4) must be satisfied including transient state at power removal.     |

# **ELECTRICAL CHARACTERISTICS**

# **DC** Characteristics

| [V <sub>SS</sub> = 0 V, V <sub>DD</sub> = 3.7 to 5.5 V, Tj =–40 to +85°C] |                                        |                  |                             |                           |       |                            |      |                                                |  |

|---------------------------------------------------------------------------|----------------------------------------|------------------|-----------------------------|---------------------------|-------|----------------------------|------|------------------------------------------------|--|

| Para                                                                      | meter                                  | Symbol           | Condition                   | Min                       | Тур   | Max                        | Unit | Applicable<br>pins                             |  |

| "H" Inpu                                                                  | it voltage                             | V <sub>IH</sub>  |                             | $0.8\times V_{\text{DD}}$ | —     | V <sub>DD</sub>            | V    | *1                                             |  |

| "L" Inpu                                                                  | t voltage                              | VIL              |                             | 0                         | _     | $0.2 \times V_{\text{DD}}$ | v    | . I                                            |  |

| "H" Inpu                                                                  | it voltage                             | VIH              |                             | $0.8\times V_{\text{DD}}$ |       | V <sub>DD</sub>            |      |                                                |  |

| "L" Inpu                                                                  | t voltage                              | VIL              |                             | 0                         | —     | $0.2 \times V_{\text{DD}}$ | V    | *2                                             |  |

| Hystere                                                                   | sis width                              | ΔV               | V <sub>DD</sub> = 5.0 V     | -                         | 1.0   | —                          |      |                                                |  |

| "H" outpu                                                                 | ut voltage                             | V <sub>OH</sub>  | I <sub>OH</sub> = –0.5 mA   | $0.8\times V_{\text{DD}}$ | —     | —                          | v    | *3                                             |  |

| "L" outpu                                                                 | ut voltage                             | V <sub>OL</sub>  | I <sub>OL</sub> = 0.5 mA    | —                         | —     | $0.2 \times V_{\text{DD}}$ | v    | 3                                              |  |

| "H" Inpu                                                                  | it current                             | I <sub>IH</sub>  | $V_1 = V_{DD}$              | -1.0                      | —     | +1.0                       | •    | *4 *5                                          |  |

| "L" Inpu                                                                  | t current                              | IIL              | V <sub>1</sub> = 0 V        | -3.0                      | _     | +3.0                       | μA   | *4 *5                                          |  |

| •                                                                         | V1 output voltage temperature gradient |                  | Tj = 25°C<br>V1 = 12 V      | _                         | -0.05 | _                          | %/°C | V1                                             |  |

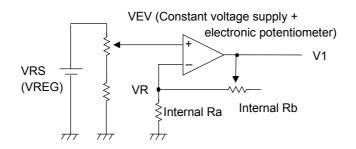

| Reference                                                                 | ce voltage                             | V <sub>REG</sub> | Tj = 25°C                   | 2.925                     | 3.00  | 3.075                      | V    | V <sub>RS</sub>                                |  |

| V1 outpu                                                                  | ut voltage                             | V1               | *6                          | 10.58                     | 10.85 | 11.12                      | V    | V1                                             |  |

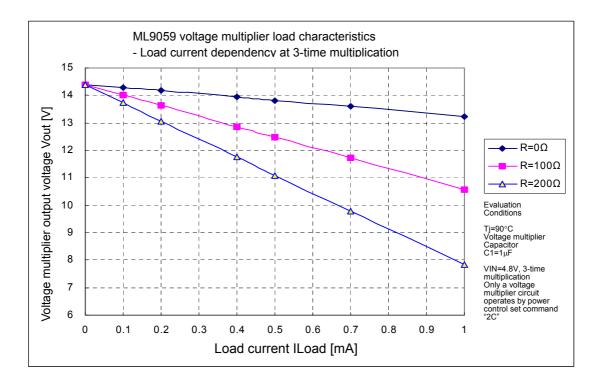

| Voltage                                                                   | multiplier                             | Vout             | 3-time<br>multiplication *7 | 13.0                      | —     | —                          | V    | V <sub>OUT</sub>                               |  |

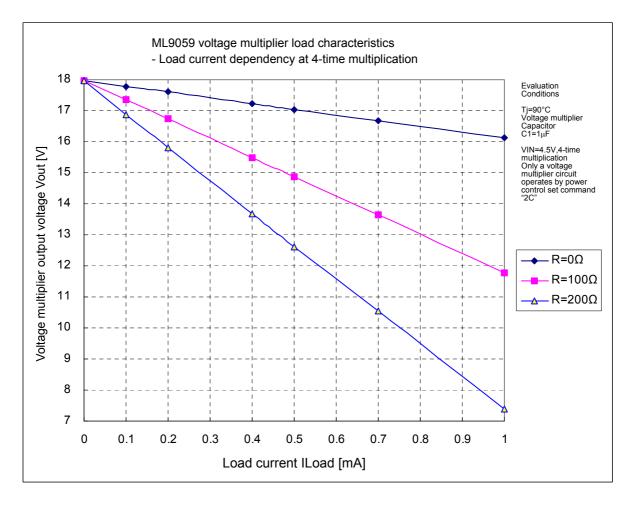

| output                                                                    | voltage                                | VOUT             | 4-time<br>multiplication *8 | 15.9                      | _     | —                          | V    | V <sub>OUT</sub>                               |  |

| V <sub>OUT</sub> - V                                                      | 1 voltage                              | Vot1             | *9                          | 0.6                       | —     | —                          | V    | V <sub>OUT,</sub> V1                           |  |

|                                                                           | LCD driver ON resistance               |                  | Ι <sub>Ο</sub> = ±50 μΑ     | _                         | —     | 10                         | kΩ   | SEG1 to 131,<br>COMS0,<br>COMS1,<br>COM0 to 47 |  |

|                                                                           | Internal                               | f                | Ti - 25°C                   | 27                        | 33    | 39                         | kHz  | *10                                            |  |

| Oscillator                                                                | oscillation                            | fosc             | Tj = 25°C                   | 21                        | —     | 47                         | kHz  |                                                |  |

| frequency                                                                 | External<br>input                      | f <sub>EXT</sub> |                             | 14                        | 17    | 20                         | kHz  | CL*10                                          |  |

\*1: DB0 to DB5, DB7 (SI), FR, DOF Pins

- \*2: A0, CS1, CS2, CLS, M/S, C86, P/S, IRS, RD (E), WR (R/W), RES, CL, DB6 (SCL) Pins

- \*3: DB0 to DB7, FR, FRS, DOF, CL Pins

- \*4: A0,  $\overline{RD}$  (E),  $\overline{WR}$  (R/ $\overline{W}$ ),  $\overline{CS1}$ , CS2, CLS, M/ $\overline{S}$ , C86, P/ $\overline{S}$ ,  $\overline{RES}$ , IRS Pins

- \*5: Applicable to the pins DB0 to DB5, DB6 (SCL), DB7 (SI), CL, FR, DOF in the high impedance state.

- \*6:  $Tj = 25^{\circ}C$ ,  $\alpha = 31$ , (1+Rb/Ra) = 4,  $V_{OUT} = 13.5 V$  (External input), LCD drive output = no-load

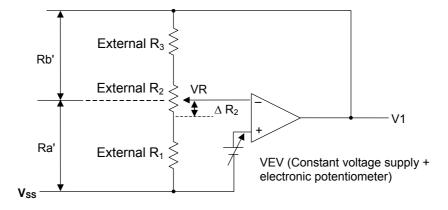

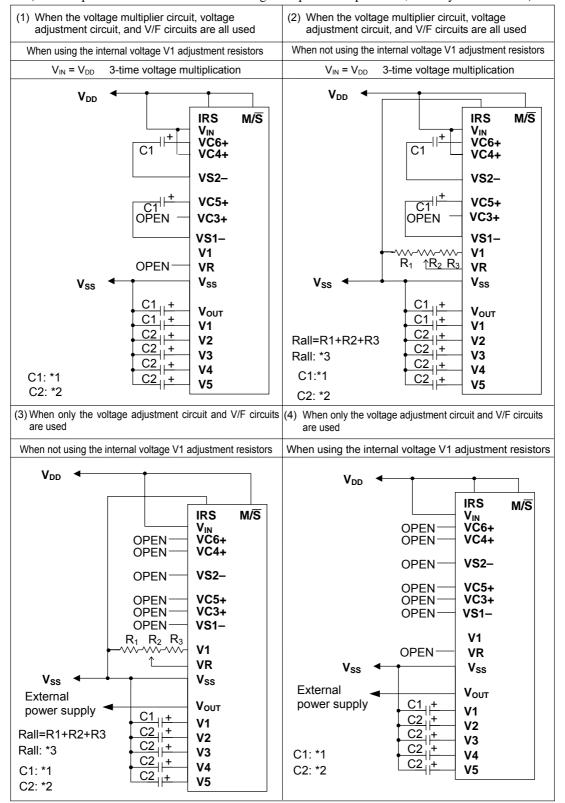

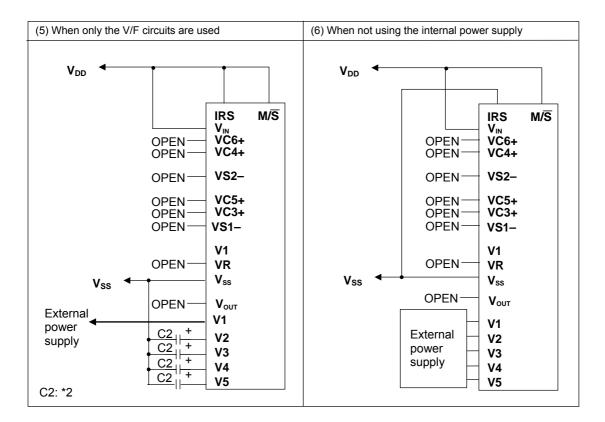

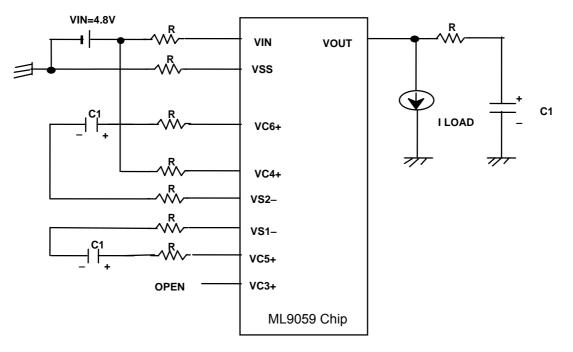

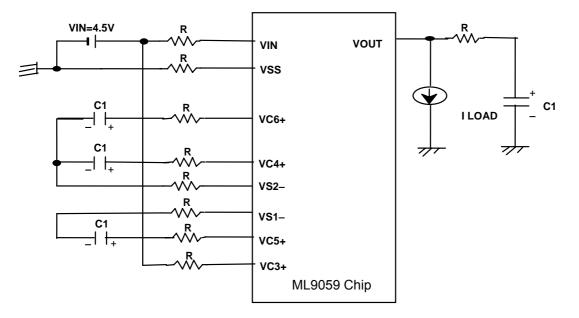

- \*7:  $V_{IN} = 4.8 \text{ V}$ , voltage multiplier capacitor  $C1 = 2.6 \text{ to } 4.0 \mu\text{F}$ , voltage multiplier output load current  $I = 500 \mu\text{A}$ . Only a voltage multiplier circuit operates, not activating the voltage adjustment circuit and V/F circuit, by command "2C".

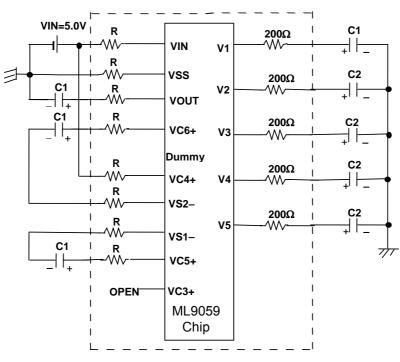

- \*8:  $V_{IN} = 4.5 \text{ V}$ , voltage multiplier capacitor  $C1 = 2.6 \text{ to } 4.0 \mu\text{F}$ , voltage multiplier output load current  $I = 500 \mu\text{A}$ . Only a voltage multiplier circuit operates, not activating the voltage adjustment circuit and V/F circuit, by command "2C".

\*9: V1 load current I = 400  $\mu$ A. 8 V is externally input to V<sub>OUT</sub>.

The voltage adjustment circuit and V/F circuit operate by command "2B". LCD output = no load \*10: See Table 1 for the relationship between the oscillator frequency and the frame frequency.

# Table 1. Relationship among the oscillator frequency (f<sub>osc</sub>), external input frequency (fEXT) display clock frequency (fLCDCK), and LCD frame frequency (f<sub>FR</sub>)

|        | Parameter                                | Display clock frequency<br>(f <sub>LCDCK</sub> ) | LCD frame frequency<br>(f <sub>FR</sub> ) |  |  |

|--------|------------------------------------------|--------------------------------------------------|-------------------------------------------|--|--|

| ML9059 | When the internal oscillator is used     | f <sub>OSC</sub> /8                              | $f_{OSC}/(8 \times 49)$                   |  |  |

| ML9039 | When the internal oscillator is not used | f <sub>EXT</sub> /4                              | f <sub>EXT</sub> /(4× 49)                 |  |  |

# • Operating current consumption value

(1) During display operation, internal power supply OFF (The current flowing through  $V_{DD}$  with V1 to V5 externally applied when an external power supply is used, not including the current for the LCD drive)  $[V_{SS} = 0 V, Tj = 25^{\circ}C]$

|                     |                 |                                               |     | [Vs         | s = 0 V, | $IJ = 25^{\circ}C$ |  |

|---------------------|-----------------|-----------------------------------------------|-----|-------------|----------|--------------------|--|

| Diantes: made       | Symbol          | O and the r                                   |     | Rated value |          |                    |  |

| Display mode Symbol |                 | Condition                                     | Min | Тур         | Max      | Unit               |  |

|                     | I               | $V_{DD}$ = 5 V, V1- $V_{SS}$ = 11 V, no load  |     | 16          | 45       | ۸                  |  |

| All-white           | I <sub>DD</sub> | $V_{DD}$ = 3.7 V, V1- $V_{SS}$ = 8 V, no load |     | 12          | 35       | μΑ                 |  |

| Chocker pattern     | 1               | $V_{DD}$ = 5 V, V1- $V_{SS}$ = 11 V, no load  |     | 16          | 45       | ۸                  |  |

| Checker pattern     | I <sub>DD</sub> | $V_{DD}$ = 3.7 V, V1- $V_{SS}$ = 8 V, no load |     | 12          | 35       | μΑ                 |  |

| (2) During display operation, internal power supply | ON (Total of currents flowing through $V_{DD}$ and $V_{IN}$ ) |

|-----------------------------------------------------|---------------------------------------------------------------|

|                                                     | [V <sub>SS</sub> = 0 V, Tj = 25°C]                            |

| Display            |                                                                                                                        |                                                                                                                        |   | D   | ated va        |     |      |

|--------------------|------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|---|-----|----------------|-----|------|

| mode               | Symbol                                                                                                                 | Condition                                                                                                              | n | Min | ацей Vа<br>Тур | Max | Unit |

|                    |                                                                                                                        | Frame reversal,<br>$V_{DD,} V_{IN} = 5 V$ , 3-time<br>voltage multiplication<br>V1 - V <sub>SS</sub> = 11 V, no load   |   | _   | 100            | 170 |      |

| All-white          | I <sub>DDIN</sub>                                                                                                      | Frame reversal,<br>$V_{DD,} V_{IN} = 3.7 V, 4$ -time<br>voltage multiplication<br>V1 - V <sub>SS</sub> = 8 V, no load  |   | _   | 110            | 190 | μΑ   |

|                    | 16-line reversal,<br>$V_{DD,} V_{IN} = 5 V$ , 3-time<br>voltage multiplication<br>V1 - V <sub>SS</sub> = 11 V, no load |                                                                                                                        | _ | 100 | 170            |     |      |

|                    |                                                                                                                        | Frame reversal,<br>$V_{DD,} V_{IN} = 5 V$ , 3-time<br>voltage multiplication<br>V1 - V <sub>SS</sub> = 11 V, no load   |   |     | 120            | 205 |      |

| Checker<br>pattern | I <sub>DDIN</sub>                                                                                                      | Frame reversal,<br>$V_{DD,} V_{IN} = 3.7 V$ , 4-time<br>voltage multiplication<br>V1 - V <sub>SS</sub> = 8 V, no load  |   | _   | 130            | 220 | μΑ   |

|                    |                                                                                                                        | 16-line reversal,<br>$V_{DD,} V_{IN} = 5 V$ , 3-time<br>voltage multiplication<br>V1 - V <sub>SS</sub> = 11 V, no load |   | _   | 120            | 205 |      |

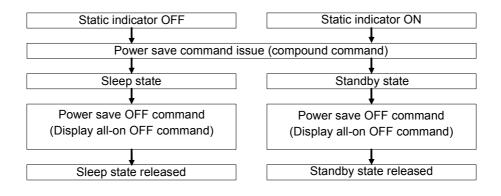

# • Power save mode current consumption

| - Tower save mode current consumption |                   |                         |     |           |     |      |  |  |

|---------------------------------------|-------------------|-------------------------|-----|-----------|-----|------|--|--|

| [V <sub>SS</sub> = 0 V, Tj = 25°C]    |                   |                         |     |           |     |      |  |  |

| Parameter                             | Symbol            |                         |     | ated valu | le  | Unit |  |  |

|                                       | Symbol            | Condition               | Min | Тур       | Max | Unit |  |  |

| Sleep mode                            | I <sub>DDS1</sub> | V <sub>DD</sub> = 3.7 V | _   | 0.3       | 5   | ۸    |  |  |

| Standby mode                          | I <sub>DDS2</sub> | V <sub>DD</sub> = 3.7 V |     | 9         | 15  | μA   |  |  |

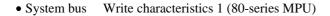

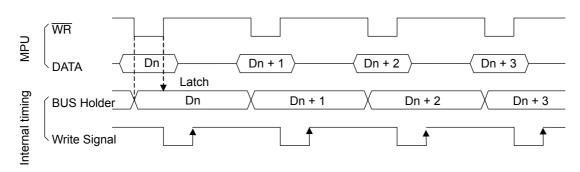

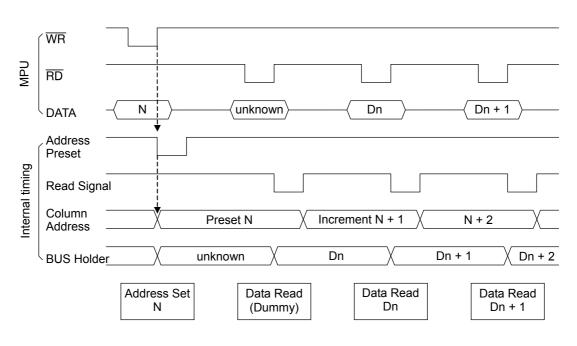

# **Parallel Interface Timing Characteristics**

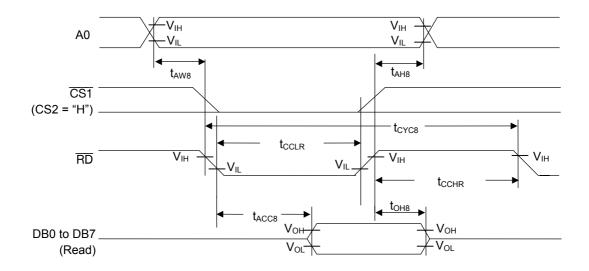

• System bus Read characteristics 1 (80-series MPU)

# **OKI** Semiconductor

#### $[V_{DD} = 4.5 \text{ to } 5.5 \text{ V}, \text{ Tj} = -40 \text{ to } +85^{\circ}\text{C}]$

|                            |                          |             | <u> </u> |      |      |

|----------------------------|--------------------------|-------------|----------|------|------|

| Parameter                  | Symbol                   | Condition   | Rated    | Unit |      |

| Faranieter                 | Symbol                   | Condition   | Min      | Max  | Onit |

| Address hold time          | t <sub>AH8</sub>         |             | 5        |      |      |

| Address setup time         | t <sub>AW8</sub>         |             | 5        | —    |      |

| System cycle time          | t <sub>CYC8</sub>        |             | 166      |      |      |

| Control L pulse width (WR) | t <sub>CCLW</sub>        |             | 30       | —    |      |

| Control L pulse width (RD) | t <sub>CCLR</sub>        |             | 70       | _    |      |

| Control H pulse width (WR) | t <sub>CCHW</sub>        |             | 55       |      | ns   |

| Control H pulse width (RD) | <b>t</b> <sub>CCHR</sub> |             | 55       | —    |      |

| Data setup time            | t <sub>DS8</sub>         |             | 30       | _    |      |

| Data hold time             | t <sub>DH8</sub>         |             | 10       | —    |      |

| RD Access time             | t <sub>ACC8</sub>        | CL = 100 pF |          | 70   |      |

| Output disable time        | t <sub>OH8</sub>         | CL = 100 pF | 5        | 50   |      |

# $[V_{DD} = 3.7 \text{ to } 4.5 \text{ V}, \text{ Tj} = -40 \text{ to } +85^{\circ}\text{C}]$

|                            | Symbol            |                          | Rated | Linit |      |

|----------------------------|-------------------|--------------------------|-------|-------|------|

| Parameter                  | Symbol            | Condition                | Min   | Max   | Unit |

| Address hold time          | t <sub>AH8</sub>  |                          | 5     | _     |      |

| Address setup time         | t <sub>AW8</sub>  |                          | 5     | _     |      |

| System cycle time          | t <sub>CYC8</sub> |                          | 300   | —     |      |

| Control L pulse width (WR) | t <sub>CCLW</sub> |                          | 60    | —     |      |

| Control L pulse width (RD) | t <sub>CCLR</sub> |                          | 120   | —     |      |

| Control H pulse width (WR) | t <sub>CCHW</sub> |                          | 60    | _     | ns   |

| Control H pulse width (RD) | t <sub>CCHR</sub> |                          | 60    | —     |      |

| Data setup time            | t <sub>DS8</sub>  |                          | 40    | _     |      |

| Data hold time             | t <sub>DH8</sub>  |                          | 15    | _     |      |

| RD Access time             | t <sub>ACC8</sub> | $C_{1} = 100 \text{ pc}$ |       | 140   |      |

| Output disable time        | t <sub>OH8</sub>  | CL = 100 pF              | 10    | 100   |      |

Note 1: The input signal rise and fall times are specified as 15ns or less. When using the system cycle time for fast speed, the specified values are  $(tr + tf) \le (t_{CYC8} - t_{CCLW} - t_{CCHW})$ or  $(tr + tf) \le (t_{CYC8} - t_{CCLR} - t_{CCHR})$ . Note 2: All timings are specified taking the levels of 20% and 80% of V<sub>DD</sub> as the reference.

Note 3: The values of  $t_{CCLW}$  and  $t_{CCLR}$  are specified during the overlapping period of  $\overline{CS1}$  at "L" (CS2 = "H") and the "L" levels of  $\overline{WR}$  and  $\overline{RD}$ , respectively.

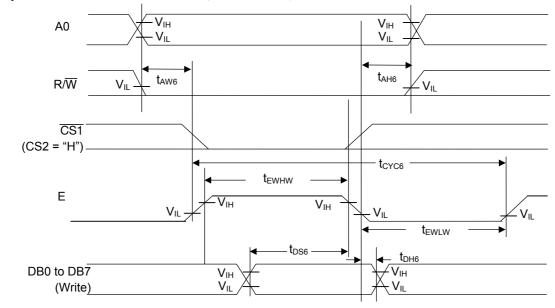

• System bus Write characteristics 2 (68-series MPU)

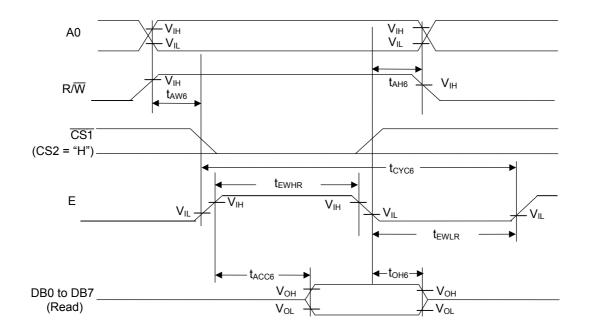

• System bus Read characteristics 2 (68-series MPU)

#### $[V_{DD} = 4.5 \text{ to } 5.5 \text{ V}, \text{ Tj} = -40 \text{ to } +85^{\circ}\text{C}]$

|                      |           | Symbol            |             | Rated value |     |      |

|----------------------|-----------|-------------------|-------------|-------------|-----|------|

| Parameter            | Parameter |                   | Condition   | Min         | Max | Unit |

| Address hold time    |           | t <sub>AH6</sub>  |             | 5           |     |      |

| Address setup time   |           | t <sub>AW6</sub>  |             | 5           |     |      |

| System cycle time    |           | t <sub>CYC6</sub> |             | 166         | _   |      |

| Data setup time      |           | t <sub>DS6</sub>  |             | 30          | _   |      |

| Data hold time       |           | t <sub>DH6</sub>  |             | 10          | _   |      |

| Access time          |           | t <sub>ACC6</sub> | CL = 100 pF | _           | 70  | ns   |

| Output disable time  |           | t <sub>OH6</sub>  |             | 10          | 50  |      |

| Enable H pulse width | Read      | t <sub>EWHR</sub> |             | 70          | _   |      |

| Enable H pulse width | Write     | t <sub>EWHW</sub> |             | 30          | —   |      |

|                      | Read      | t <sub>EWLR</sub> |             | 60          |     |      |

| Enable L pulse width | Write     | t <sub>EWLW</sub> |             | 60          | _   |      |

#### [V<sub>DD</sub> = 3.7 to 4.5 V. Ti = -40 to +85°C]

|                      |                   |                   | $v_{DD} = 3.7 \text{ to } 4$ | 1           |     | +05 0] |  |

|----------------------|-------------------|-------------------|------------------------------|-------------|-----|--------|--|

| Parameter            |                   | Symbol            | Condition                    | Rated value |     | Unit   |  |

|                      |                   |                   | Condition                    | Min         | Max | Onic   |  |

| Address hold time    | Address hold time |                   |                              | 5           |     |        |  |

| Address setup time   |                   | t <sub>AW6</sub>  |                              | 5           | —   |        |  |

| System cycle time    |                   | t <sub>CYC6</sub> |                              | 300         | —   |        |  |

| Data setup time      |                   | t <sub>DS6</sub>  |                              | 40          | —   |        |  |

| Data hold time       | Data hold time    |                   |                              | 15          | —   |        |  |

| Access time          |                   | t <sub>ACC6</sub> | CL = 100 pF                  | —           | 140 | ns     |  |

| Output disable time  |                   | t <sub>OH6</sub>  | CL = 100 pP                  | 10          | 100 |        |  |

| Enable H pulse width | Read              | t <sub>EWHR</sub> |                              | 120         |     |        |  |

|                      | Write             | t <sub>EWHW</sub> |                              | 60          | —   |        |  |

| Enable L pulse width | Read              | t <sub>EWLR</sub> |                              | 60          |     |        |  |

|                      | Write             | t <sub>EWLW</sub> |                              | 60          |     |        |  |

Note 1: The input signal rise and fall times are specified as 15ns or less.

When using the system cycle time for fast speed, the specified values are  $(tr + tf) \le (t_{CYC6} - t_{EWLW} - t_{EWHW})$ or  $(tr + tf) \le (t_{CYC6} - t_{EWLR} - t_{EWHR})$ . Note 2: All timings are specified taking the levels of 20% and 80% of V<sub>DD</sub> as the reference.

Note 3: The values of  $t_{EWLW}$  and  $t_{EWLR}$  are specified during the overlapping period of  $\overline{CS1}$  at "L" (CS2 = "H") and the "H" level of E.

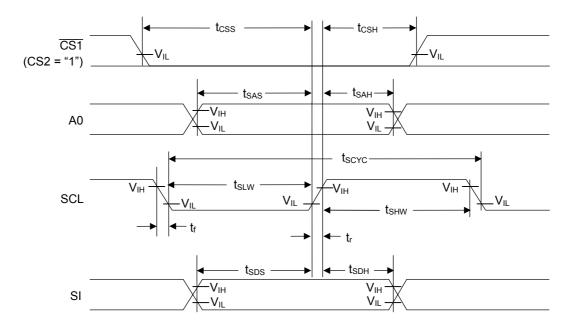

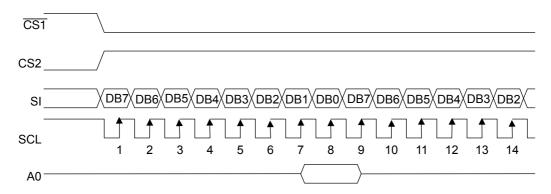

# Serial Interface Timing Characteristics

• Serial interface

|                     |                  |                              | • · , · j | 10 10 | 00 01 |  |

|---------------------|------------------|------------------------------|-----------|-------|-------|--|

| Parameter           | Symbol           | Symbol Condition Rated value |           | value | Unit  |  |

| Falameter           | Symbol           | Condition                    | Min       | Max   | Unit  |  |

| Serial clock period | tscyc            |                              | 200       | —     |       |  |

| SCL "H" Pulse width | t <sub>SHW</sub> |                              | 75        |       |       |  |

| SCL "L" Pulse width | t <sub>SLW</sub> |                              | 75        |       |       |  |

| Adress setup time   | t <sub>SAS</sub> |                              | 50        | —     |       |  |

| Address hold time   | t <sub>SAH</sub> |                              | 100       |       | ns    |  |

| Data setup time     | t <sub>SDS</sub> |                              | 50        |       |       |  |

| Data hold time      | t <sub>SDH</sub> |                              | 50        |       |       |  |

| CS setup time       | t <sub>CSS</sub> |                              | 100       | _     |       |  |

| CS hold time        | t <sub>CSH</sub> |                              | 100       | _     |       |  |

Note 1: The input signal rise and fall times are specified as 15ns or less.

Note 2: All timings are specified taking the levels of 20% and 80% of  $V_{DD}$  as the reference.

# **OKI** Semiconductor

# [V<sub>DD</sub> = 3.7 to 4.5 V, Tj = -40 to +85°C]

|                     |                  | Rated value |     |   | Unit |  |

|---------------------|------------------|-------------|-----|---|------|--|

| Parameter           | Symbol           | Condition   | Min |   |      |  |

| Serial clock period | tscyc            |             | 250 | _ |      |  |

| SCL "H" Pulse width | t <sub>SHW</sub> |             | 100 | _ |      |  |

| SCL "L" Pulse width | t <sub>SLW</sub> |             | 100 |   |      |  |

| Address setup time  | t <sub>SAS</sub> |             | 150 | _ |      |  |

| Address hold time   | t <sub>SAH</sub> |             | 150 |   | ns   |  |

| Data setup time     | t <sub>SDS</sub> |             | 100 |   |      |  |

| Data hold time      | t <sub>SDH</sub> |             | 100 | _ |      |  |

| CS setup time       | t <sub>css</sub> |             | 150 |   |      |  |

| CS hold time        | t <sub>CSH</sub> |             | 150 | — |      |  |

Note 1: The input signal rise and fall times are specified as 15ns or less.

Note 2: All timings are specified taking the levels of 20% and 80% of  $V_{DD}$  as the reference.

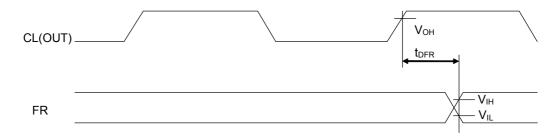

• Display control output timing

| [V <sub>DD</sub> = 4.5 to 5.5 V, T] | j = -40 to +85°C] |

|-------------------------------------|-------------------|

|-------------------------------------|-------------------|

| Parameter     | Symbol           | Condition  | Rated value<br>Min Typ Max |    |    | Unit |  |

|---------------|------------------|------------|----------------------------|----|----|------|--|

| Falameter     | Symbol           | Condition  |                            |    |    | Unit |  |

| FR Delay time | t <sub>DFR</sub> | CL = 50 pF | _                          | 10 | 40 | ns   |  |

| $[V_{DD} = 3]$ | 7 to 4 5 V                     | Tj = -40 to | +85°C1 |

|----------------|--------------------------------|-------------|--------|

| [VDD = 0.      | <i>i</i> to <del>4</del> .0 v, | 1           | .00.01 |

| Parameter     | Symbol           | Condition  | Rated value |     |     | Unit |  |

|---------------|------------------|------------|-------------|-----|-----|------|--|

| Falameter     | Symbol           | Condition  | Min         | Тур | Max | Unit |  |

| FR Delay time | t <sub>DFR</sub> | CL = 50 pF | _           | 20  | 80  | ns   |  |

Note 1: All timings are specified taking the levels of 20% and 80% of  $V_{\text{DD}}$  as the reference.

Note 2: Valid only when the device operates in master mode.

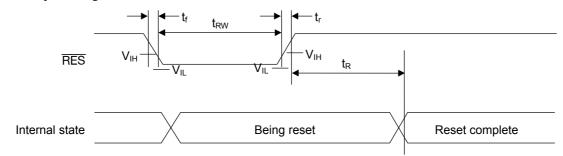

• Reset input timing

$[V_{DD} = 4.5 \text{ to } 5.5 \text{ V}, \text{ Tj} = -40 \text{ to } +85^{\circ}\text{C}]$

| Parameter             | Symbol             | Condition | Rated value |     | Unit |      |  |

|-----------------------|--------------------|-----------|-------------|-----|------|------|--|

| Farameter             | Symbol Condition – |           | Min         | Тур | Max  | Unit |  |

| Reset time            | t <sub>R</sub>     |           | _           | _   | 0.5  |      |  |

| Reset "L" pulse width | t <sub>RW</sub>    |           | 0.5         | —   | _    | μs   |  |

| $[V_{DD} = 3.7 \text{ to } 4.5 \text{ V}, \text{ T}]$ | j = -40 to +85°C] |

|-------------------------------------------------------|-------------------|

|-------------------------------------------------------|-------------------|

| Parameter             | Symbol          | Condition | Rated value |     |     | Unit |  |

|-----------------------|-----------------|-----------|-------------|-----|-----|------|--|

| Farameter             | Symbol          | Condition | Min         | Тур | Max | Unit |  |

| Reset time            | t <sub>R</sub>  |           | _           | _   | 1   |      |  |

| Reset "L" pulse width | t <sub>RW</sub> |           | 1           | _   |     | μs   |  |

Note 1: The input signal rise and fall times  $(t_r, t_f)$  are specified as 15 ns or less. Note 2: All timings are specified taking the levels of 20% and 80% of  $V_{DD}$  as the reference.

# **PIN DESCRIPTION**

| Function         | Pin name      | Number<br>of pins | I/O | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|------------------|---------------|-------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                  | DB0 to<br>DB7 | 8                 | I/O | These are 8-bit bi-directional data bus pins that can be connected to<br>8-bit standard MPU data bus pins. When a serial interface is selected<br>$(P/\overline{S} = "L")$ :<br>DB7: Serial data input pin (SI)<br>DB6: Serial clock input pin (SCL)<br>In this case, DB0 to DB5 will be in the high impedance state. DB0 to<br>DB7 will all be in the high impedance state when the chip select is in<br>the inactive state.<br>Fix the DB0 to DB5 pins at "H" or "L" level.                                                         |

|                  | A0            | 1                 | I   | Normally, the lowest bit of the MPU address bus is connected and<br>used for distinguishing between data and commands.<br>A0 = "H": Indicates that DB0 to DB7 is display data.<br>A1 = "L": Indicates that DB0 to DB7 is control data.                                                                                                                                                                                                                                                                                                |

|                  | RES           | 1                 | I   | Initial setting is made by making $\overline{\text{RES}}$ = "L". The reset operation is made during the active level of the $\overline{\text{RES}}$ signal.                                                                                                                                                                                                                                                                                                                                                                           |

|                  | CS1<br>CS2    | 2                 | I   | These are the chip select signals. The Chip Select of the LSI becomes active when CS1 is "L" and also CS2 is "H" and allows the input/output of data or commands.                                                                                                                                                                                                                                                                                                                                                                     |

| MPU<br>Interface | RD<br>(E)     | 1                 | I   | The active level of this signal is "L" when connected to an 80-series MPU. This pin is connected to the $\overline{\text{RD}}$ signal of the 80-series MPU, and the data bus of the ML9059 goes into the output state when this signal is "L".<br>The active level of this signal is "H" when connected to a 68-series MPU. This pin will be the Enable and clock input pin when connected to a 68-series MPU.<br>When a serial interface is selected ( $\overline{P/S} = \text{``L"}$ ), fix this pin at "H" or "L" level.           |

|                  | ₩R<br>(R/₩)   | 1                 | I   | The active level of this signal is "L" when connected to an 80-series MPU. This pin is connected to the $\overline{WR}$ signal of the 80-series MPU. The data on the data bus is latched into the ML9059 at the rising edge of the $\overline{WR}$ signal.<br>When connected to a 68-series MPU, this pin becomes the input pin for the Read/Write control signal.<br>$R/\overline{W}$ = "H": Read, $R/\overline{W}$ = "L": Write<br>When a serial interface is selected ( $P/\overline{S}$ = "L"), fix this pin at "H" or "L" level. |

|                  | C86           | 1                 | I   | This is the pin for selecting the MPU interface type.<br>C86 = "H": 68-Series MPU interface.<br>C86 = "L": 80-Series MPU interface.                                                                                                                                                                                                                                                                                                                                                                                                   |

# **OKI** Semiconductor

|    | ~ ~ - ~ |

|----|---------|

| ML | ,9059   |

| Function                                  | Pin name | Number<br>of pins | I/O | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

|-------------------------------------------|----------|-------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| MPU                                       | P/S      | 1                 |     | This is the pin for selecting parallel data input or serial data<br>input.<br>$P/\overline{S} = "H"$ : Parallel data input.<br>$P/\overline{S} = "L"$ : Serial data input.<br>The pins of the LSI have the following functions depending on<br>the state of $P/\overline{S}$ input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

| Interface                                 |          |                   |     | P/S Data/command Data Read/Write Serial clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

|                                           |          |                   |     | "H" A0 DB0 to DB7 RD, WR —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

|                                           |          |                   |     | "L" A0 SI (D7) — SCL(DB6)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

|                                           |          |                   |     | During serial data input, it is not possible to read the display data<br>in the RAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

| Oscillator<br>circuit                     | CLS      | 1                 | I   | This is the pin for selecting whether to enable or disable the internal oscillator circuit for the display clock.<br>CLS = "H": The internal oscillator circuit is enabled.<br>CLS = "L": The internal oscillator circuit is disabled (External input).<br>When CLS = "L", the display clock is input at the pin CL.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

| Display<br>timing<br>generator<br>circuit | M/S      | 1                 | Ι   | This is the pin for selecting whether master operation or slave<br>operation is made towards the ML9059. During slave operation,<br>the synchronization with the LCD display system is achieved by<br>inputting the timing signals necessary for LCD display. $M/\overline{S} = "H": Master operationM/\overline{S} = "L": Slave operationM/\overline{S} = "L": Slave operationThe functions of the different circuits and pins will be as followsdepending on the states of M/\overline{S} and CLS signals.\overline{M/\overline{S}}\overline{M/\overline{S}}\overline{M/\overline{S}}\overline{CLS}\overline{Oscillator}\overline{Power}clremains remains remaining the states of M/\overline{S} and CLS signals.\overline{M/\overline{S}}\overline{U'}\overline{U'}\overline{U'}\overline{U'}\overline{U'}\overline{U'}\overline{U'}\overline{U'}\overline{U'}\overline{U'}\overline{U'}\overline{U'}\overline{U'}\overline{U'}\overline{U'}\overline{U'}\overline{U'}\overline{U'}\overline{U'}\overline{U'}\overline{U'}\overline{U'}\overline{U'}\overline{U'}\overline{U'}\overline{U'}\overline{U'}\overline{U'}\overline{U'}\overline{U'}\overline{U'}\overline{U'}\overline{U'}\overline{U'}\overline{U'}\overline{U'}\overline{U'}\overline{U'}\overline{U'}\overline{U'}\overline{U'}\overline{U'}\overline{U'}\overline{U'}\overline{U'}\overline{U'}\overline{U'}<$ |  |  |  |  |  |

| Function                       | Pin name        | Number<br>of pins | I/O | Description                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

|--------------------------------|-----------------|-------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

|                                |                 |                   |     | This is the clock input/output pin.<br>The function of this pin will be as follows depending on the states of M/S and CLS signals.                                                                                                                                                                                                                                                                           |  |  |  |  |  |

|                                |                 |                   |     | M/S CLS CL                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

|                                | CL              | 1                 | I/O | "H" Output<br>"L" Input                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

|                                |                 |                   |     | "I" Input                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

|                                |                 |                   |     | "L" Input                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

| Display                        |                 |                   |     | When the ML9059 is used in the master/slave mode, the corresponding CL pin has to be connected.                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

| timing<br>generator<br>circuit | FR              | 1                 | I/O | This is the input/output pin for LCD display frame reversal signal.<br>$M/\overline{S} = "H"$ : Output<br>$M/\overline{S} = "L"$ : Input<br>When the ML9059 is used in the master/slave mode, the<br>corresponding FR pin has to be connected.                                                                                                                                                               |  |  |  |  |  |

|                                | DOF             | 1                 | I/O | This is the blanking control pin for the LCD display.<br>$M/\overline{S} = "H"$ : Output<br>$M/\overline{S} = "L"$ : Input<br>When the ML9059 is used in the master/slave mode, the<br>corresponding $\overline{DOF}$ pin has to be connected.                                                                                                                                                               |  |  |  |  |  |

|                                | FRS             | 1                 | 0   | This is the output pin for static drive.<br>This pin is used in combination with the FR pin.                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

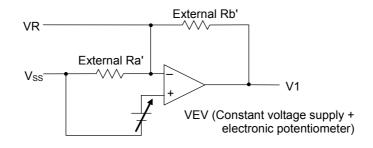

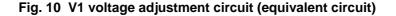

| Power                          | IRS             | 1                 | I   | This is the pin for selecting the resistor for adjusting the voltage V1.<br>IRS = "H": The internal resistor is used.<br>IRS = "L": The internal resistor is not used. The voltage V1 is<br>adjusted using the external potential divider resistors connected to<br>the pins VR. This pin is effective only in the master operation. This<br>pin is tied to the "H" or the "L" level during slave operation. |  |  |  |  |  |

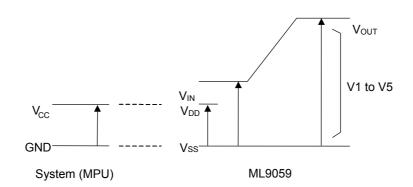

| circuit                        | V <sub>DD</sub> | 12                | _   | These pins are tied to the MPU power supply pin $V_{\text{CC}}$ .                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

|                                | V <sub>SS</sub> | 12                |     | These are the 0 V pins connected to the system ground (GND).                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

|                                | V <sub>IN</sub> | 5                 | _   | These are the reference power supply pins of the voltage multiplier circuit for driving the LCD.                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

| Function          | Pin name                   | Number<br>of pins | I/O                  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |

|-------------------|----------------------------|-------------------|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

|                   | V <sub>RS</sub>            | 2                 | _                    | These are the test pins for the LCD power supply voltage adjustment circuit. Leave these pins open.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |  |

|                   | Vout                       | 2                 | I/O                  | These are the output pins during voltage multiplication. Connect a capacitor between these pins and $V_{\mbox{\scriptsize SS}}.$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |

|                   | V1<br>V2<br>V3<br>V4<br>V5 | 10                | I/O                  | These are the multiple level power supply pins for the LCD powersupply. The voltages specified for the LCD cells are applied tothese pins after resistor network voltage division or afterimpedance transformation using operational amplifiers. Thevoltages are specified taking V <sub>SS</sub> as the reference, and thefollowing relationship should be maintained among them.V1 $\geq$ V3 $\geq$ V4 $\geq$ V5 $\geq$ V <sub>SS</sub> Master operation: When the power supply is ON, the followingvoltages are applied to V2 to V5 from the built-in power supplycircuit. The selection of voltages is determined by the LCD biasset command.ML9059V27/8 $\times$ V15/6 $\times$ V1V27/8 $\times$ V15/6 $\times$ V1V27/8 $\times$ V12/6 $\times$ V1 |  |  |  |  |  |  |

| Power             |                            |                   | V5 1/8 × V1 1/6 × V1 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |

| supply<br>circuit | VR                         | 2                 | I                    | Voltage adjustment pins. Voltages between V1 and $V_{SS}$ are applied using a resistance voltage divider.<br>These pins are effective only when the internal resistors for voltage V1 adjustment are not used (IRS = "L").<br>Do not use these pins when the internal resistors for voltage V1 adjustment are used (IRS = "H").                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |

|                   | VS1–                       | 3                 | 0                    | These are the pins for connecting the negative side of the capacitors for voltage multiplication.<br>Connect capacitors between these pins and VC3+, VC5+.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |

|                   | VS2–                       | 3                 | 0                    | These are the pins for connecting the negative side of the capacitors for voltage multiplication.<br>Connect capacitors between these pins and VC4+, VC6+.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |

|                   | VC3+                       | 3                 | 0                    | These are the input pins for voltage multiplication. Apply the voltage equal to $V_{IN}$ to the pins or leave them open, depending on voltage multiplication values.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

|                   | VC4+                       | 3                 | 0                    | These are the pins for connecting the positive side of the capacitors for voltage multiplication.<br>Connect capacitors between VS2– and these pins.<br>For 3-time voltage multiplication, the pins are configured as inputs for voltage multiplication.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |

# **OKI** Semiconductor

| Function                   | Pin name          | Number<br>of pins | I/O | Description                                                                                          |                                                                                      |                                                                                        |                                                         |  |  |  |

|----------------------------|-------------------|-------------------|-----|------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|---------------------------------------------------------|--|--|--|

| Power<br>supply<br>circuit | VC5+              | 3                 | о   | capacitors for v<br>Connect capac                                                                    | oltage multiplie<br>itors between<br>ge multiplicatio                                | ting the positive sic<br>cation.<br>/S1– and these pin<br>on, the pins are con         | S.                                                      |  |  |  |

| Circuit                    | VC6+              | 3                 | ο   | capacitors for v                                                                                     | oltage multipli                                                                      | ting the positive sic<br>cation.<br>/S2– and these pin                                 |                                                         |  |  |  |

|                            |                   |                   |     |                                                                                                      | Is among V1, V                                                                       | drive outputs.<br>/3, V4, and V <sub>SS</sub> is s<br>of the display RAM               |                                                         |  |  |  |

|                            |                   |                   |     | RAM Data                                                                                             | FR                                                                                   |                                                                                        | t voltage                                               |  |  |  |

| SEG0 to                    |                   |                   |     |                                                                                                      |                                                                                      | Reverse display                                                                        |                                                         |  |  |  |

|                            | SEG0 10<br>SEG131 | 132               | 0   | Н                                                                                                    | Н                                                                                    | V1                                                                                     | V3                                                      |  |  |  |

|                            |                   |                   |     | H                                                                                                    | L                                                                                    | V <sub>SS</sub>                                                                        | V4                                                      |  |  |  |

|                            |                   |                   |     | L                                                                                                    | H                                                                                    | V3                                                                                     | V1                                                      |  |  |  |

|                            |                   |                   |     | L<br>Power save                                                                                      | L                                                                                    | V4                                                                                     | V <sub>SS</sub>                                         |  |  |  |

|                            |                   |                   |     |                                                                                                      | Is among V1, V                                                                       | /2, V5, and $V_{SS}$ is s<br>of the scan data ar                                       |                                                         |  |  |  |

|                            |                   |                   |     | Scan data                                                                                            | FR                                                                                   | Output voltage                                                                         |                                                         |  |  |  |

|                            |                   |                   |     | Н                                                                                                    | H                                                                                    | V <sub>SS</sub>                                                                        |                                                         |  |  |  |

|                            | COM0 to           | 40                | 0   | Н                                                                                                    | L                                                                                    | V1                                                                                     |                                                         |  |  |  |

|                            | COM47             | 48                | 0   | L                                                                                                    | H                                                                                    | V2                                                                                     |                                                         |  |  |  |

|                            |                   |                   |     |                                                                                                      | L                                                                                    | V5                                                                                     |                                                         |  |  |  |

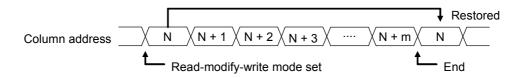

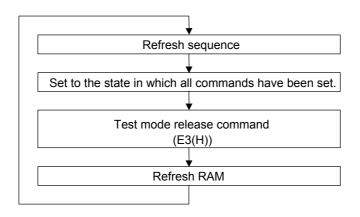

|                            |                   |                   |     |                                                                                                      | Power save                                                                           | _                                                                                      | -                                                       |  |  |  |