# **OKI Semiconductor**

Oki, Network Solutions for a Global Society

**PEDL9055A-02-01** Issue Date: Jul. 26, 2002

# ML9055A-02

# **Preliminary**

LCD Controller/Driver

#### GENERAL DESCRIPTION

The ML9055A-02 is an LSI providing the bit map display on a dot matrix graphic LCD panel . With one chip, it is possible to construct a graphic display system with a maximum of  $128 \times 128$  dots. Since all the functions necessary for driving the bit map type LCD panel are incorporated into a single chip, the ML9055A-02 allows to implement a dot matrix graphic LCD display system of bit map type with only a few chips in combination with an 8-bit microcomputer.

Using the CMOS process and a built-in RAM, the ML9055A-02 is highly suitable for displays in battery-operated portable equipment.

#### **FEATURES**

- Liquid Crystal Display (LCD) controller and driver

- Maximum display size: 128 columns × 128 rows

- Logic voltage: 1.8 to 3.0 V

- LCD drive voltage: 4.0 to 16.0 V

- Serial interface (3-line or 4-line, write only) and parallel interface

- · Built-in voltage multiplier and oscillator circuit for display timing control

- LCD drive bias: 1/5 to 1/12Duty ratio: 1/16 to 1/128

- Voltage regulator temperature coefficient: -0.125%/°C

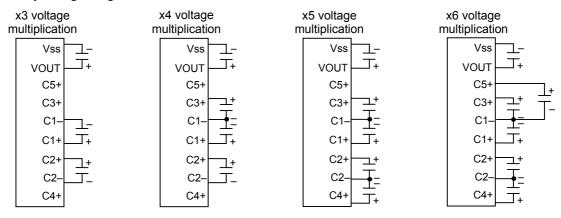

- Voltage multiplier: x3, x4, x5, x6

- Contrast adjustjment: 64 levels available

- 4-level gray scale

- Partial display function

- Scroll function

- Frame frequency: 180 Hz

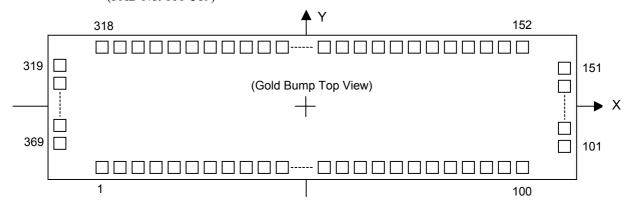

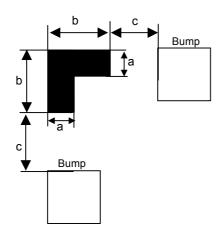

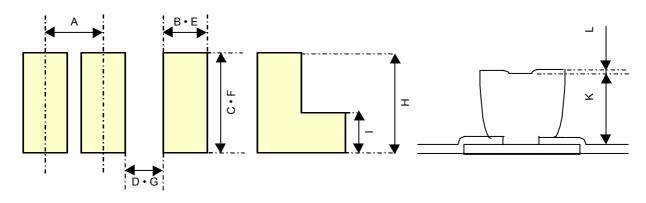

- Package: Gold bump chip, TCP

ML9055A-02DVWA (Gold bump chip name) ML9055A-02DVVAZ01L (General TCP name)

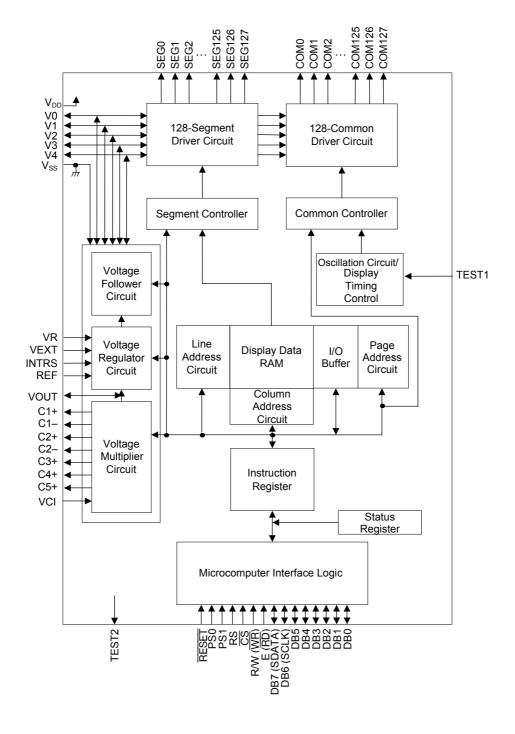

#### **BLOCK DIAGRAM**

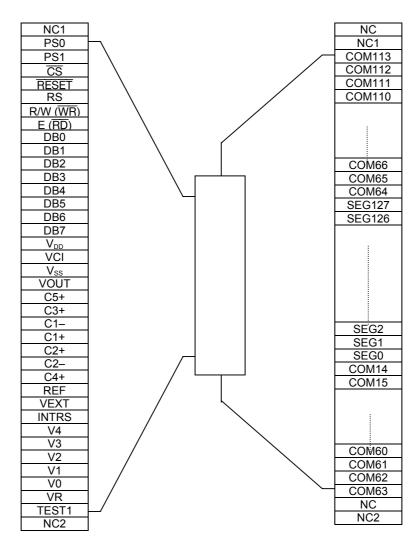

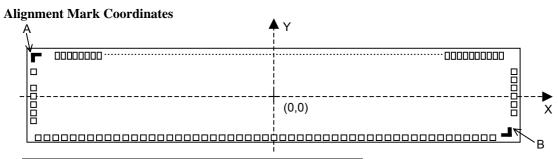

#### PIN CONFIGURATION (STANDARD TCP: BRONZE-FOIL FACE UP)

Note 1: This drawing is not a true external view of TCP, but it primarily shows the TCP pin layout.

Note 2: The TCP shown above is a standard TCP and does not have COM0 to COM13 pins and COM114 to COM127 pins. Also there is no TEST2 pin on the TCP.

(In the TCP, 128 lines from SEG0 to SEG127 and 100 lines from COM14 to COM113 are derived as the output pins.)

The external shape and the number of output pins of TCP can be customized as needed.

Note 3: Do not connect the NC pins to outside or any other pins. NC stands for "No Connection". The NC pins are not connected to the chip. All NC pins are independent.

NC1 remains connected to COM112 before dicing. Although the input side NC1 remains connected with the output side NC1 by dicing, the connection with COM112 is lost.

Similarly, NC2 remains connected to COM63 before dicing. Although the input side NC2 remains connected with the output side NC2 by dicing, the connection with COM63 is lost.

# PIN DESCRIPTIONS

| Function          | Symbol   | Туре   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-------------------|----------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -                 | $V_{DD}$ | Supply | Power supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                   | $V_{SS}$ | Supply | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                   | V0       |        | LCD drive power supply voltage pin V0, and LCD drive bias voltage pins V1 to V4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Power Supply      | V1       |        | When applying the LCD drive power supply voltage and each LCD drive bias voltage from outside, notice to hold the following relationship:                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| i ower cuppiy     | V2       | I/O    | $V_{SS} < V4 < V3 < V2 < V1 < V0$ The LCD drive bias voltages are generated when using the built in voltage follower.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                   | V3       |        | built-in voltage follower.  For the value of each generated bias voltage, refer to the "Voltage Follower Circuit" section in this document.                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| _                 | V4       |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                   | C1-      | 0      | Connection pins of capacitors for multiplied voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                   | C1+      | 0      | Connect capacitors for the voltage multiplier to these pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                   | C2-      | 0      | (Connect pins with + sign to positive polarity of respective                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                   | C2+      | 0      | capacitors and pins with – sign to negative polarity of respective                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                   | C3+      | 0      | capacitors.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                   | C4+      | 0      | The connections of capacitors for multiplying voltage differ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                   | C5+      | 0      | depending upon the voltage multiplication.  The connections of the capacitors for multiplying voltage are described in the "Voltage Multiplier" section.                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                   | VOUT     | I/O    | Voltage multiplier input/output pins When using an internal voltage multiplier, the following voltage is output from the VOUT pin: VOUT = VCI x Voltage multiplication When not using the internal voltage multiplier, input the external power supply voltage from this VOUT pin. About the pin processing in the case of an external input, refer to the "LCD Drive Power Supply Circuit" section.                                                                                                                                                                                                                  |

| LCD Driver Supply | VCI      | I      | Multiplied voltage input pin of internal voltage multiplier When using an external power supply, tie this pin to V <sub>SS</sub> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 202 Бичег оцрргу  | VR       | I      | V0 voltage adjustment pin (Adjusts V0 using external resistors.) When INTRS pin = "L", the V0 voltage is adjusted by connecting external resistors to this pin. The method of connecting external resistors is described in the "LCD Drive Power Supply Circuit" section. When INTRS pin = "H", keep this VR pin open. Note: When INTRS pin is "H", the internal resistors are selected for adjusting V0 and a very high internal resistor gets connected to VR pin. Therefore this ML9055A can be vulnerable to external noise. In designing the circuit board, pay proper attention to the external noise and leak. |

|                   | REF      | I      | Internal/external reference voltage select pin. (L: External, H: Internal)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                   | VEXT     | 1      | External reference voltage ( $V_{\text{REF}}$ ) input pin. (Valid only when REF= L.) When using the internal reference power supply, keep this pin open.                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                   | INTRS    | I      | V0 adjustment resistor select pin (L: External, H: Internal)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Function                   | Symbol            | Туре | Description                                                                                                                                                                |  |  |  |  |  |

|----------------------------|-------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

|                            | RESET             | Ī    | Reset input pin (active "L")                                                                                                                                               |  |  |  |  |  |

|                            |                   |      | Parallel/serial data setting (H = Parallel, L = Serial)                                                                                                                    |  |  |  |  |  |

|                            |                   |      | PS0 PS1 Interface                                                                                                                                                          |  |  |  |  |  |

|                            |                   |      | L L 3-line serial interface                                                                                                                                                |  |  |  |  |  |

|                            | PS0               | I    | L H 4-line serial interface                                                                                                                                                |  |  |  |  |  |

|                            | PS1               |      | H L 8080 parallel interface                                                                                                                                                |  |  |  |  |  |

|                            |                   |      | H H 6800 parallel interface                                                                                                                                                |  |  |  |  |  |

|                            |                   |      | Note: When using the serial interface, leave D0-D5 open and connect E $(\overline{RD})$ and R/W $(\overline{WR})$ to $V_{DD}$ or $V_{SS}$ .                                |  |  |  |  |  |

|                            | <u>CS</u>         | I    | Chip select input pin (active "L")                                                                                                                                         |  |  |  |  |  |

| Microcomputer<br>Interface | RS                | I    | Register select input pin Distinguishes between display data (H) and command data (L). Connect this pin to V <sub>DD</sub> or V <sub>SS</sub> for 3-line serial interface. |  |  |  |  |  |

|                            | R/W (WR)          | I    | When connected to a 68-series MPU: Read/write execute control pin (H = read, L = write) When connected to an 80-series MPU: Write execute control pin (L = write)          |  |  |  |  |  |

|                            | E (RD)            | I    | When connected to a 68-series MPU: E clock input pin When connected to an 80-series MPU: Read execute control pin (L = read)                                               |  |  |  |  |  |

|                            | DB0 to<br>DB7     | I/O  | When parallel interface is selected, 8-bit data bus pin When serial interface is selected, DB0 to DB5: Open DB6(SCLK): Serial clock input DB7(SDATA): Serial data input    |  |  |  |  |  |

| LCD Driver                 | SEG0 to<br>SEG127 | 0    | LCD segment driver outputs                                                                                                                                                 |  |  |  |  |  |

| LOD DIIVei                 | COM0 to<br>COM127 | 0    | LCD common driver outputs                                                                                                                                                  |  |  |  |  |  |

| Test                       | TEST1             | I    | Test pin of this LSI. Connect this pin to V <sub>DD</sub> .                                                                                                                |  |  |  |  |  |

| 1001                       | TEST2             | 0    | Test pin of this LSI. Leave this pin open                                                                                                                                  |  |  |  |  |  |

#### ABSOLUTE MAXIMUM RATINGS

$(V_{SS} = 0 V)$

| Parameter                            | Symbol    | Condition | Rating                       | Unit |

|--------------------------------------|-----------|-----------|------------------------------|------|

| Power Supply Voltage                 | $V_{DD}$  | Tj = 25°C | -0.3 to +4.0                 | V    |

| Voltage Multiplier Input<br>Voltage  | VCI       | Tj = 25°C | -0.3 to +4.0 (*1)            | ٧    |

| Voltage Multiplier Output<br>Voltage | VOUT      | Tj = 25°C | -0.3 to +20.0                | ٧    |

| LCD Drive Voltage                    | V0        | Tj = 25°C | -0.3 to +20.0 (*2)           | V    |

| LCD Drive Bias Voltage               | Vm (*3)   | Tj = 25°C | -0.3 to V0 +0.3 (*4)         | V    |

| Logic Input Voltage                  | $V_{I}$   | Tj = 25°C | -0.3 to V <sub>DD</sub> +0.3 | V    |

| Storage Temperature Range            | $T_{stg}$ | Chip      | -55 to +150                  | °C   |

- \*1. Notice that voltage multiplier output voltage VOUT should not exceed 20 V.

\*2. V0 should not exceed VOUT.

\*3. Vm indicates V1, V2, V3 and V4.

\*4. Notice that Vm should not exceed 20 V.

# RECOMMENDED OPERATING CONDITIONS

$(V_{SS} = 0 V)$

| Parameter                            | Symbol   | Condition | Range                       | Unit |

|--------------------------------------|----------|-----------|-----------------------------|------|

| Power Supply Voltage                 | $V_{DD}$ | _         | 1.8 to 3.0                  | V    |

| Voltage Multiplier Input Voltage     | VCI      | _         | V <sub>DD</sub> to 3.0 (*1) | V    |

| Voltage Multiplier Output<br>Voltage | VOUT     | ı         | 5.4 to 16.0                 | V    |

| LCD Driver voltage                   | V0       | _         | 4.0 to VOUT-1               | V    |

| LCD Driver Bias Voltage 1            | V1       | <u> </u>  | 3.2 to 14.7 (*2)            | V    |

| LCD Driver Bias Voltage 2            | V2       | <u> </u>  | 2.4 to 13.4 (*2)            | V    |

| LCD Driver Bias Voltage 3            | V3       | _         | 1.6 to 2.7 (*2)             | V    |

| LCD Driver Bias Voltage 4            | V4       | _         | 0.8 to 1.4 (*2)             | V    |

| External Reference<br>Voltage        | VEXT     | -         | 1.8 to V <sub>DD</sub>      | V    |

| Operating Temperature                | $T_jop$  | Chip      | -40 to +85                  | °C   |

<sup>\*1.</sup> Notice that the voltage multiplier output voltage VOUT is 16 V or below.\*2. Notice that VOUT>V0>V1>V2>V3>V4.

Do not expose the ML9055A to light when in use.

# **ELECTRICAL CHARACTERISTICS**

# **DC** Characteristics

VOUT-V0 Voltage

$V_{\text{OT0}} \\$

|                                 |                    |                                    | $(V_{DD}$           | = 1.8 to | 3.0 V, V                 | / <sub>SS</sub> = 0 \ | $/$ , Tj = $-40$ to $+85^{\circ}$ C)                                                                            |

|---------------------------------|--------------------|------------------------------------|---------------------|----------|--------------------------|-----------------------|-----------------------------------------------------------------------------------------------------------------|

| Parameter                       | Symbol             | Condition                          | Min.                | Тур.     | Max.                     | Unit                  | Applied pins                                                                                                    |

| Liber leavet Veltere            | .,                 |                                    | ×8.0                |          | .,                       | .,                    | RESET, PS0,                                                                                                     |

| High Input Voltage              | V <sub>IH</sub>    | _                                  | $V_{DD}$            |          | $V_{DD}$                 | V                     | PS1, <del>CS</del> , RS,                                                                                        |

| Low Input Voltage               | V <sub>IL</sub>    | _                                  | 0.0                 | _        | 0.2 ×<br>V <sub>DD</sub> | V                     | R/W (WR), E (RD), DB7 (SDATA), DB6 (SCLK), DB5-DB0, INTRS, REF                                                  |

| High Output Voltage             | V <sub>OH</sub>    | I <sub>OH</sub> = -0.5 mA          | $0.8 \times V_{DD}$ | _        | V <sub>DD</sub>          | ٧                     | DB7 (SDATA),                                                                                                    |

| Low Output Voltage              | V <sub>OL</sub>    | I <sub>OL</sub> = 0.5 mA           | 0.0                 | _        | 0.2 × V <sub>DD</sub>    | V                     | DB6 (SCLK),<br>DB5-DB0                                                                                          |

| Input Current                   | I <sub>IL</sub>    | $V_{IN} = V_{DD}$ or $V_{SS}$      | -1.0                |          | +1.0                     | μА                    | RESET, PS0,<br>PS1, CS, RS,<br>R/W (WR),<br>E (RD),<br>DB7 (SDATA),<br>DB6 (SCLK),<br>DB5-DB0,<br>INTRS,<br>REF |

| LCD Driver On<br>Resistance     | R <sub>ON</sub>    | Tj = 25°C,<br>1/8 bias<br>V0 = 8 V |                     | 2.5      | 5                        | kΩ                    | SEG0-SEG127,<br>COM0-COM127                                                                                     |

| Internal resistance ratio error | R <sub>ratio</sub> | _                                  | _                   | _        | 3                        | %                     | V0                                                                                                              |

|                                 |                    | V0 load current = 300 μA           |                     |          |                          |                       |                                                                                                                 |

VOUT = 8 V(applied externally)

LCD output, no load

VOUT, V0

| Parameter                              | Symbol             | Condition                                                                                                                                      | Min. | Тур. | Max.     | Unit | Applied pins               |

|----------------------------------------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------|------|------|----------|------|----------------------------|

|                                        | I <sub>DD11</sub>  | Tj= 25°C,  V <sub>DD</sub> = VCI = 2.75 V  ×5 voltage multiplier  1/100 duty  Frame frequency: 180 Hz  Display: Off (*1)                       | _    | 150  | 230      | μΑ   |                            |

|                                        | I <sub>DD12</sub>  | Tj= 25°C,  V <sub>DD</sub> = VCI = 2.75 V  ×5 voltage multiplier  1/128 duty  Frame frequency: 220 Hz  Display: Off (*1)                       | _    | 185  | 285      | μΑ   |                            |

| Operating Current<br>Consumption       | I <sub>DD21</sub>  | Tj= 25°C, V <sub>DD</sub> = VCI = 2.75 V ×5 voltage multiplier Display: On 1/100 duty Frame frequency: 180 Hz (Full checker board pattern (*1) |      | 300  | 430      | μΑ   | V <sub>DD</sub> , VCI (*2) |

|                                        | I <sub>DD22</sub>  | Tj= 25°C, V <sub>DD</sub> = VCI = 2.75 V ×5 voltage multiplier Display: On 1/128 duty Frame frequency: 220 Hz (Full checker board pattern (*1) | _    | 370  | 530      | μΑ   |                            |

| Current Consumption in Power Save Mode | I <sub>SLEEP</sub> | Power save mode<br>Tj = 25°C, $V_{DD}$ = 3.0 V                                                                                                 | _    | _    | 2        | μΑ   |                            |

| Voltage Multiplier<br>Efficiency       | E <sub>VC</sub>    | ×3/×4/×5/×6 Using internal power supply No load                                                                                                | 95   | 99   | _        | %    | VOUT                       |

| Reference Voltage                      | $V_{REF}$          | Tj = -20°C<br>Tj = 25°C                                                                                                                        | 2.04 | 2.22 | <u> </u> | V    | VEXT (*3)                  |

|                                        |                    | Tj = 70°C                                                                                                                                      | _    | 1.98 |          | V    |                            |

<sup>(\*1)</sup> No CPU access state.

No LCD panel load.

Other conditions: 1/12 bias; contrast = 60; internal resistance ratio setting = 5.8; 3-FRC; 9-level PWM; frame inversion

- (\*2) The current consumption is a sum of  $V_{DD}$  current and VCI current.

- (\*3) Vref voltage is measurable in the test mode, but cannot be measured when a customer is using the ML9055A in normal circumstances.

#### **AC Characteristics**

Serial Interface Timing

$(V_{DD} = 1.8 \text{ V}, \text{ Tj} = -40 \text{ to } +85^{\circ}\text{C})$

$(V_{DD} = 2.7 \text{ V}, \text{ Tj} = -40 \text{ to } +85^{\circ}\text{C})$

15

15

ns

ns

ns

ns

| Parameter                      | Symbol           | Min. | Typ.     | Max. | Unit |

|--------------------------------|------------------|------|----------|------|------|

| Serial Clock Frequency         | f <sub>CLK</sub> | _    | _        | 9    | MHz  |

| Serial Clock Cycle Time        | t <sub>CLK</sub> | 111  | _        | _    | ns   |

| Serial Clock "H" Pulse Width   | t <sub>WHS</sub> | 50   | _        | _    | ns   |

| Serial Clock "L" Pulse Width   | t <sub>WLS</sub> | 50   | <u> </u> | _    | ns   |

| Data Setup Time                | t <sub>DS</sub>  | 50   | _        | _    | ns   |

| Data Hold Time                 | t <sub>DH</sub>  | 50   | _        | _    | ns   |

| Chip Select Setup Time         | t <sub>CSS</sub> | 60   |          | _    | ns   |

| Chip Select Hold Time          | t <sub>CSH</sub> | 50   | _        | _    | ns   |

| Chip Select "H" Pulse Width    | t <sub>СН</sub>  | 50   | _        | _    | ns   |

| Register Select Setup Time(*1) | t <sub>RSS</sub> | 60   | _        | _    | ns   |

| Register Select Hold Time(*1)  | t <sub>RSH</sub> | 60   | _        | _    | ns   |

| Input Signal Rise Time (*2)    | tr               | _    | _        | 15   | ns   |

| Input Signal Fall Time (*2)    | tf               | _    | _        | 15   | ns   |

(Note) (\*1) Not applied to 3-line serial interface.

(\*2) Applied to all input pins.

Parameter Symbol Min. Max. Unit Тур. Serial Clock Frequency  $f_{\mathsf{CLK}}$ 17 MHz Serial Clock Cycle Time 58.8  $t_{\text{CLK}}$ ns Serial Clock "H" Pulse Width  $t_{\text{WHS}} \\$ 25 ns Serial Clock "L" Pulse Width 25  $t_{\text{WLS}}$ ns Data Setup Time  $t_{\text{DS}}$ 25 ns Data Hold Time 25  $t_{\mathsf{DH}}$ ns Chip Select Setup Time 30  $t_{\text{CSS}}$ ns Chip Select Hold Time 25  $t_{CSH}$ ns Chip Select "H" Pulse Width  $t_{CH}$ 30 ns

$t_{RSS}$

$t_{\mathsf{RSH}}$

tr

tf

30

30

\_

Register Select Setup Time(\*1)

Register Select Hold Time(\*1)

Input Signal Rise Time (\*2)

Input Signal Fall Time (\*2)

<sup>(</sup>Note) (\*1) Not applied to 3-line serial interface.

<sup>(\*2)</sup> Applied to all input pins.

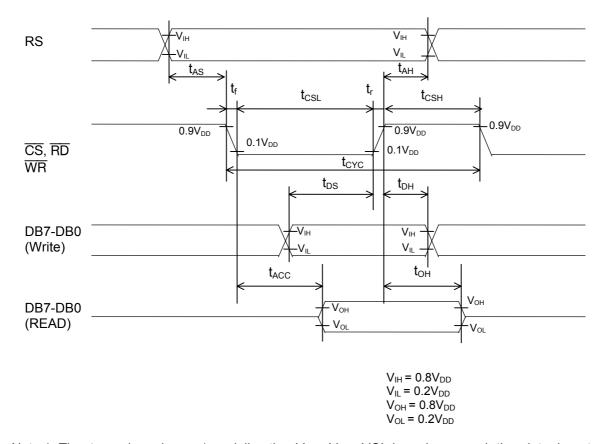

# Parallel Interface Timing (68-series MPU)

$(V_{DD} = 1.8 \text{ V}, \text{ Tj} = -40 \text{ to } +85^{\circ}\text{C})$

|                              |                  |                        |      | ( 🗸 🖰 🖰 – | 1.0 v, 1j <del>4</del> | 0 10 100 0) |

|------------------------------|------------------|------------------------|------|-----------|------------------------|-------------|

| Parameter                    | Symbol           | Condition              | Min. | Тур.      | Max.                   | Unit        |

| Address Setup Time           | t <sub>AS</sub>  | _                      | 0    | _         | _                      | ns          |

| Address Hold Time            | t <sub>AH</sub>  | _                      | 0    | _         | _                      | ns          |

| CS "L" Pulse Width for Write | t <sub>CSL</sub> | _                      | 60   | _         | _                      | ns          |

| CS "H" Pulse Width for Write | t <sub>CSH</sub> | _                      | 60   | _         | _                      | ns          |

| CS "L" Pulse Width for Read  | t <sub>CSL</sub> | _                      | 100  | _         | _                      | ns          |

| CS "H" Pulse Width for Read  | t <sub>CSH</sub> | _                      | 100  | _         | _                      | ns          |

| E "H" Pulse Width for Write  | t <sub>EH</sub>  | _                      | 60   | _         | _                      | ns          |

| E "L" Pulse Width for Write  | t <sub>EL</sub>  | _                      | 60   | _         | _                      | ns          |

| E "H" Pulse Width for Read   | t <sub>EH</sub>  | _                      | 100  | _         | _                      | ns          |

| E "L" Pulse Width for Read   | t <sub>EL</sub>  | _                      | 100  | _         | _                      | ns          |

| Data Setup Time              | t <sub>DS</sub>  | _                      | 40   | _         |                        | ns          |

| Data Hold Time during Write  | t <sub>DH</sub>  | _                      | 10   | _         | _                      | ns          |

| Data Access Time             | t <sub>ACC</sub> | $C_L = 100 \text{ pF}$ |      | _         | 90                     | ns          |

| Data Hold Time during Read   | t <sub>OH</sub>  | _                      | 10   | _         | 90                     | ns          |

| System Write Cycle Time      | t <sub>CYC</sub> | _                      | 150  | _         | _                      | ns          |

| System Read Cycle Time       | t <sub>CYC</sub> | _                      | 330  | _         | _                      | ns          |

| Input Signal Rise Time (*1)  | tr               | _                      | _    | _         | 15                     | ns          |

| Input Signal Fall Time (*1)  | tf               |                        | _    | _         | 15                     | ns          |

# (Note) (\*1) Applied to all input pins.

$(V_{DD} = 2.7 \text{ V}, \text{ Tj} = -40 \text{ to } +85^{\circ}\text{C})$

|                              |                  |                        |      | ( <b>v</b> DD – | Z.7 V, 1j | 10 to 103 C) |

|------------------------------|------------------|------------------------|------|-----------------|-----------|--------------|

| Parameter                    | Symbol           | Condition              | Min. | Тур.            | Max.      | Unit         |

| Address Setup Time           | t <sub>AS</sub>  | _                      | 0    | _               | _         | ns           |

| Address Hold Time            | t <sub>AH</sub>  | _                      | 0    | _               | _         | ns           |

| CS "L" Pulse Width for Write | t <sub>CSL</sub> | _                      | 40   | _               | _         | ns           |

| CS "H" Pulse Width for Write | t <sub>CSH</sub> | _                      | 40   | _               | _         | ns           |

| CS "L" Pulse Width for Read  | t <sub>CSL</sub> | _                      | 60   | _               | _         | ns           |

| CS "H" Pulse Width for Read  | t <sub>CSH</sub> | _                      | 60   | _               | _         | ns           |

| E "H" Pulse Width for Write  | t <sub>EH</sub>  | _                      | 40   | _               | _         | ns           |

| E "L" Pulse Width for Write  | t <sub>EL</sub>  | _                      | 40   | _               | _         | ns           |

| E "H" Pulse Width for Read   | t <sub>EH</sub>  | _                      | 60   | _               | _         | ns           |

| E "L" Pulse Width for Read   | t <sub>EL</sub>  | _                      | 60   | _               | _         | ns           |

| Data Setup Time              | t <sub>DS</sub>  | _                      | 30   | _               | _         | ns           |

| Data Hold Time during Write  | t <sub>DH</sub>  | _                      | 5    | _               | _         | ns           |

| Data Access Time             | t <sub>ACC</sub> | $C_L = 100 \text{ pF}$ |      | _               | 50        | ns           |

| Data Hold Time during Read   | t <sub>OH</sub>  | _                      | 10   | _               | 50        | ns           |

| System Write Cycle Time      | t <sub>CYC</sub> | _                      | 150  |                 |           | ns           |

| System Read Cycle Time       | t <sub>CYC</sub> | _                      | 166  | _               | _         | ns           |

| Input Signal Rise Time (*1)  | tr               | _                      |      | _               | 15        | ns           |

| Input Signal Fall Time (*1)  | tf               | _                      | _    | _               | 15        | ns           |

(Note) (\*1) Applied to all input pins.

# Parallel Interface Timing (80-series MPU)

$(V_{DD} = 1.8 \text{ V}, \text{ Tj} = -40 \text{ to } +85^{\circ}\text{C})$

|                                  |                  |                        |      | (*00 | , . , | /    |

|----------------------------------|------------------|------------------------|------|------|-------|------|

| Parameter                        | Symbol           | Condition              | Min. | Тур. | Max.  | Unit |

| Address Setup Time               | t <sub>AS</sub>  | _                      | 0    | _    | _     | ns   |

| Address Hold Time                | t <sub>AH</sub>  |                        | 0    | _    | _     | ns   |

| CS, WR "L" Pulse Width for Write | t <sub>CSL</sub> | _                      | 60   | _    | _     | ns   |

| CS, WR "H" Pulse Width for Write | t <sub>CSH</sub> |                        | 60   | _    | _     | ns   |

| CS, RD "L" Pulse Width for Read  | t <sub>CSL</sub> |                        | 100  | _    | _     | ns   |

| CS, RD "H" Pulse Width for Read  | t <sub>CSH</sub> |                        | 100  | _    | _     | ns   |

| Data Setup Time                  | t <sub>DS</sub>  |                        | 40   | _    | _     | ns   |

| Data Hold Time during Write      | t <sub>DH</sub>  |                        | 10   | _    | _     | ns   |

| Data Access Time                 | t <sub>ACC</sub> | $C_L = 100 \text{ pF}$ |      | _    | 90    | ns   |

| Data Hold Time during Read       | t <sub>OH</sub>  |                        | 10   | _    | 90    | ns   |

| System Write Cycle Time          | t <sub>CYC</sub> |                        | 150  | _    | _     | ns   |

| System Read Cycle Time           | t <sub>CYC</sub> |                        | 330  | _    | _     | ns   |

| Input Signal Rise Time (*1)      | tr               | _                      |      | _    | 15    | ns   |

| Input Signal Fall Time (*1)      | tf               | _                      | _    | _    | 15    | ns   |

# (Note) (\*1) Applied to all input pins.

$(V_{DD} = 2.7 \text{ V}. \text{ Ti} = -40 \text{ to } +85^{\circ}\text{C})$

|                                  |                  |                |      | (VDD - Z.1 | 7 V, IJ <del>4</del> 0 | 10 100 0 |

|----------------------------------|------------------|----------------|------|------------|------------------------|----------|

| Parameter                        | Symbol           | Condition      | Min. | Тур.       | Max.                   | Unit     |

| Address Setup Time               | t <sub>AS</sub>  | _              | 0    | _          | _                      | ns       |

| Address Hold Time                | $t_AH$           | _              | 0    | _          | _                      | ns       |

| CS, WR "L" Pulse Width for Write | t <sub>CSL</sub> | _              | 40   | _          | _                      | ns       |

| CS, WR "H" Pulse Width for Write | t <sub>CSH</sub> | _              | 40   | _          | _                      | ns       |

| CS, RD "L" Pulse Width for Read  | t <sub>CSL</sub> | _              | 60   | _          | _                      | ns       |

| CS, RD "H" Pulse Width for Read  | t <sub>CSH</sub> | _              | 60   | _          | _                      | ns       |

| Data Setup Time                  | t <sub>DS</sub>  | _              | 30   | _          | _                      | ns       |

| Data Hold Time during Write      | t <sub>DH</sub>  | _              | 5    | _          | _                      | ns       |

| Data Access Time                 | t <sub>ACC</sub> | $C_L = 100 pF$ | _    | _          | 50                     | ns       |

| Data Hold Time during Read       | toH              | _              | 10   | _          | 50                     | ns       |

| System Write Cycle Time          | t <sub>CYC</sub> | _              | 150  | _          | _                      | ns       |

| System Read Cycle Time           | t <sub>CYC</sub> | _              | 166  | _          | _                      | ns       |

| Input Signal Rise Time (*1)      | tr               | _              |      | _          | 15                     | ns       |

| Input Signal Fall Time (*1)      | tf               | _              |      | _          | 15                     | ns       |

(Note) (\*1) Applied to all input pins.

# OSC Frequency

$(V_{DD} = 1.8 \text{ to } 3.0 \text{ V}, \text{ Tj} = 25^{\circ}\text{C})$

|                 |                 |                  |      | ( 00 - | ·· · , , |      |

|-----------------|-----------------|------------------|------|--------|----------|------|

| Parameter       | Symbol          | Condition        | Min. | Тур.   | Max.     | Unit |

|                 | r               | 9PWM, 1/100 duty | 150  | 180    | 210      | Hz   |

| Frame Frequency | T <sub>FR</sub> | 9PWM, 1/128 duty | 180  | 220    | 260      | Hz   |

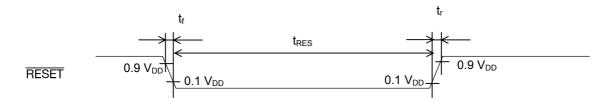

# Reset Timing

$(V_{DD} = 1.8 \text{ to } 3.0 \text{ V}, \text{ Tj} = -40 \text{ to } +85^{\circ}\text{C})$

| Parameter              | Symbol           | Condition | Min. | Тур. | Max. | Unit |

|------------------------|------------------|-----------|------|------|------|------|

| Reset Pulse Width      | t <sub>RES</sub> | _         | 1.5  | _    | _    | μs   |

| Input Signal Rise Time | tr               |           |      | _    | 15   | ns   |

| Input Signal Fall Time | tf               |           |      | _    | 15   | ns   |

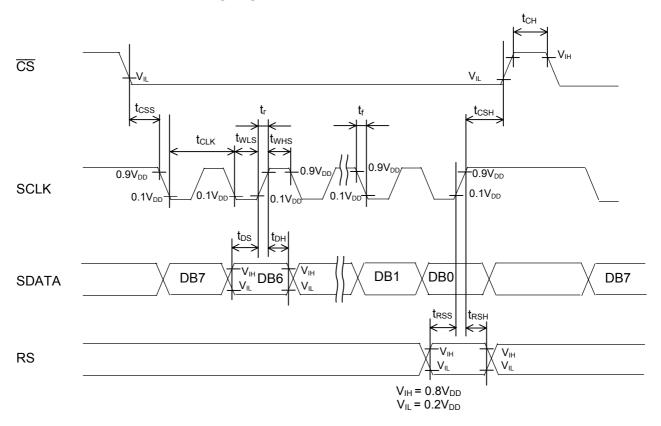

#### **TIMING DIAGRAMS**

#### 3- and 4-Line Serial Interface Timing Diagram

In 3-line system, the ML9055A interfaces with a microcomputer by 3 lines namely,  $\overline{\text{CS}}$ , SCLK, and SDATA.

The method to switch between the data and command in the 3-line system is described in the "Microcomputer Interface" section of Functional Description.

In 4-line system, the ML9055A interfaces with a microcomputer by 4 lines namely  $\overline{CS}$ , SCLK, SDATA, and RS.

If  $\overline{CS}$  holds "L", the display data and command write operations can be executed consecutively. At this time, the chip select setup time,  $t_{CSS}$ , stipulates the time up to the first falling edge of SCLK after the falling edge of  $\overline{CS}$ . And the chip select hold time,  $t_{CSH}$ , stipulates the time from the rising edge of the last SCLK up to the rising edge of  $\overline{CS}$ .

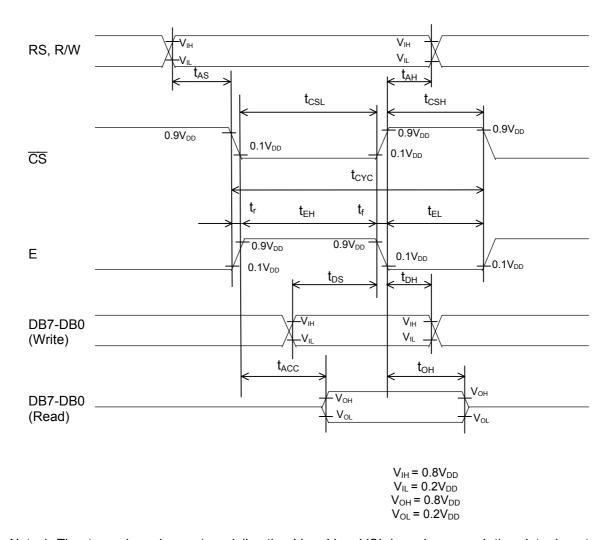

#### Parallel Interface Timing Diagram for 68-Series MPU

- Note 1: The trace impedance (specially, the  $V_{DD}$ ,  $V_{SS}$ , VCI impedance and the data bus trace capacitance etc,) between this chip and circuit board should be designed as low as possible. Factors such as not sufficiently low trace impedance, LCD panel of large size, and high trace impedance of the microcomputer interface, would become a cause of the ML9055A malfunction. In such a situation, use the microcomputer interface not for reading, but for writing only to reduce the power supply noise.

- Note 2: The system cycle time  $t_{\text{CYC}}$  at write and at read is different in the ML9055A. Please keep to the system write time cycle when switching from the write operation to the read operation and, similarly, keep to the system read time cycle when switching from the read operation to the write operation.

- Note 3: The overlapping duration when  $\overline{CS}$  is "L" and E is "H" must satisfy  $t_{CSL}$  or  $t_{EH}$ . Reference points  $t_{AS}$  and  $t_{ACC}$  in this case are decided by  $\overline{CS}$  or E, whichever is slower, and the reference points  $t_{AH}$ ,  $t_{DS}$ ,  $T_{DH}$  and  $t_{OH}$  are decided by  $\overline{CS}$  or E, whichever is faster.

#### Parallel Interface Timing Diagram for 80-Series MPU

Note 1: The trace impedance (specially, the  $V_{DD}$ ,  $V_{SS}$ , VCI impedance and the data bus trace capacitance etc.,) between this chip and circuit board should be designed as low as possible. Factors such as not sufficiently low trace impedance, LCD panel of large size, and high trace impedance of the microcomputer interface, would become a cause of the ML9055A malfunction. In such a situation, use the microcomputer interface not for reading, but for writing only to reduce the power supply noise.

Note 2: The system cycle time  $t_{CYC}$  at write and at read is different in the ML9055A. Please keep to the system write time cycle when switching from the write operation to the read operation and, similarly, keep to the system read time cycle when switching from the read operation to the write operation.

# **Reset Timing**

#### **FUNCTIONAL DESCRIPTION**

#### **Microcomputer Interface**

#### · Serial Interface

The ML9055A communicates with a microcomputer via clock-synchronized serial interface when PS0 holds "L". Read operation is inhibited in the serial interface. Write operation is executed only when  $\overline{CS}$  is low. Data should be input from the most signification bit (MSB). The data latches to the internal shift registers on the rising edge of the serial clock SCLK, and then processed as 8-bit data on the rising edge of the 8th clock. When display data is written to the RAM, the column address is incremented automatically by one only. If  $\overline{CS}$  holds "L", the serial data can be input continuously. If  $\overline{CS}$  goes "H" before 8 serial clocks are sent while the serial data is being input, the discontinued bytes become an invalid data, but the data transmitted prior to that is valid.

The serial interface includes a 3-line serial interface and a 4-line serial interface.

When PS1 is "L", the 3-line serial interface is selected. The 3-line serial interface is composed of serial data (SDATA), serial clock (SCLK), and chip select  $(\overline{CS})$ . The set display data length command identifies whether the data from a microcomputer is a display data or a command data. The specified number of bytes (1 to 256) in data that follow the set display data length command is processed as the display data. And the next byte, after sending the number of display data bytes specified by the set display data length command, is processed as the command data.

If  $\overline{\text{CS}}$  goes "H" while the number of bytes of serial data specified by the set display data length command is being input, the discontinued bytes become an invalid data. And the bytes sent prior to the transmitted data is a valid data. The next input data will be processed as the command data.

When PS1 is "H", the 4-line serial interface is selected. The 4-line serial interface is composed of serial data (SDATA), serial clock (SCLK), chip select  $(\overline{CS})$ , and register select (RS). The register select pin RS is used to differentiate whether the data sent from a microcomputer is a display data or a command data. At RS pin = "H", the input data is a display data. And at RS pin = "L", the input data is a command data.

Note: Do not use the ML9055A with  $\overline{CS}$  tied to "L". Make sure to return the  $\overline{CS}$  to "H" at the end of a command or data input. However, use the ML9055A with  $\overline{CS}$  at "L" when the set display data length command only is input, including the input data, at the end of this command. Return the  $\overline{CS}$  to "H" at the end of all data input.

#### · Parallel Interface

The ML9055A communicates with a microcomputer via the parallel interface when the PS0 is "H". The ML9055A includes a parallel interface for 68-series MPU and a parallel interface for 80-series MPU. When both PS0 and PS1 are "H", the interface is an 8-bit parallel interface for 68-series MPU. Both read and write operations are performed only when the Chip Select  $(\overline{CS})$  pin is "L" and E clock (E) pin is "H". The Register Select (RS) pin is used to discriminate whether the data accessed from a microcomputer is a display data or a command data. When the RS pin is "H", the accessed data is a display data. And when the RS pin is "L", the accessed data is a command data.

Table 1-1. Parallel Interface Function (68-series MPU)

(× Don't care)

| E clock (E) | Register<br>Select (RS) | Chip Select (CS) | Read/Write<br>(R/W) | Operation             |

|-------------|-------------------------|------------------|---------------------|-----------------------|

| Н           | L                       | L                | L                   | Write command data.   |

| Н           | L                       | L                | Н                   | Read status register. |

| Н           | Н                       | L                | L                   | Write display data.   |

| Н           | Н                       | L                | Н                   | Read display data.    |

| L           | ×                       | ×                | ×                   | Invalid               |

| ×           | ×                       | Н                | ×                   | Invalid               |

When PS0 is "H" and PS1 is "L", the interface is an 8-bit parallel interface for 80-series MPU. Both read and write operations are performed only when the Chip Select  $(\overline{CS})$  is "L". The Register Select (RS) pin is used to discriminate whether the data accessed from a microcomputer is a display data or a command data. When the RS pin is "H", the accessed data is a display data. And when the RS pin is "L", the accessed data is a command data.

Table 1-2. Parallel Interface Function (80-series MPU)

(× Don't care)

| Chip Select (CS) | Register<br>Select (RS) | Write (WR) | Read (RD) | Operation             |

|------------------|-------------------------|------------|-----------|-----------------------|

| L                | L                       | L          | Н         | Write command data.   |

| L                | L                       | Н          | L         | Read status register. |

| L                | Н                       | L          | Н         | Write display data.   |

| L                | Н                       | Н          | L         | Write display data.   |

| L                | ×                       | Н          | Н         | Invalid               |

| Н                | ×                       | ×          | ×         | Invalid               |

Note: Do not simultaneously input "L" to  $\overline{WR}$  and  $\overline{RD}$  to avoid the ML9055A malfunction.

#### **LCD Drive Power Supply Circuit**

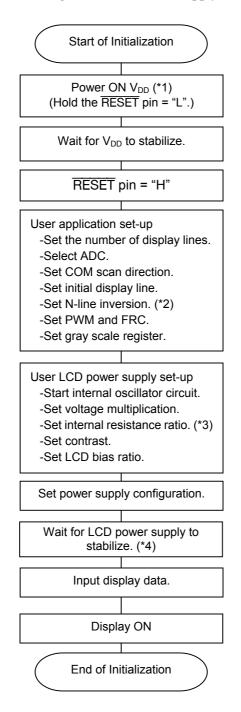

The LCD drive power supply circuit composed of a voltage multiplier (VC), a voltage regulator (VR), and a voltage follower (VF) is controlled by the set power supply configuration instruction.

|                                                   | Power supply                            | LCD drive power supply circuit |     |     | Pin state (Note 2) |                |                |

|---------------------------------------------------|-----------------------------------------|--------------------------------|-----|-----|--------------------|----------------|----------------|

| Configuration                                     | configuration<br>(Note 1)<br>(VC VR VF) | VC                             | VR  | VF  | VOUT               | V0             | V1 – V4        |

| All internal LCD drive power supply circuits used | 1 1 1                                   | ON                             | ON  | ON  | Output             | Output         | Output         |

| Voltage regulator and voltage follower used       | 0 1 1                                   | OFF                            | ON  | ON  | External input     | Output         | Output         |

| Voltage follower only used                        | 0 0 1                                   | OFF                            | OFF | ON  | Shorted with V0    | External input | Output         |

| External power supply used                        | 0 0 0                                   | OFF                            | OFF | OFF | Shorted with V0    | External input | External input |

**Table 2. Power Supply Circuit Configuration**

Note 1: Although the set power supply configuration instruction allows to input commands to perform settings also of combinations other than shown in Table 2, do not perform such settings as would cause the ML9055A malfunction.

Note 2: When the pin state is "output", connect the specified capacitors to VOUT, V0 and V1 to V4.

#### Voltage multiplier

The voltage multiplier is used to increase the VCI voltage applied to VCI pin up to the set multiple value. The setting enable voltage multiples are  $\times 3$ ,  $\times 4$ ,  $\times 5$ , and  $\times 6$ . These multiples are set by the voltage multiplication instruction. After voltage multiplication, the voltage is output from VOUT pin, which is used as a power supply for the voltage regulator and voltage follower.

A voltage multiplier is configured in conjunction with external capacitors. As shown in Figure 1, to configure  $\times 3$  to  $\times 6$  multiplications, connect appropriate capacitors to the chip externally. Connect the capacitors to configure a voltage multiplier with the maximum multiplication used. Do not set the voltage multiplication by a command larger than the enable setting by the external capacitors because it would become a cause of the ML9055 unstable operation.

Note: Use the voltage multiplier output voltage VOUT, and the LCD drive voltage V0, at the recommended operating voltage 16.0 V or below.

Figure 1. Voltage Multiplier Setting (C =  $0.8 \mu F$  to  $5.7 \mu F$ )

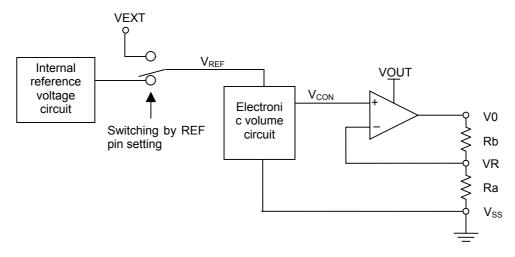

#### Voltage Regulator Circuit

Figure 2. Voltage Regulator Circuit

The voltage regulator is composed of an internal reference voltage circuit, an electronic volume circuit, and an amplifier circuit. The internal reference voltage circuit outputs the reference voltage,  $V_{REF} = 2.1 \text{ V}$  (Tj = 25°C). This reference voltage  $V_{REF}$  has a temperature co-efficient of 0.125%/°C.

The reference voltage  $V_{REF}$  is input to the electronic volume circuit.  $V_{REF}$  can be input from VEXT pin also by the set REF pin instruction. (Refer to Table 3.)

| REF | Temp. coefficient                               | V <sub>REF</sub> (V) |

|-----|-------------------------------------------------|----------------------|

| L   | (Depends on externally connected power supply.) | VEXT pin value       |

| Н   | _0.125%/°C                                      | 21V                  |

Table 3. V<sub>REF</sub> Voltage at Tj = 25°C

The electronic volume circuit converts the input reference voltage,  $V_{\text{REF}}$ , to the contrast control voltage, Vcon, expressed by the following equation:

$$V_{CON} = (1 - (63 - a)/210) \times V_{REF}$$

Here, parameter "a" is the contrast setting value shown in Table 4. (Levels 0 to 63 can be set.)

**Table 4. Contrast Setting Value**

| <br>Contrast setting value |    |    |    |    | Parameter |    |

|----------------------------|----|----|----|----|-----------|----|

| C5                         | C4 | C3 | C2 | C1 | C0        | а  |

| 0                          | 0  | 0  | 0  | 0  | 0         | 0  |

| 0                          | 0  | 0  | 0  | 0  | 1         | 1  |

| 0                          | 0  | 0  | 0  | 1  | 0         | 2  |

| 0                          | 0  | 0  | 0  | 1  | 1         | 3  |

| 0                          | 0  | 0  | 1  | 0  | 0         | 4  |

|                            |    |    | :  |    |           | :  |

| 1                          | 1  | 1  | 1  | 1  | 0         | 62 |

| 1                          | 1  | 1  | 1  | 1  | 1         | 63 |

The contrast control voltage Vcon, that is output from the electronic volume circuit, is input to the amplifier circuit and amplified to the LCD drive voltage V0, expressed by the following equation by the ratio of resistor Ra to Rb.

$$V0 = (1 + Rb/Ra) \times V_{CON}$$

Resistor Ra and resistor Rb can select either internal or external resistor by INTRS pin setting.

# • Internal Resistor Configuration

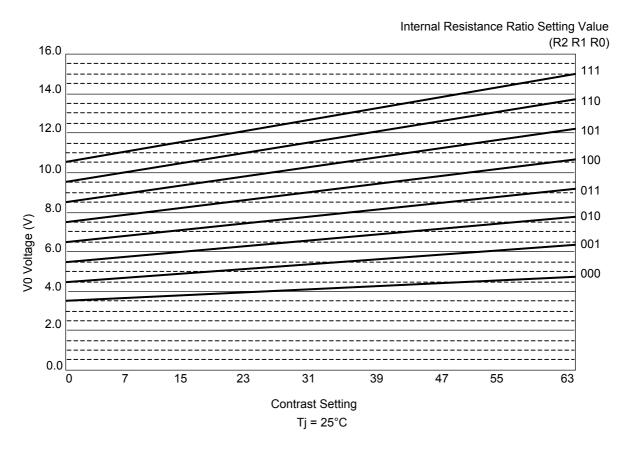

When "H" is input to INTRS pin, resistor Ra and resistor Rb in the IC are selected. The resistance ratio Rb/Ra is determined by the set internal resistance ratio command. Table 5 shows amplification factor of the amplifier circuit.

Figure 3 shows the variable range of LCD drive voltage V0 at  $Tj = 25^{\circ}C$  when using the internal resistors.

**Table 5. Internal Resistance Ratio Setting**

| Internal resistance ratio setting value | Amplification factor |

|-----------------------------------------|----------------------|

| R2 R1 R0                                | 1 + Rb/Ra            |

| 0 0 0                                   | 2.3                  |

| 0 0 1                                   | 3.0                  |

| 0 1 0                                   | 3.7                  |

| 0 1 1                                   | 4.4                  |

| 1 0 0                                   | 5.1                  |

| 1 0 1                                   | 5.8                  |

| 1 1 0                                   | 6.5                  |

| 1 1 1                                   | 7.2                  |

#### • External Resistor Configuration

When "L" is input to the INTRS pin, the internal resistors are separated and the externally connected resistors Ra and Rb set the amplification factor. Similar to Figure 2, connect an external resistor Ra across VR and  $V_{SS}$  pins, and an external resistor Rb across VR and  $V_{O}$  pins.

Note: The sum of the externally connected resistors Ra and Rb should be in the 500 k $\Omega$  to 5 M $\Omega$  range.

Figure 3. V0 Variable Range When Using Internal Reference Voltage and Internal Resistors

# • Voltage Follower Circuit

With LCD drive voltage V0 as a reference voltage, 4 LCD drive bias voltages are generated. The LCD bias is determined by the set LCD bias ratio command. The available bias levels are: 1/5, 1/6, 1/7, 1/8, 1/9, 1/10, 1/11, and 1/12. Connect capacitors of  $0.376~\mu F$  to  $2.4~\mu F$  to the voltage follower outputs for stabilizing the voltage.

To determine optimal bias setting:

Let the display duty be 1/D, then the optimal bias ratio is  $1/(1 + \sqrt{D})$ .

Table 6. LCD Drive Voltage Levels vs. Bias

| LCD drive bias ratio | V1           | V2           | V3              | V4              |

|----------------------|--------------|--------------|-----------------|-----------------|

| 1/n                  | (n−1)/n × V0 | (n-2)/n × V0 | $2/n \times V0$ | $1/n \times V0$ |

Power Supply Configuration Examples  $V_{\text{DD}} \\$  $V_{DD}$ INTRS INTRS REF **INTRS** REF REF VCI VCI VCI VEXT VEXT VEXT VOUT VOUT VOUT External C5+ C4+ C3+ C2+ C2-C1+ C5+ power Capacitors Capacitors supply for multiplying multiplying C2 C2 voltage voltage C1-VR VR VR Ra C1 C1 C1 V0 V٥ V0 C1 C1 C1 V1 V1 V1 C1 C1 C1 V2 V2 V2 C1 C1 C1 V3 V3 V3 C1 C1 C1 V4 V4 V4 (b) Using all internal power (c) Using all external reference power (a) Using all internal power supplies and internal supplies and external supply, voltage follower, and resistors internal resistors resistors  $V_{\text{DD}}$  $V_{DD}$ **INTRS** REF INTRS REF INTRS REF VCI VCI VCI VEXT VEXT **VEXT** VOUT VOUT VOUT C5+ C4+ C3+ C2+ C2-C1+ C5+ C4+ C3+ C2+ C2-C1+ C5+ C4+ C3+ C2+ C2-C1+ External power supply External C1-C1-C1power VR VR VR supply C1 V0 V0 V0 C1 C1 V1 V1 V1 Externa C1 C1 V2 V2 V2 power C1 C1 V3 supply V3 V3 C1 C1 V4 V4 V4 (f) Using external power (e) Using voltage follower (d) Using voltage regulator, voltage

Figure 4. Power Supply Configuration Examples

follower, and internal resistors

- Note 1: The bias capacitor C1 connected to the LCD drive bias pin should be in the 0.376  $\mu$ F to 2.4  $\mu$ F range. And the capacitors for multiplying voltage connected to the connect pins for these capacitors, and stabilizing capacitor C2 connected to the voltage multiplier input/output pin VOUT should be in the 0.8  $\mu$ F to 5.7  $\mu$ F range.

- Note 2: In the case of using an external power supply, apply V<sub>SS</sub> to pin VCI. And when not using an external reference voltage, keep the pin VEXT open.

supply only

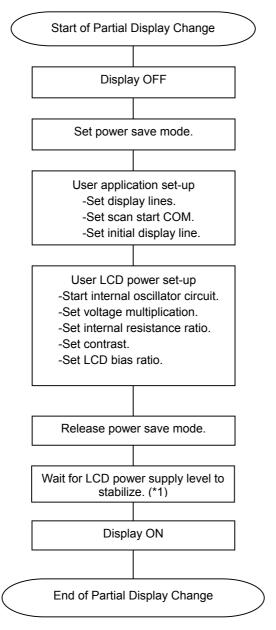

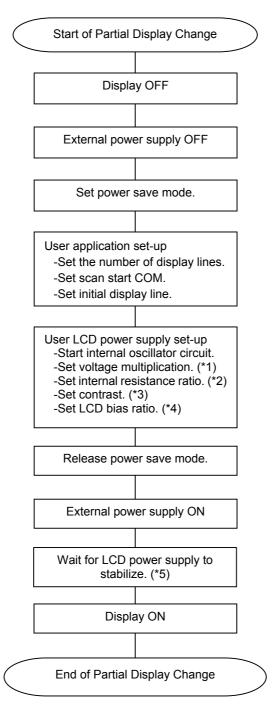

#### **Partial Display Function**

The set display lines count instruction allows the display duty to be set to any value from 1/16 duty to 1/128 duty line-by-line, and also allows the display duty to be set according to the used panel.

Also, the partial display function can display a part of the common lines only on the used LCD panel out of the total common lines, and accordingly sets the supply voltages, bias ratio and voltage multiplication thus reducing the current consumption. The method of changing the number of display lines is described in the "Partial Display Change Sequence" section of the OPERATING SEQUENCE.

#### **Display Data RAM**

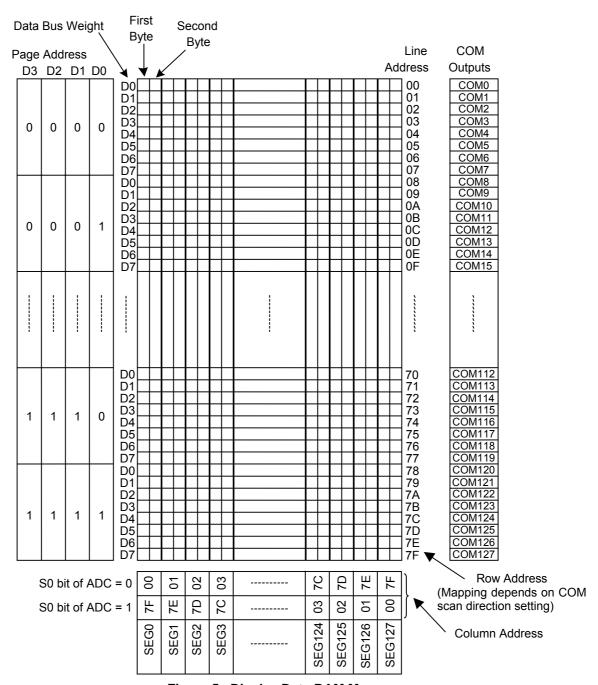

For performing the bit-map display in the ML9055A, the data RAM is arranged into 2-dimensional 128 rows × 128 columns corresponding to the display image, and a specific element is specified by the row address (0 to 127) and column address (0 to 127). Each element stores a 2-bit data that indicates the level of gradation i.e., gray scale, of a pixel corresponding to an element. (Refer to Figure 5.)

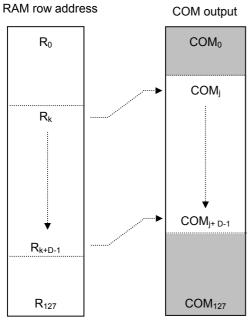

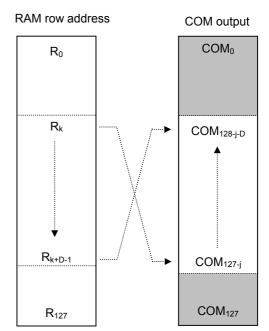

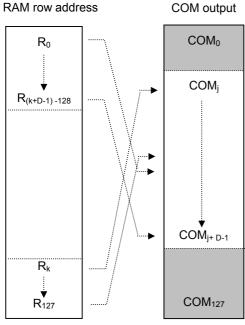

The relationship between COM output numbers and RAM row addresses can be reversed by the set COM scan direction command. The relationship between SEG output numbers and RAM column addresses can be reversed by the ADC select command. This enhances the freedom in relationship between the panel and chip location at the time of implementation.

Moreover, it is possible to provide an offset to the row addresses and COM numbers by the set scanning start COM command allowing to scroll a display in the common direction. (Refer to Figure 6.)

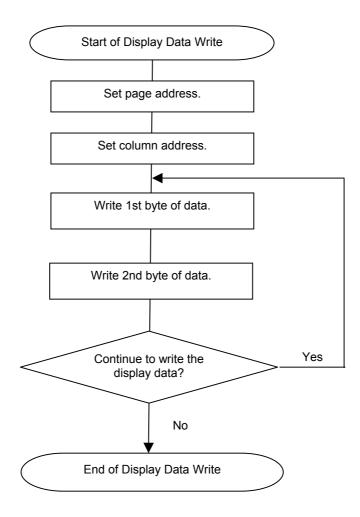

Since the microcomputer interface data is in bytes, the data for 8 pixels of 8 rows  $\times$  1 column is collectively handled as 1 byte. For this reason, the RAM read/write location is specified by the upper 4 bits of a row address (called a page address) and a column address. In byte, the larger row address side is positioned to the upper bit side. Since 1 pixel data consists of 2 bits, the read/write operations are performed in the order of upper/lower bits by accessing 2 times consecutively.

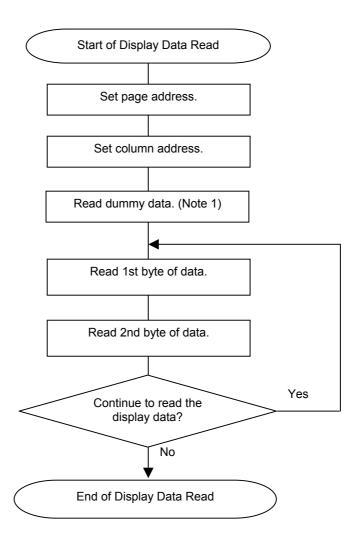

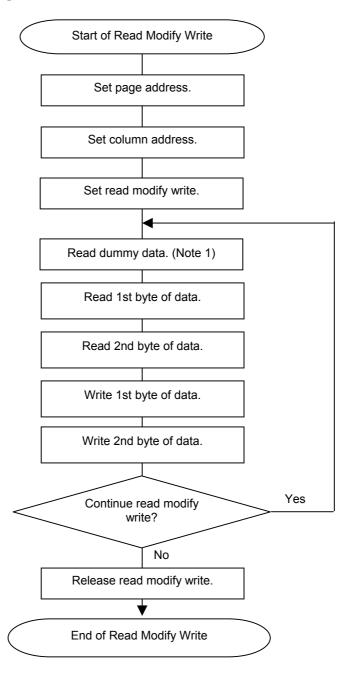

As for the access procedure, the page address and column address are first set by command followed by the execution of display data read/write commands. It is not necessary to set again the column address when reading/writing the display data on the same page in the order of column address by the column address automatic increment function. Meanwhile, when reading, it is necessary to read a dummy display data once between the address setting and display data reading. For additional details, refer to the Display Data Write Sequence, Display Data Read Sequence, and Read Modify Write Sequence in the OPERATING SEQUENCE section.

Figure 5. Display Data RAM Map

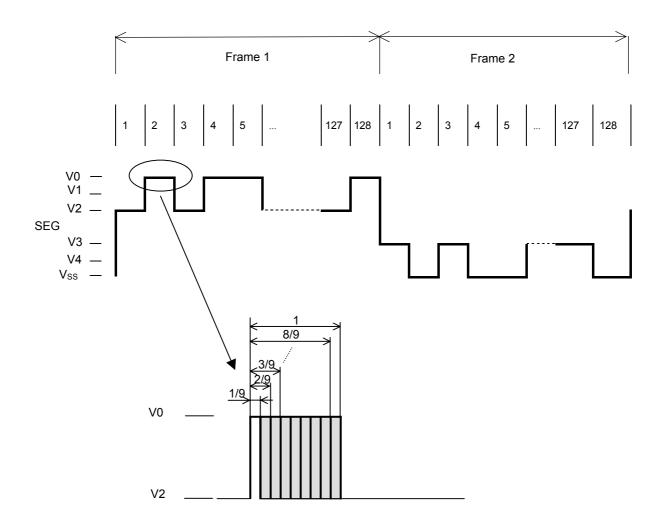

(a) COM scan direction SC0 = 0Scan start COM setting = jDisplay start row address setting = kDisplay line count setting = D

(b) COM scan direction SC0 = 1Scan start COM setting = jDisplay start row address setting = kDisplay line count setting = D

(c) COM scan direction SC0 = 0

Scan start COM setting = j

Display start row address setting = k

Display line count setting = D

In the case of j+D > 128

(b) COM scan direction SC0 = 1

Scan start COM setting = j

Display start row address setting = k

Display line count setting = D

In the case of j+D > 128

Figure 6. Relationship Between RAM Row Address Setting and COM Output

#### **Gray Scale Display**

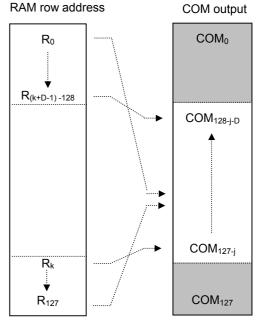

In order to perform 4 gray scales (black, dark gray, light gray, and white) on a display, the ML9055A can set the lighting level pulse width of a segment drive waveform every frame for the 2-bit display data. This allows the ML9055A to support 2 modulation methods: pulse width modulation (PWM) and frame modulation (FRC), which in turn allows flexible setting according to the panel characteristics.

For the frame cycle, which performs modulation, 3 frames or 4 frames can be selected by the set FRC field of FRC/PWM mode command. And 9, 12 or 15 can be selected as the number of PWM pulse width setting steps by the PWM1 and PWM0 fields, and the lighting pulse width of every frame of each gray scale is set by the set pulse width command. (Refer to Tables 7 and 8.)

Example: In the setting (inversion display off) shown in Table 9, in pixels of the display RAM data 11, all the 3 frames output the segment drive waveform of pulse width 9/9 (driver voltage effective value maximum). Similarly, in pixels of the RAM data 10, the 1st and 2nd frames output the segment drive waveform of pulse width 9/9, and the 3rd frame outputs pulse width 0/9. In pixels of the RAM data 01, the 1st frame, 2nd frame and 3rd frame output the segment drive waveform of pulse width 9/9, 3/9 and 0/9, respectively. In pixels of the RAM data 00, all 3 frames output the segment drive waveform of pulse width 0/9 (driver voltage effective value minimum).

Note: In order to avoid the occurrence of DC offset when using the 4-frame FRC, determine the pulse width setting values of each gray scale such that the sum of values of even number frames is equal to the sum of values of odd number frames.

RAM bit **PWM Binary Setting** G/S (1st Byte/ 2nd frame PWM 1st frame PWM 3rd frame PWM 4th frame PWM 2nd Byte) (BB3-BB0) (BD3-BD0) 11 Black (BA3-BA0) (BC3-BC0) 10 (DB3-DB0) (DC3-DC0) Dark Gray (DA3-DA0) (DD3-DD0) (LA3-LA0) (LD3-LD0) 01 Light Gray (LB3-LB0) (LC3-LC0) 00 White (WA3-WA0) (WB3-WB0) (WC3-WC0) (WD3-WD0)

Table 7. PWM Binary Setting for 4-frame FRC

| Table 8. PWN | /I Binary Setting | g for 3-frame FRC |

|--------------|-------------------|-------------------|

|--------------|-------------------|-------------------|

| RAM bit                 |            |               | PWM Binary Setting |               |

|-------------------------|------------|---------------|--------------------|---------------|

| (1st Byte/<br>2nd Byte) | G/S        | 1st frame PWM | 2nd frame PWM      | 3rd frame PWM |

| 11                      | Black      | (BA3-BA0)     | (BB3-BB0)          | (BC3-BC0)     |

| 10                      | Dark Gray  | (DA3-DA0)     | (DB3-DB0)          | (DC3-DC0)     |

| 01                      | Light Gray | (LA3-LA0)     | (LB3-LB0)          | (LC3-LC0)     |

| 00                      | White      | (WA3-WA0)     | (WB3-WB0)          | (WC3-WC0)     |

Table 9. Example of PWM Binary Setting (3-frame FRC and 9-level PWM)

| G/S        |               | PWM Binary Setting |               |

|------------|---------------|--------------------|---------------|

|            | 1st frame PWM | 2nd frame PWM      | 3rd frame PWM |

| Black      | 1001          | 1001               | 1001          |

| Dark Gray  | 1001          | 1001               | 0000          |

| Light Gray | 1001          | 0011               | 0000          |

| White      | 0000          | 0000               | 0000          |

Table 10. 9-Level PWM Settings

| Decimal Value | Binary Setting(*1) | PWM Setting | Visual Appearance      |  |

|---------------|--------------------|-------------|------------------------|--|

| 0             | 0000               | 0           | Lightest               |  |

| 1             | 0001               | 1/9         |                        |  |

| 2             | 0010               | 2/9         |                        |  |

| 3             | 0011               | 3/9         |                        |  |

| 4             | 0100               | 4/9         |                        |  |

| 5             | 0101               | 5/9         |                        |  |

| 6             | 0110               | 6/9         |                        |  |

| 7             | 0111               | 7/9         |                        |  |

| 8             | 1000               | 8/9         |                        |  |

| 9             | 1001               | 1           | Darkest                |  |

| 10            | 1010               | 0           |                        |  |

| 11            | 1011               | 0           |                        |  |

| 12            | 1100               | 0           | Set to lightest level  |  |

| 13            | 1101               | 0           | Set to lightest level. |  |

| 14            | 1110               | 0           |                        |  |

| 15            | 1111               | 0           |                        |  |

(\*1) The binary setting value can be any one of WA3-0, LA3-0, DA3-0, BA3-0, WB3-0, LB3-0, DB3-0, BB3-0, WC3-0, LC3-0, DC3-0, BC3-0, WD3-0, LD3-0, DD3-0, and BD3-0.

Table 11. 12-Level PWM Settings

| Decimal Value | Binary Setting(*1) | PWM Setting | Visual Appearance      |

|---------------|--------------------|-------------|------------------------|

| 0             | 0000               | 0           | Lightest               |

| 1             | 0001               | 1/12        |                        |

| 2             | 0010               | 2/12        |                        |

| 3             | 0011               | 3/12        |                        |

| 4             | 0100               | 4/12        |                        |

| 5             | 0101               | 5/12        |                        |

| 6             | 0110               | 6/12        |                        |

| 7             | 0111               | 7/12        |                        |

| 8             | 1000               | 8/12        |                        |

| 9             | 1001               | 9/12        |                        |

| 10            | 1010               | 10/12       |                        |

| 11            | 1011               | 11/12       |                        |

| 12            | 1100               | 1           | Darkest                |

| 13            | 1101               | 0           |                        |

| 14            | 1110               | 0           | Set to lightest level. |

| 15            | 1111               | 0           |                        |

(\*1) The binary setting value can be any one of WA3-0, LA3-0, DA3-0, BA3-0, WB3-0, LB3-0, DB3-0, BB3-0, WC3-0, LC3-0, DC3-0, BC3-0, WD3-0, LD3-0, DD3-0, and BD3-0.

**Table 12. 15-Level PWM Settings**

| Decimal Value | Binary Setting(*1) | PWM Setting | Visual Appearance |

|---------------|--------------------|-------------|-------------------|

| 0             | 0000               | 0           | Lightest          |

| 1             | 0001               | 1/15        |                   |

| 2             | 0010               | 2/15        |                   |

| 3             | 0011               | 3/15        |                   |

| 4             | 0100               | 4/15        |                   |

| 5             | 0101               | 5/15        |                   |

| 6             | 0110               | 6/15        |                   |

| 7             | 0111               | 7/15        |                   |

| 8             | 1000               | 8/15        |                   |

| 9             | 1001               | 9/15        |                   |

| 10            | 1010               | 10/15       |                   |

| 11            | 1011               | 11/15       |                   |

| 12            | 1100               | 12/15       |                   |

| 13            | 1101               | 13/15       |                   |

| 14            | 1110               | 14/15       | ·                 |

| 15            | 1111               | 1           | Darkest           |

<sup>(\*1)</sup> Binary Setting Values are WA3–0, LA3–0, DA3–0, BA3–0, WB3–0, LB3–0, DB3–0, BB3–0, WC3–0, LC3–0, DC3–0, BC3–0, WD3–0, LD3–0, DD3–0, or BD3–0.

Figure 7. Example of 9-Level PWM Segment Waveform

# **Instruction Description**

# **Table 13. Instruction Set List**

| Х. | D١ | ٦n | ۱'t | റമ | rc |

|----|----|----|-----|----|----|

|    |    |    |     |    |    |

|    |        |        |     |          |          |         |         |         |         | x: Don't care                                                                                                                                                                        |

|----|--------|--------|-----|----------|----------|---------|---------|---------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RS | R/W    | D7     | D6  | D5       | D4       | D3      | D2      | D1      | D0      | Description                                                                                                                                                                          |

| 0  | 1      | BUSY   | ON  | RES      | 1        | 0       | 1       | 1       | 0       | Read internal status.                                                                                                                                                                |

| 1  | 0      |        |     |          | Write da | ata     |         |         |         | Write display data.                                                                                                                                                                  |

| 1  | 1      |        |     |          | Read da  | ata     |         |         |         | Read display data.                                                                                                                                                                   |

| 0  | 0      | 0      | 0   | 0        | 0        | C3      | C2      | C1      | C0      | Set column address (lower digits).                                                                                                                                                   |

| 0  | 0      | 0      | 0   | 0        | 1        | 0       | C6      | C5      | C4      | Set column address (upper digits).                                                                                                                                                   |