# **ML671000**

OKI's CMOS 32-Bit Single-Chip Microcontroller with Built-in USB Device Controller

#### **GENERAL DESCRIPTION**

The ML671000 is a high-performance CMOS 32-bit microcontroller combining a RISC based, 32-bit CPU core - the ARM7TDMI<sup>TM</sup> - with USB device controller, memory and peripherals.

This version:

Previous version: Jul. 2001

Jul. 2001

The built-in USB device controller which is based on USB1.1 Full-speed (12 Mbps) makes interface with PCs or other devices by USB. The ML671000, which provides the 32-bit data processing capability and built-in peripheral functions performed by UART, serial ports, 16-bit timers, a DMA controller, and a memory controller, is a single-chip microcontroller idealy suited to PC peripheral equipment and communication terminal control applications.

## **FEATURES (1)**

| CPU                   | RISC 32-bit CPU (ARM7TDMI)  Executable 32-bit instructions and 16-bit instructions  General registers: 32-bit × 31 registers  Built-in multiplier  Little-endian format                                                                                                                                                                                                              |  |  |  |  |  |

|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Memory Spaces         | Internal RAM: 4K bytes External ROM, RAM, I/O: 26M bytes External DRAM: 32M bytes                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

| I/O Ports             | I/O pins: 64 pins (I/O directions are specified at the bit level)                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

| Timers                | 16-bit flexible timer × 2ch (auto-reload, compare-output, PWM, capture modes) 16-bit auto-reload timer × 2ch 12-bit watchdog timer                                                                                                                                                                                                                                                   |  |  |  |  |  |

| Serial Ports          | UART (16550A equivalent) × 1ch, UART/synchronous serial × 1ch                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

| USB Device Controller | USB1.1 compliant, support full-speed (12 Mbps) Transmission type: control, bulk, isochronous, interrupt Remote wakeup function Adaptable to USB bus powered devices Four endpoint addresses Endpoint FIFO size  EP0 64 bytes × 2 (transmit/receive) EP1 64 bytes × 1 (transmit-receive) EP2 64 bytes × 2 (transmit-receive, 2 levels) EP3 256 bytes × 2 (transmit-receive, 2 levels) |  |  |  |  |  |

| DMA Controller        | × 2ch Single and Dual addressing modes Cycle steal and Burst transfers 8- or 16-bit data transfers Maximum transferring: 65536 times Addressing area: 64M bytes                                                                                                                                                                                                                      |  |  |  |  |  |

ARM7TDMI and the ARM POWERED logo are registered trademarks of ARM Ltd., UK.

The information contained herein can change without notice owing to the product being under development.

## FEATURES (2)

| Interrupt Controller        | Interrupt sources: 22 (13 internal , 9 external ) Interrupt priority: 8 levels                                                                                                                                           |

|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Memory Controller           | Direct connection to ROM, SRAM, DRAM and I/O. 4-bank memory control ROM, RAM, I/O × 2 banks; DRAM × 2 banks Access wait control parameters for each bank.                                                                |

| Other                       | Arbitration of external bus request  Power saving functions Standby modes: HALT and STOP modes Clock gears: Selection of 1/2 OSC, 1/1 OSC, OSC ×2  Onboard debugging is possible with JTAG interface.  Built-in PLL: × 4 |

| Power Supply Voltage        | 3.0 to 3.6 V                                                                                                                                                                                                             |

| Operating Frequency         | CPU: 6, 12, 24 MHz; USB: 48 MHz @12 MHz (Operating USBC) CPU: 4 to 24 MHz (Non-Operating USBC)                                                                                                                           |

| Operating Temperature Range | -10°C to +70°C                                                                                                                                                                                                           |

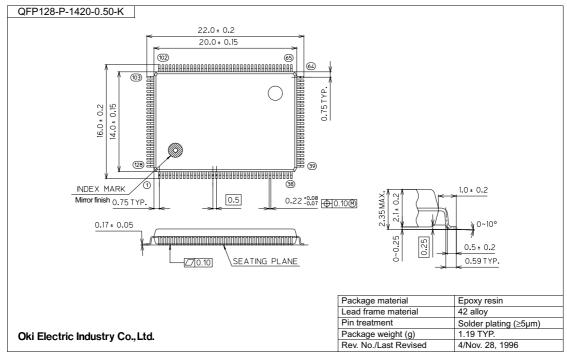

| Package                     | 128-pin plastic QFP (QFP128-P-1420-0.50-K)                                                                                                                                                                               |

## **APPLICATIONS**

Digital still camera, Printer, Terminal Adapter for PC peripherals and Communication terminals.

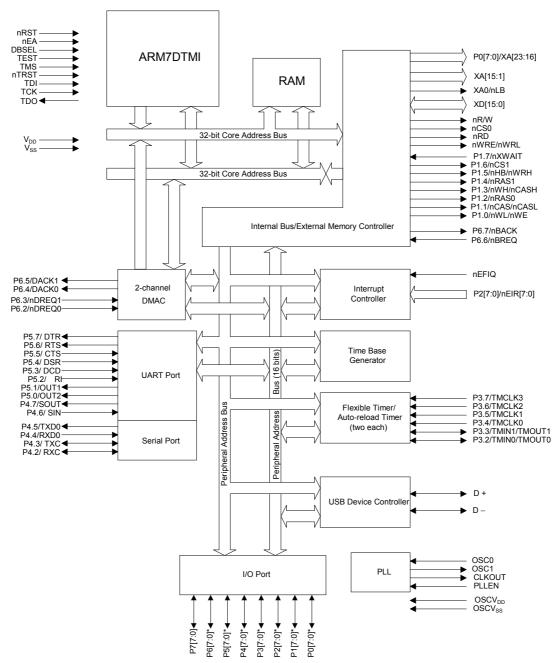

### **BLOCK DIAGRAM**

Asterisks indicate pins with secondary functions.

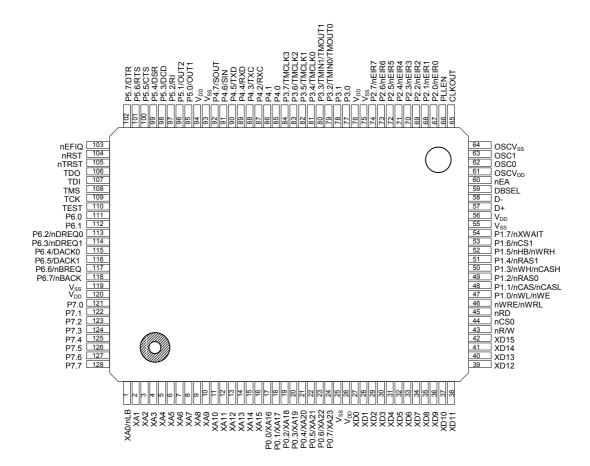

### PIN CONFIGURATION (TOP VIEW)

128-Pin Plastic QFP

## PIN DESCRIPTION (1)

| Classification | Pin Name           | I/O | Function  | Description                                                                                                               |

|----------------|--------------------|-----|-----------|---------------------------------------------------------------------------------------------------------------------------|

| Address Bus    | XA15 to XA1        | 0   | _         | External address bus bits 15 to 1                                                                                         |

|                | nLB/XA0            | 0   | _         | Bank 0/1 lower byte select or external address bus bit 0                                                                  |

| Data Bus       | XD15 to XD0        | I/O | _         | External data bus                                                                                                         |

|                | nCS0               | 0   | _         | Bank 0 chip select signal                                                                                                 |

| Desa Constant  | nRD                | 0   | _         | Bank 0/1 read enable signal                                                                                               |

| Bus Control    | nR/W               | 0   | _         | Read strobe signal                                                                                                        |

|                | nWRE/nWRL          | 0   | _         | Bank 0/1 write enable or lower byte write enable signal                                                                   |

|                | OSC0               | I   | _         | Connection pin for crystal oscillator or ceramic resonator If an external clock used, input the clock signal to this pin. |

|                | OSC1               | 0   | _         | Connection pin for crystal oscillator or ceramic resonator If an external clock used, leave this pin open (unconnected).  |

| Clock Control  | CLKOUT             | 0   | _         | Internal system clock output                                                                                              |

|                | PLLEN              | Ī   | _         | Enable pin for internal PLL. If PLL is to be used, connect this pin to V <sub>DD</sub> .                                  |

|                | OSCV <sub>DD</sub> | Ī   | _         | Power supply pin for internal oscillator circuit and PLL. Connect to $V_{DD}$ .                                           |

|                | OSCV <sub>SS</sub> | I   | _         | Power supply pin for internal oscillator circuit and PLL. Connect to GND.                                                 |

|                |                    | I/O | Primary   | Bit 7 of port 0                                                                                                           |

|                | P0.7/XA23          | 0   | Secondary | Bit 23 of external address bus                                                                                            |

|                |                    | 1/0 | Primary   | Bit 6 of port 0                                                                                                           |

|                | P0.6/XA22          | 0   | Secondary | Bit 22 of external address bus                                                                                            |

|                |                    | 1/0 | Primary   | Bit 5 of port 0                                                                                                           |

|                | P0.5/XA21          | 0   | Secondary |                                                                                                                           |

|                | P0.4/XA20          | 1/0 | Primary   | Bit 4 of port 0                                                                                                           |

|                |                    | 0   | Secondary | Bit 20 of external address bus                                                                                            |

|                | P0.3/XA19          | I/O | Primary   | Bit 3 of port 0                                                                                                           |

|                |                    | 0   | Secondary | Bit 19 of external address bus                                                                                            |

|                |                    | I/O | Primary   | Bit 2 of port 0                                                                                                           |

|                | P0.2/XA18          | 0   | Secondary | Bit 18 of external address bus                                                                                            |

|                | P0.1/XA17          | I/O | Primary   | Bit 1 of port 0                                                                                                           |

|                | PU. 1/AA 17        | 0   | Secondary | Bit 17 of external address bus                                                                                            |

|                | P0.0/XA16          | I/O | Primary   | Bit 0 of port 0                                                                                                           |

|                | P0.0/XA16          | 0   | Secondary | Bit 16 of external address bus                                                                                            |

| I/O Ports      | P1.7/nXWAIT        | I/O | Primary   | Bit 7 of port 1                                                                                                           |

|                | 1 1.7/IIXWAII      | I   | Secondary | External wait cycle insert input                                                                                          |

|                | P1.6/nCS1          | I/O | Primary   | Bit 6 of port 1                                                                                                           |

|                | 1 1.0/11001        | 0   | Secondary | Bank 1 chip select signal                                                                                                 |

|                | P1.5/nHB/          | I/O | Primary   | Bit 5 of port 1                                                                                                           |

|                | nWRH               | 0   | Secondary | Bank 0/1 upper byte select or upper byte write enable signal                                                              |

|                | P1.4/nRAS1         | I/O | Primary   | Bit 4 of port 1                                                                                                           |

|                | 1 1.4/1110-01      | 0   | Secondary | Bank 3 row address strobe signal                                                                                          |

|                | P1.3/              | I/O | Primary   | Bit 3 of port 1                                                                                                           |

|                | nWH/nCASH          | 0   | Secondary | Bank 2/3 upper byte column address strobe signal.                                                                         |

|                | P1.2/nRAS0         | I/O | Primary   | Bit 2 of port 1                                                                                                           |

|                | . 1.2/1110-000     | 0   | Secondary | Bank 2 row address strobe signal                                                                                          |

|                | P1.1/              | I/O | Primary   | Bit 1 of port 1                                                                                                           |

|                | nCAS/nCASL         | 0   | Secondary | Bank 2/3 column address strobe or lower byte column address strobe signal                                                 |

|                | P1.0/              | I/O | Primary   | Bit 0 of port 1                                                                                                           |

|                | nWL/nWE            | 0   | Secondary | Bank 2/3 lower byte write enable or write enable signal                                                                   |

## PIN DESCRIPTION (2)

| Classification | Pin Name                  | I/O  | Function                                         | Description                                                          |  |  |  |  |

|----------------|---------------------------|------|--------------------------------------------------|----------------------------------------------------------------------|--|--|--|--|

|                | P2.7/nEIR7                | I/O  | Primary                                          | Bit 7 of port 2                                                      |  |  |  |  |

|                | PZ.//IIEIR/               | ı    | Secondary                                        | External interrupt request 7 input pin                               |  |  |  |  |

|                | D0.0/=FID0                | I/O  | Primary                                          | Bit 6 of port 2                                                      |  |  |  |  |

|                | P2.6/nEIR6                | ı    | Secondary                                        | External interrupt request 6 input pin                               |  |  |  |  |

|                | D0 5/- 51D5               | I/O  | Primary                                          | Bit 5 of port 2                                                      |  |  |  |  |

|                | P2.5/nEIR5                | -    | Secondary                                        | External interrupt request 5 input pin                               |  |  |  |  |

|                | DO 4/ EID4                | I/O  | Primary                                          | Bit 4 of port 2                                                      |  |  |  |  |

|                | P2.4/nEIR4                | ı    | Secondary                                        | External interrupt request 4 input pin                               |  |  |  |  |

|                | D0 0/=CID0                | I/O  | Primary                                          | Bit 3 of port 2                                                      |  |  |  |  |

|                | P2.3/nEIR3                |      | Secondary                                        | External interrupt request 3 input pin                               |  |  |  |  |

|                | P2.2/nEIR2                | I/O  | Primary                                          | Bit 2 of port 2                                                      |  |  |  |  |

|                | PZ.Z/IIEIRZ               | ı    | Secondary                                        | External interrupt request 2 input pin                               |  |  |  |  |

|                | P2.1/nEIR1                | I/O  | Primary                                          | Bit 1 of port 2                                                      |  |  |  |  |

|                | PZ. I/IIEIR I             | ı    | Secondary                                        | External interrupt request 1 input pin                               |  |  |  |  |

|                | P2.0/nEIR0                | I/O  | Primary                                          | Bit 0 of port 2                                                      |  |  |  |  |

|                | F2.0/IIEIRU               |      | Secondary                                        | External interrupt request 0 input pin                               |  |  |  |  |

|                | P3.7/TMCLK3               | I/O  | Primary                                          | Bit 7 of port 3                                                      |  |  |  |  |

|                | F3.7/TIVICENS             |      | Secondary                                        | External clock input pin for timer 3                                 |  |  |  |  |

|                | P3.6/TMCLK2               | 1/0  | Primary                                          | Bit 6 of port 3                                                      |  |  |  |  |

|                | F 3.0/ TWICENZ            |      | Secondary                                        | External clock input pin for timer 2                                 |  |  |  |  |

|                | P3.5/TMCLK1               | I/O  | Primary                                          | Bit 5 of port 3                                                      |  |  |  |  |

|                | F 3.3/ TWOLK I            |      | I Secondary External clock input pin for timer 1 |                                                                      |  |  |  |  |

|                | P3.4/TMCLK0               | I/O  | Primary                                          | Bit 4 of port 3                                                      |  |  |  |  |

| I/O Ports      | 1 3.4/ TWOLKO             | - 1  | Secondary                                        | External clock input pin for timer 0                                 |  |  |  |  |

|                | P3.3/                     | I/O  | Primary                                          | Bit 3 of port 3                                                      |  |  |  |  |

|                | TMIN1/                    |      | Secondary                                        | If timer 1 is set to the compare-output or PWM modes, this pin is an |  |  |  |  |

|                | TMOUT1                    | I/O  |                                                  | output.                                                              |  |  |  |  |

|                |                           | 1/0  | ·                                                | If set to the capture mode, this pin is an input.                    |  |  |  |  |

|                | P3.2/<br>TMIN1/<br>TMOUT0 | I/O  | Primary                                          | Bit 2 of port 3                                                      |  |  |  |  |

|                |                           | I/O  | Secondary                                        | If timer 0 is set to the compare-output or PWM modes, this pin is an |  |  |  |  |

|                |                           | 1/0  | Secondary                                        | output. If set to the capture mode, this pin is an input.            |  |  |  |  |

|                | P3.1                      | I/O  | _                                                | Bit 1 of port 3                                                      |  |  |  |  |

|                | P3.0                      | 1/0  | _                                                | Bit 0 of port 3                                                      |  |  |  |  |

|                | 1 3.0                     | 1/0  | Primary                                          | Bit 7 of port 4                                                      |  |  |  |  |

|                | P4.7/SOUT                 | 0    | Secondary                                        | Serial data output pin for UART serial port                          |  |  |  |  |

|                |                           | 1/0  | Primary                                          | Bit 6 of port 4                                                      |  |  |  |  |

|                | P4.6/SIN                  | 1/0  | Secondary                                        | Serial data input pin for UART serial port                           |  |  |  |  |

|                |                           | 1/0  | Primary                                          | Bit 5 of port 4                                                      |  |  |  |  |

|                | P4.5/TXD                  | 0    | Secondary                                        | Transmit data output pin for UART/synchronous serial port            |  |  |  |  |

|                |                           | 1/0  | Primary                                          | Bit 4 of port 4                                                      |  |  |  |  |

|                | P4.4/RXD                  | 1/0  | Secondary                                        | Receive data input pin for UART/synchronous serial port              |  |  |  |  |

|                |                           |      | Primary                                          | Bit 3 of port 4                                                      |  |  |  |  |

|                | P4.3/TXC                  | I/O  | Secondary                                        | Transmit clock I/O pin for UART/synchronous serial port              |  |  |  |  |

|                |                           |      | Primary                                          | Bit 2 of port 4                                                      |  |  |  |  |

|                | P4.2/RXC                  | I/O  | Secondary                                        | Receive clock I/O pin for UART/synchronous serial port               |  |  |  |  |

|                | P4.1                      | I/O  |                                                  | Bit 1 of port 4                                                      |  |  |  |  |

|                | P4.0                      | I/O  | _                                                | Bit 0 of port 4                                                      |  |  |  |  |

|                |                           | ., 0 | 1                                                | =: 0 0: port                                                         |  |  |  |  |

## PIN DESCRIPTION (3)

| Classification    | Pin Name           | I/O | Function                | Description                                                                                                                                                                    |  |

|-------------------|--------------------|-----|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                   |                    | I/O | Primary                 | Bit 7 of port 5                                                                                                                                                                |  |

|                   | P5.7/DTR           | 0   | Secondary               | DTR signal output pin for UART serial port                                                                                                                                     |  |

|                   | D. D. O. (D. T. O. | I/O | Primary                 | Bit 6 of port 5                                                                                                                                                                |  |

|                   | P5.6/RTS           | 0   | Secondary               | RTS signal output pin for UART serial port                                                                                                                                     |  |

|                   |                    | I/O | Primary                 | Bit 5 of port 5                                                                                                                                                                |  |

|                   | P5.5/CTS           | 1   | Secondary               | CTS signal input pin for UART serial port                                                                                                                                      |  |

|                   |                    | I/O | Primary Bit 4 of port 5 |                                                                                                                                                                                |  |

|                   | P5.4/DSR           | I   | Secondary               | DSR signal input pin for UART serial port                                                                                                                                      |  |

|                   | D. T. O. (D. O.D.  | I/O | Primary                 | Bit 3 of port 5                                                                                                                                                                |  |

|                   | P5.3/DCD           | ı   | Secondary               | DCD signal input pin for UART serial port                                                                                                                                      |  |

|                   | DE O/DI            | I/O | Primary                 | Bit 2 of port 5                                                                                                                                                                |  |

|                   | P5.2/RI            | -   | Secondary               | RI signal input pin for UART serial port                                                                                                                                       |  |

|                   | DE MOUTA           | I/O | Primary                 | Bit 1 of port 5                                                                                                                                                                |  |

|                   | P5.1/OUT1          | 0   | Secondary               | OUT1 signal output pin for UART serial port                                                                                                                                    |  |

|                   | DE O/OLITO         | I/O | Primary                 | Bit 0 of port 5                                                                                                                                                                |  |

|                   | P5.0/OUT2          | 0   | Secondary               | OUT2 signal output pin for UART serial port                                                                                                                                    |  |

|                   | D0 7/ D4 0//       | I/O | Primary                 | Bit 7 of port 6                                                                                                                                                                |  |

|                   | P6.7/nBACK         | 0   | Secondary               | Bus release request acknowledged signal output pin                                                                                                                             |  |

| 1/0 D 1           | D0 0/ DDE0         | I/O | Primary                 | Bit 6 of port 6                                                                                                                                                                |  |

| I/O Ports         | P6.6/nBREQ         |     | Secondary               | Bus release request signal input pin                                                                                                                                           |  |

|                   | D0 5/D4 01/4       | I/O | Primary                 | Bit 5 of port 6                                                                                                                                                                |  |

|                   | P6.5/DACK1         | 0   | Secondary               | Data transfer request 1 acknowledged signal output pin                                                                                                                         |  |

|                   | D0 4/D4 01/0       | I/O | Primary                 | Bit 4 of port 6                                                                                                                                                                |  |

|                   | P6.4/DACK0         | 0   | Secondary               | Data transfer request 0 acknowledged signal output pin                                                                                                                         |  |

|                   | D0.0/DDE04         | I/O | Primary                 | Bit 3 of port 6                                                                                                                                                                |  |

|                   | P6.3/nDREQ1        |     | Secondary               | Data transfer request 1 signal input pin                                                                                                                                       |  |

|                   | P6.2/nDREQ0        | I/O | Primary                 | Bit 2 of port 6                                                                                                                                                                |  |

|                   |                    |     | Secondary               | Data transfer request 0 signal input pin                                                                                                                                       |  |

|                   | P6.1               | I/O |                         | Bit 1 of port 6                                                                                                                                                                |  |

|                   | P6.0               | I/O | _                       | Bit 0 of port 6                                                                                                                                                                |  |

|                   | P7.7               | I/O | _                       | Bit 7 of port 7                                                                                                                                                                |  |

|                   | P7.6               | I/O | _                       | Bit 6 of port 7                                                                                                                                                                |  |

|                   | P7.5               | I/O | _                       | Bit 5 of port 7                                                                                                                                                                |  |

|                   | P7.4               | I/O | _                       | Bit 4 of port 7                                                                                                                                                                |  |

|                   | P7.3               | I/O | _                       | Bit 3 of port 7                                                                                                                                                                |  |

|                   | P7.2               | I/O | _                       | Bit 2 of port 7                                                                                                                                                                |  |

|                   | P7.1               | I/O | _                       | Bit 1 of port 7                                                                                                                                                                |  |

|                   | P7.0               | I/O | _                       | Bit 0 of port 7                                                                                                                                                                |  |

| USB Port          | D+                 | I/O | _                       | LICE data I/O nina                                                                                                                                                             |  |

|                   | D-                 | I/O | _                       | USB data I/O pins                                                                                                                                                              |  |

|                   | TCK                | ı   | _                       | Test clock input pin                                                                                                                                                           |  |

| Dahaa             | TMS                | ı   | _                       | Test mode select pin                                                                                                                                                           |  |

| Debug             | TDI                | ı   | _                       | Test data input pin                                                                                                                                                            |  |

| Interface         | TDO                | 0   | _                       | Test data output pin                                                                                                                                                           |  |

|                   | nTRST              | ı   | _                       | Boundary scan logic reset input pin                                                                                                                                            |  |

| Interrupt         | nEFIQ              | ı   | _                       | External FIQ (high-speed interrupt) interrupt request signal input pin                                                                                                         |  |

| -                 | nEA                | I   | _                       | Normally connected to ground                                                                                                                                                   |  |

|                   | nRST               | -   | _                       | System reset signal input pin for this LSI device                                                                                                                              |  |

| System<br>Control | DBSEL              | ı   | _                       | During a system reset of this LSI device, this pin sets the bank 0 data bus width. To set a 16-bit bus width, connect to $V_{DD}$ . To set an 8-bit bus width, connect to GND. |  |

|                   | TEST               | 1   | _                       | This pin sets the test and debug modes for this LSI device. Normally connected to GND.                                                                                         |  |

| Power Supply      | $V_{DD}$           | l   | _                       | Power supply pin. Connect all V <sub>DD</sub> pins to the power supply.                                                                                                        |  |

|                   | $V_{SS}$           | I   |                         | Ground pin. Connect all V <sub>SS</sub> pins to GND.                                                                                                                           |  |

#### **OVERVIEW OF INTERNAL PERIPHERAL FUNCTIONS**

#### I/O Ports

The 64 I/O ports are configured from the 8-bit ports P0 to P7. Each bit of each port can be specified as an input or output. If specified as an input, the port becomes a high impedance input. In addition to their port function (primary function), some ports are assigned secondary functions such as an external interface function or an I/O pin for an internal peripheral.

#### **Timers**

The timers consist of a 2-channel 16-bit flexible timer and a 2-channel 16-bit general-purpose timer. A count clock can be selected for each channel.

- Flexible timer

Operating modes: auto-reload timer, compare-output, PWM, capture

General-purpose timer

Auto-reload timer

- Synchronous timer operation

Timer channel can be started and stopped in union.

Count clock

A count clock can be selected for each timer as: 1/1, 1/2, 1/4, 1/8, 1/16, and 1/32 of the system clock, or as an external clock.

#### **Time Base Generator**

The time base generator consists of the time base counter, which drives frequency dividers deriving the time base signals for on-chip peripherals from the system clock signals, and a watchdog timer, which counts time base clock cycles and produces a system reset signal when its internal counter overflows.

#### **UART Serial Port**

Functionally the same as the 16550A, the UART serial port is equipped with 16-byte FIFOs for both receive and transmit, modem control signals, a dedicated baud rate generator, etc.

- Full duplex operation

- Independent controls for transmit, receive, line status and data set interrupt

- Modem control signals: CTS, DSR, DCD, DTR, RTS and RI

- Built-in dedicated baud rate generator

- Data length: 5, 6, 7, or 8 bits

- Stop bit: 1, 1.5, or 2 bits

- Parity: odd, even, or none

- Detection of receive errors: parity error, framing error, overrun error, or data error of break interrupt

#### **UART/Synchronous Serial Port**

The UART/synchronous serial port is a serial port that operates in two communication modes, the UART mode and synchronous mode. In the UART mode, characters units are synchronized according to the controlled start bit and stop bit, and data is transferred. In the synchronous mode, the data transfer is synchronized to the controlled shift clock.

- Built-in dedicated baud rate generator

- Data length: 7 or 8 bits

- Stop bit: 1 or 2 bits (UART mode only)

- Parity: even or odd parity (none in the synchronous mode)

- Detection of receive errors: parity error, framing error, and overrun error (only overrun error in the synchronous mode)

- Full-duplex operation

#### **Interrupt Controller**

The interrupt controller manages interrupt requests from 9 external sources and 13 internal sources, and passes them on to the CPU as interrupt request (IRQ) or fast interrupt request (FIQ) exception requests. An interrupt level can be set for each interrupt and priority can be controlled.

- Supports 9 external interrupt sources from nEFIQ and nEIR [7:0] pins and 13 internal interrupt sources from internal peripherals such as the USB device controller and the timers.

- To simplify the control of interrupt priority, 8 interrupt levels can be set for each interrupt source.

- The interrupt controller assigns a unique interrupt number to each interrupt source to permit rapid branching to the appropriate routine.

#### **Direct Memory Access (DMA) Controller**

The direct memory access (DMA) controller is used instead of the CPU to transfer data between internal memory, internal peripherals, external memory and memory mapped external devices.

- Built-in 2 channels

- Supports 64MB address area

- Transfer data size: 8 or 16 bits - Maximum transferring: 65536 times

- Addressing modes: single or dual address mode

Bus modes: cycle-steal or burst mode

- Supports transfer requests from nDREQ[0:1] pins, internal peripheral devices and software.

- Generates transfer complete interrupt requests when transfer is completed.

#### Universal Serial Bus (USB) Device Controller

The USB device controller consists of a protocol engine to control the USB communications protocol, DPLL, status/control, FIFO control, a USB transceiver, etc. The USB device controller conforms to USB spec. 1.1 full-speed (12Mbps).

- Supports the 4 types of transfers that are specified by the USB standard. (control transfer, bulk transfer, isochronous transfer, and interrupt transfer)

- Remote wakeup function

- Adaptable to USB bus powered devices

- 4 endpoint addresses

**Endpoint FIFO contents and functions**

| Endpoint | FIFO contents |                        | Transfer mode                |

|----------|---------------|------------------------|------------------------------|

| EP0      | 64 bytes      | × 1 (transmit)         | Control                      |

|          | 64 bytes      | × 1 (receive)          | Control                      |

| EP1      | 64 bytes      | × 1 (transmit-receive) | Bulk, interrupt              |

| EP2      | 64 bytes      | × 2 (transmit-receive) | Bulk, interrupt, isochronous |

| EP3      | 256 bytes     | × 2 (transmit-receive) | Bulk, interrupt, isochronous |

#### **External Memory Controller**

The external memory controller generates control signals for accessing external memory (ROM, RAM, DRAM, etc.) and peripheral devices mapped in the external memory space, and arbitrates external bus requests from external devices.

- Manages memory by dividing the memory space into 4 banks

- 2 banks of ROM, SRAM, and I/O

- 2 banks of DRAM

- Each bank has a 16MB address space.

- Bus width (8 or 16 bits) and wait cycles can be specified for each bank.

- ROM, SRAM and I/O can be connected directly.

Outputs a strobe signal for the ROM, SRAM and I/O.

- DRAM can be connected directly.

- Row and column addresses are output as multiplexed signals.

- Random access mode or high-speed page mode

- Supports CAS before RAS refresh and self-refresh.

#### **Clock Control**

The clock controller generates and controls the system clock based on the internal oscillator circuit and phase locked loop (PLL). It also controls the transitions to and from standby modes (HALT and STOP modes) and returns to normal operation of mode.

- It offers a choice of divider ratio for adjusting operating clock frequency to match the load processing.

When using PLL:  $2 \times f$ , f, f/2 Not using PLL: f, f/2, f/4, f/8

f = input clock frequency

### **ABSOLUTE MAXIMUM RATINGS**

| Parameter           | Symbol           | Condition          | Rated value                  | Unit |

|---------------------|------------------|--------------------|------------------------------|------|

| Supply voltage      | $V_{DD}$         | M                  | -0.3 to +4.6                 | W    |

| Input voltage       | V <sub>IN</sub>  | $V_{DD}$ GND = 0 V | -0.3 to V <sub>DD</sub> +0.3 | V    |

| Output current      | Io               | Ta = 25°C          | 12                           | mA   |

| Power dissipation   | $P_{D}$          | 1a - 25 C          | 1                            | W    |

| Storage temperature | T <sub>STG</sub> | _                  | -55 to +150                  | °C   |

### RECOMMENDED OPERATING CONDITIONS

(GND = 0 V)

| Parameter               | Symbol         | Condition                      | Min. | Тур. | Max. | Unit |

|-------------------------|----------------|--------------------------------|------|------|------|------|

| Supply voltage          | $V_{DD}$       |                                | 3.0  | 3.3  | 3.6  | \/   |

| Storage holding voltage | $V_{DDH}$      | $f_C = 0 Hz$                   | 2.0  | _    | 3.6  | V    |

| Operating frequency     | f <sub>C</sub> | $V_{DD} = 3.0 \text{ to } 3.6$ | 4    | _    | 24   | MHz  |

| Ambient temperature     | Та             | _                              | -10  | 25   | +70  | °C   |

## Input Clock Conditions

Connecting a crystal oscillator

| PLLEN Pin | Input frequency | Operating frequency (f <sub>c</sub> ) |

|-----------|-----------------|---------------------------------------|

| "H" Level | 6 to 12 MHz     | 12 to 24 MHz                          |

| "L" Level | 4 to 12 MHz     | 4 to 12 MHz                           |

Using an external clock supply

| PLLEN Pin | Input frequency | Operating frequency (f <sub>C</sub> ) |

|-----------|-----------------|---------------------------------------|

| "H" Level | 6 to 12 MHz     | 12 to 24 MHz                          |

| "L" Level | 4 to 48 MHz     | 4 to 24 MHz                           |

### **ELECTRICAL CHARACTERISTICS**

### DC Characteristics (1)

| De characteristics (1)                 |                  | (                                                       | $V_{DD} = 3.0 \text{ to } 3.$ | 6 V GND = 1 | 0 V Ta= _10          | to +70°C) |

|----------------------------------------|------------------|---------------------------------------------------------|-------------------------------|-------------|----------------------|-----------|

| Parameter                              | Symbol           | Condition                                               | Min.                          | Typ. (*1)   | Max.                 | Unit      |

| H-level input voltage 1                | V <sub>IH1</sub> | _                                                       | $0.76 \times V_{DD}$          | _           | 5.5                  |           |

| H-level input voltage 2, 3             | $V_{IH2}$        | _                                                       | $0.76 \times V_{DD}$          |             | V <sub>DD</sub> +0.3 |           |

| H-level input voltage 4                | $V_{IH3}$        | _                                                       | 2.0                           |             | 5.5                  |           |

| L-level input voltage 1, 2, 3          | $V_{IL1}$        |                                                         | -0.3                          |             | $0.2 \times V_{DD}$  | V         |

| L-level input voltage 4                | $V_{IL2}$        | _                                                       | -0.3                          |             | 0.8                  | V         |

| H-level output voltage                 | V <sub>OH</sub>  | $I_{OH} = -4 \text{ mA}$<br>$I_{OH} = -100 \mu\text{A}$ | 2.2<br>V <sub>DD</sub> -0.2   |             | _                    |           |

| L-level output voltage                 | V <sub>OL</sub>  | I <sub>OL</sub> = 4 mA                                  | _                             | _           | 0.4                  |           |

| Input leakage current                  | I <sub>LI</sub>  | $V_1 = 0/V_{DD}$                                        | _                             | -           | 1.0 (*2)             |           |

| Output leakage current                 | I <sub>LO</sub>  | $V_{O} = 0/V_{DD}$                                      | _                             | _           | 1.0 (*2)             |           |

| H-level input current 3                | I <sub>IH</sub>  | $V_{l} = V_{DD}$<br>Pull-down resistor<br>$50k\Omega$   | 20                            | 66          | 200                  | μА        |

| L-level input current 2                | I <sub>IL</sub>  | $V_1 = 0 \text{ V}$ Pull-up resistor $50k\Omega$        | -200                          | -60         | -20                  |           |

| Input pin capacitance                  | Cı               | _                                                       | _                             | 6           | _                    | _         |

| Output pin capacitance                 | Co               | <u> </u>                                                | _                             | 9           | _                    | pF        |

| I/O pin capacitance                    | C <sub>IO</sub>  | <u> </u>                                                | _                             | 10          | _                    |           |

| Current consumption                    | I <sub>DDS</sub> | (*3)                                                    | _                             | 3           | 150                  | μА        |

| (in STOP mode)                         | 'DDS             | (*4)                                                    | _                             | 20          | 500                  | μΑ        |

| Current consumption (in HALT mode)     | I <sub>DDH</sub> | f <sub>C</sub> = 24 MHz                                 | _                             | 35          | 50                   | mA        |

| Current consumption (during operation) | I <sub>DD</sub>  | No load                                                 | _                             | 70          | 105                  | IIIA      |

- 1. Applied to PIO7 to PIO0, nEFIQ, nEA, DBSEL, TEST, and PLLEN

- 2. Applied to nRST, TDI, TMS, and TCK

- 3. Applied to nTRST

- 4. Applied to XD0 to XD15

- (\*1): Typ. indicates values for the case where  $V_{DD} = 3.3 \text{ V}$  and  $Ta = 25^{\circ}\text{C}$ .

- (\*2): 50  $\mu$ A when Ta is 50°C or above.

- (\*3): Ta = -10 to  $+50^{\circ}$ C

- (\*4): Ta = +50 to +70°C

## DC Characteristics (2) USB Port (D+, D-)

$(V_{DD} = 3.0 \text{ to } 3.6 \text{ V}, \text{ GND} = 0 \text{ V}, \text{ Ta} = 0 \text{ to } +70^{\circ}\text{C})$

| Parameter                       | Symbol          | Condition                              | Min. | Typ. (*1) | Max. | Unit |

|---------------------------------|-----------------|----------------------------------------|------|-----------|------|------|

| Differential input sensitivity  | VDI             | {(D+)-(D-)}                            | 0.2  |           | _    |      |

| Differential common mode range  | VCM             | Including VDI part                     | 0.8  |           | 2.5  | .,   |

| Single ended receiver threshold | VSE             |                                        | 8.0  |           | 2.0  | V    |

| H-level output voltage          | $V_{OH}$        | 15kΩ to GND                            | 2.8  |           | 3.6  |      |

| L-level output voltage          | $V_{OL}$        | 15kΩ to 3.6 V                          | _    |           | 0.3  |      |

| Output leakage current          | I <sub>LO</sub> | 0 V <v<sub>IN<v<sub>DD</v<sub></v<sub> | -10  | _         | +10  | μА   |

(\*1): Typ. indicates values for the case where  $V_{\text{DD}}$  = 3.3 V and Ta = 25°C.

### **AC Characteristics**

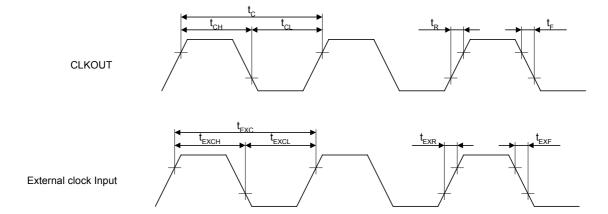

Clock timing

$(V_{DD} = 3.0 \text{ to } 3.6 \text{ V}, \text{ GND} = 0 \text{ V}, \text{ Ta} = -10 \text{ to } +70^{\circ}\text{C})$

| Parameter                                | Symbol                                | Condition                                | Min. | Тур. | Max. | Unit |

|------------------------------------------|---------------------------------------|------------------------------------------|------|------|------|------|

| Clock frequency                          | $f_{C}$                               |                                          | 4    | _    | 24   | MHz  |

| Clock cycle time                         | t <sub>C</sub>                        |                                          | 42   | _    | 250  | ns   |

| Clock H-level pulse width                | t <sub>CH</sub>                       |                                          | 15   | _    | _    |      |

| Clock L-level pulse width                | $t_{\scriptscriptstyle{\mathrm{CL}}}$ |                                          | 15   | _    | _    |      |

| External clock input frequency           | $f_{\text{EXC}}$                      | $V_{DD} = 3.0 \text{ to } 3.6 \text{ V}$ | 4    | _    | 24   | MHz  |

| External clock input cycle time          | t <sub>EXC</sub>                      |                                          | 42   | _    | 250  | ns   |

| External clock input H-level pulse width | t <sub>EXCH</sub>                     |                                          | 15   | _    | _    |      |

| External clock input L-level pulse width | t <sub>EXCL</sub>                     |                                          | 15   | _    | _    |      |

| Clock rise time                          | t <sub>R</sub>                        | _                                        | _    | _    | 5    |      |

| Clock fall time                          | t <sub>F</sub>                        | _                                        | _    | _    | 5    |      |

| External clock input rise time           | t <sub>EXR</sub>                      | _                                        | _    | _    | 5    |      |

| External clock input fall time           | t <sub>EXF</sub>                      | _                                        | _    | _    | 5    |      |

15.2

OKI Semiconductor ML671000

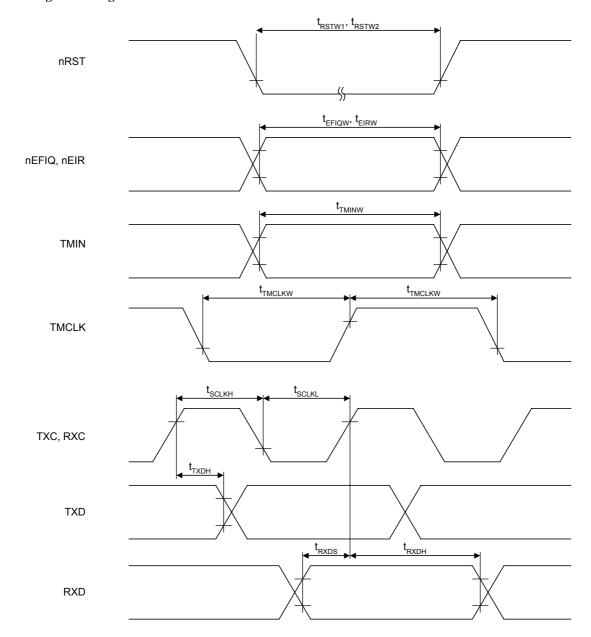

#### Control signal timing

|                              |                     |                        | $(V_{DD} = 3.0 \text{ to } 3.6 \text{ V}, \text{ GND} = 0 \text{ V}, \text{ Ta} = -10 \text{ to } +70^{\circ}\text{C})$ |      |                      |      |  |

|------------------------------|---------------------|------------------------|-------------------------------------------------------------------------------------------------------------------------|------|----------------------|------|--|

| Parameter                    | Symbol              | Condition              | Min.                                                                                                                    | Тур. | Max.                 | Unit |  |

| nRST pulse width (*1)        | t <sub>RSTW1</sub>  | _                      | 2 t <sub>C</sub>                                                                                                        | _    | _                    | ns   |  |

| nRST pulse width (*2)        | t <sub>RSTW2</sub>  | _                      | Oscillation stabilization time                                                                                          | _    | _                    | _    |  |

| nEFIQ pulse width            | t <sub>EFIQW</sub>  | _                      | 2 t <sub>C</sub>                                                                                                        | _    | _                    | ns   |  |

| nEIR pulse width             | t <sub>EIRW</sub>   | _                      | 2 t <sub>C</sub>                                                                                                        | _    | _                    |      |  |

| TMIN pulse width             | t <sub>TMINW</sub>  | _                      | 2 t <sub>C</sub>                                                                                                        | _    | _                    |      |  |

| TMCLK pulse width            | t <sub>TMCLKW</sub> | _                      | 2 t <sub>C</sub>                                                                                                        | _    | _                    |      |  |

| TCX, RXC frequency           | $f_{SC}$            | _                      | _                                                                                                                       | _    | 1/4 f <sub>C</sub>   | MHz  |  |

| TXC, RXC H-level pulse width | t <sub>sclkh</sub>  | _                      | 2 t <sub>C</sub>                                                                                                        | _    | _                    |      |  |

| TXC, RXC L-level pulse width | t <sub>sclkl</sub>  | _                      | 2 t <sub>C</sub>                                                                                                        | _    | _                    | Ī    |  |

| TXD delay time               | t <sub>TXD</sub>    | C <sub>L</sub> = 50 pF | _                                                                                                                       | _    | 1 t <sub>c</sub> +22 |      |  |

| RXD setup time               | t <sub>RXS</sub>    |                        | 0.5 t <sub>C</sub>                                                                                                      | _    |                      | ne   |  |

|                              |                     |                        |                                                                                                                         |      |                      | ns   |  |

$C_{L} = 50 \text{ pF}$

1.5 t<sub>C</sub>

1.0

2.6

2.4

(1\*): Not including when power is turned on and during STOP mode

$t_{RXH}$

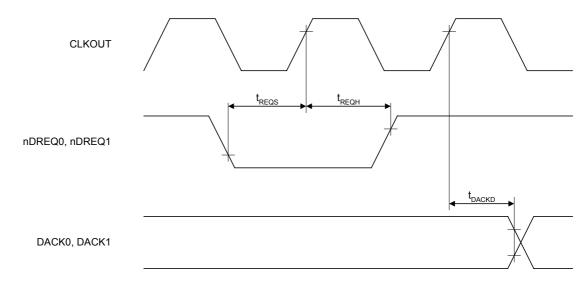

t<sub>REQS</sub>

$t_{\text{REQH}}$

t<sub>DACKD</sub>

(2\*): When power is turned on and also during STOP mode

### External bus timing

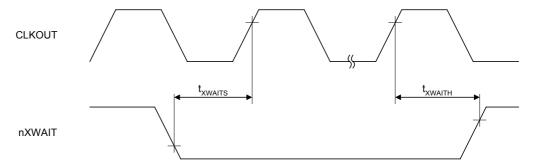

RXD hold time

nDREQ0, nDREQ1 setup time

nDREQ0, nDREQ1 hold time

DACK0, DACK1 delay time

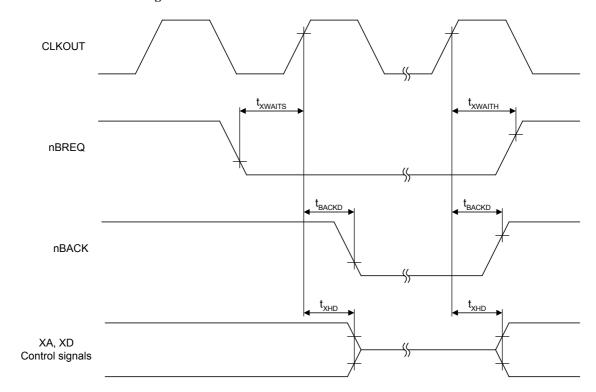

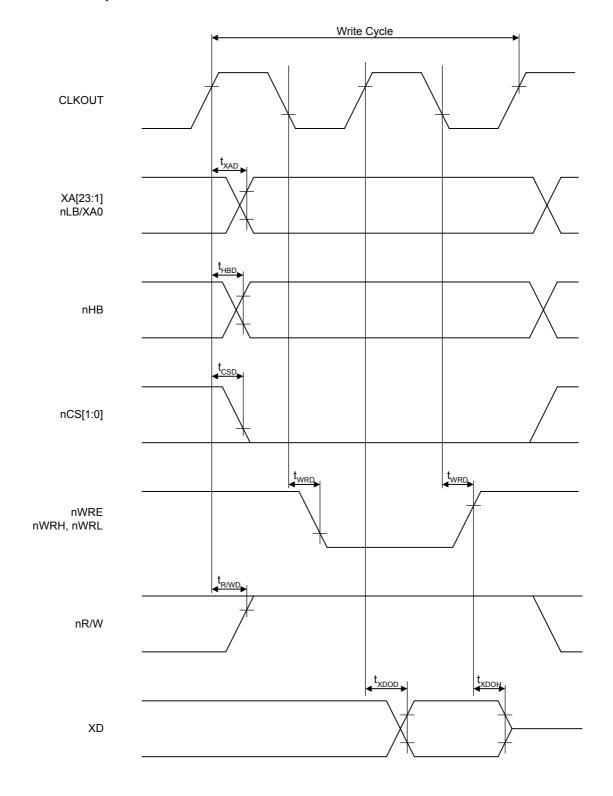

$(V_{DD} = 3.0 \text{ to } 3.6 \text{ V}, \text{ GND} = 0 \text{ V}, \text{ Ta} = -10 \text{ to } +70^{\circ}\text{C})$ Parameter Symbol Condition Min. Typ. Max. Unit XA[23:1], nLB/XA0 delay time 0 12  $t_{XAD}$ XD[15:0] output delay time 2 18  $t_{XDOD}$ XD[15:0] output hold time 9  $t_{XDOH}$ XD[15:0] input setup time 12 t<sub>XDIS</sub> XD[15:0] input hold time 0  $t_{XDIH}$ nXWAIT setup time 0 t<sub>xwaits</sub> nXWAIT hold time 0 t<sub>XWAITH</sub> 0 nHB delay time 9  $t_{HBD}$ 0 nCS[1:0] delay time 10  $t_{CSD}$  $C_{L} = 50 \text{ pF}$ nWRE, nWRH, nWRL delay time ns 0 9  $t_{WRD}$ nRD assert delay time 0 8  $t_{RDD}$ nR/W assert delay time 0 10  $t_{RWD}$ nRAS[1:0] assert delay time 1 10 t<sub>RASD</sub> nCAS assert delay time 1 10  $t_{CASD}$ nWE, nWH, nWL assert delay 1 12  $t_{\text{WED}}$ time nBREQ setup time  $t_{BREQS}$ 11 nBREQ hold time 0 t<sub>BREQH</sub> nBACK delay time 2 13 High impedance delay time 3 12  $t_{XHD}$

## TIMING DIAGRAMS

### **Clock Timing**

## **Control Signal Timing**

## $\overline{DMA}$ Timing

## **nXWAIT** Signal Input Timing

## **External Bus Release Timing**

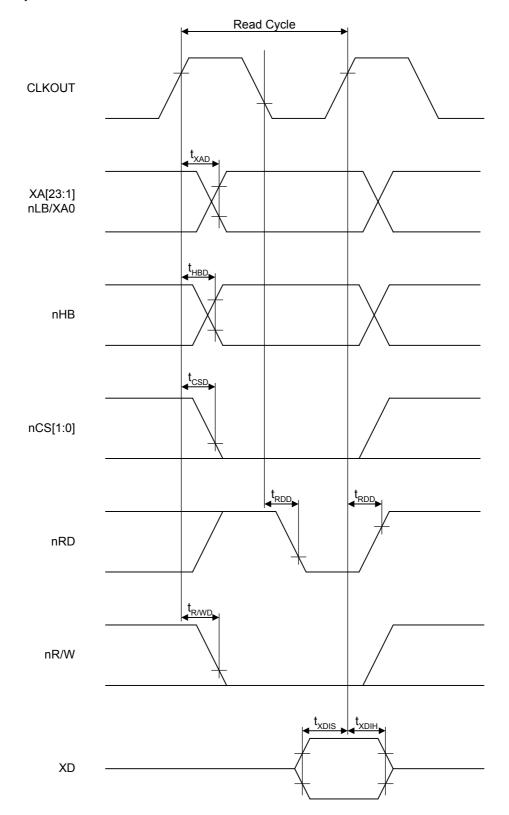

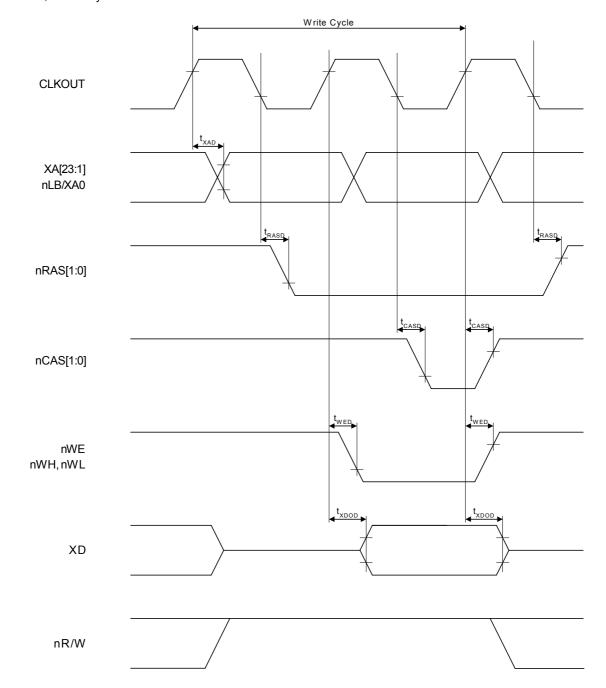

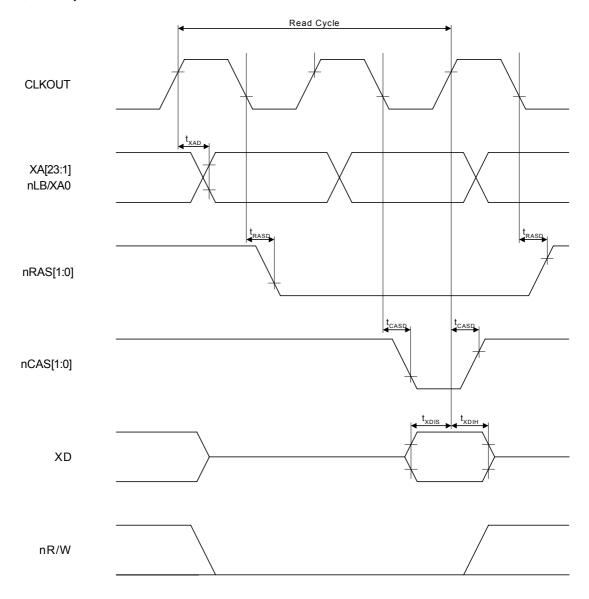

## **External Bus Timing**

Bank 0, 1 write cycle

Bank 0, 1 read cycle

Bank 2, 3 write cycle

Bank 2, 3 read cycle

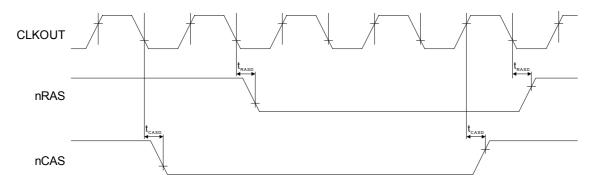

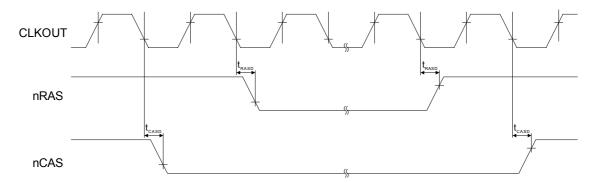

## CAS before RAS (CBR) refresh

## Self-refresh

#### **PACKAGE DIMENSIONS**

(Unit: mm)

Notes for Mounting the Surface Mount Type Package

The surface mount type packages are very susceptible to heat in reflow mounting and humidity absorbed in storage.

Therefore, before you perform reflow mounting, contact Oki's responsible sales person for the product name, package name, pin number, package code and desired mounting conditions (reflow method, temperature and times).

#### **NOTICE**

The information contained herein can change without notice owing to product and/or technical improvements. Before using the product, please make sure that the information being referred to is up-todate.

- 2. The outline of action and examples for application circuits described herein have been chosen as an explanation for the standard action and performance of the product. When planning to use the product, please ensure that the external conditions are reflected in the actual circuit, assembly, and program designs.

- 3. When designing your product, please use our product below the specified maximum ratings and within the specified operating ranges including, but not limited to, operating voltage, power dissipation, and operating temperature.

- 4. Oki assumes no responsibility or liability whatsoever for any failure or unusual or unexpected operation resulting from misuse, neglect, improper installation, repair, alteration or accident, improper handling, or unusual physical or electrical stress including, but not limited to, exposure to parameters beyond the specified maximum ratings or operation outside the specified operating range.

- 5. Neither indemnity against nor license of a third party's industrial and intellectual property right, etc. is granted by us in connection with the use of the product and/or the information and drawings contained herein. No responsibility is assumed by us for any infringement of a third party's right which may result from the use thereof.

- 6. The products listed in this document are intended for use in general electronics equipment for commercial applications (e.g., office automation, communication equipment, measurement equipment, consumer electronics, etc.). These products are not authorized for use in any system or application that requires special or enhanced quality and reliability characteristics nor in any system or application where the failure of such system or application may result in the loss or damage of property, or death or injury to humans. Such applications include, but are not limited to, traffic and automotive equipment, safety devices, aerospace equipment, nuclear power control, medical equipment, and life-support systems.

- 7. Certain products in this document may need government approval before they can be exported to particular countries. The purchaser assumes the responsibility of determining the legality of export of these products and will take appropriate and necessary steps at their own expense for these.

- 8. No part of the contents contained herein may be reprinted or reproduced without our prior permission.

Copyright 2001 Oki Electric Industry Co., Ltd.